基于FPGA的多路无线数据采集系统设计

李锦明,刘梦欣,成乃朋,成雅丽

(中北大学仪器与电子学院,山西 太原 030051)

0 引 言

随着工业、农业、医疗、仓储行业的不断发展,需要监测的数据对象逐渐增多[1]。数据采集是监测控制系统的关键部分,也是最为核心的部分,如何有效获取多路数据并进行可靠地存储传输成为关键的问题。

在实际应用中,数据的多路采集一般采用模拟多路复用器配合AD转换器实现[2-3],数据的可靠传输多采用串口、网口等有线传输方式实现。然而,对于煤矿、油井、海洋探测等特殊环境,有线传输已无法满足数据通信的需求。

针对数据采集系统存在的有线传输局限性问题,本文设计一种基于FPGA的多路无线数据采集系统,由FPGA控制模拟多路复用器与AD转换器实现多路数据采集并完成数据的编帧处理,将处理后的数据存入Flash中,防止数据丢失,采用ZigBee无线通信技术实现采集数据的无线传输[4-5]。

1 系统总体设计

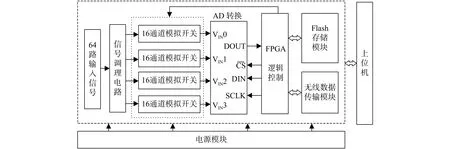

本系统设计的无线传感网络节点电路主要由FPGA主控模块、AD转换电路、Flash存储模块、无线数据传输模块、电源管理模块等组成。系统总体设计框图如图1所示,以FPGA为控制单元,模拟多路复用器配合AD转换器完成64路模拟信号的采样量化,FPGA对数据进行FIFO缓存和编帧操作,通过控制Flash模块完成多路数据的存储,由无线数据传输模块实现数据的无线传输。

本设计以采集64路模拟信号为例,系统的工作过程如下:上位机发送有效指令,命令系统开始工作,该指令由无线数据传输模块接收后发送至FPGA,FPGA通过对模拟开关相应地址的选通信号及AD转换器片选信号的控制,将调理电路处理后的多路待采样信号由AD模块转换成数字信号并传输给FPGA,FPGA对采样量化后的数据进行编帧处理后存入写FIFO中,待写FIFO半满标志有效,将数据传输至Flash存储模块。当读数据信号有效,则在FPGA控制下将数据读出至读FIFO中并发送给无线数据传输模块进行传输,最后由上位机软件对数据进行处理和显示。

2 系统硬件电路设计

2.1 数据采集模块设计

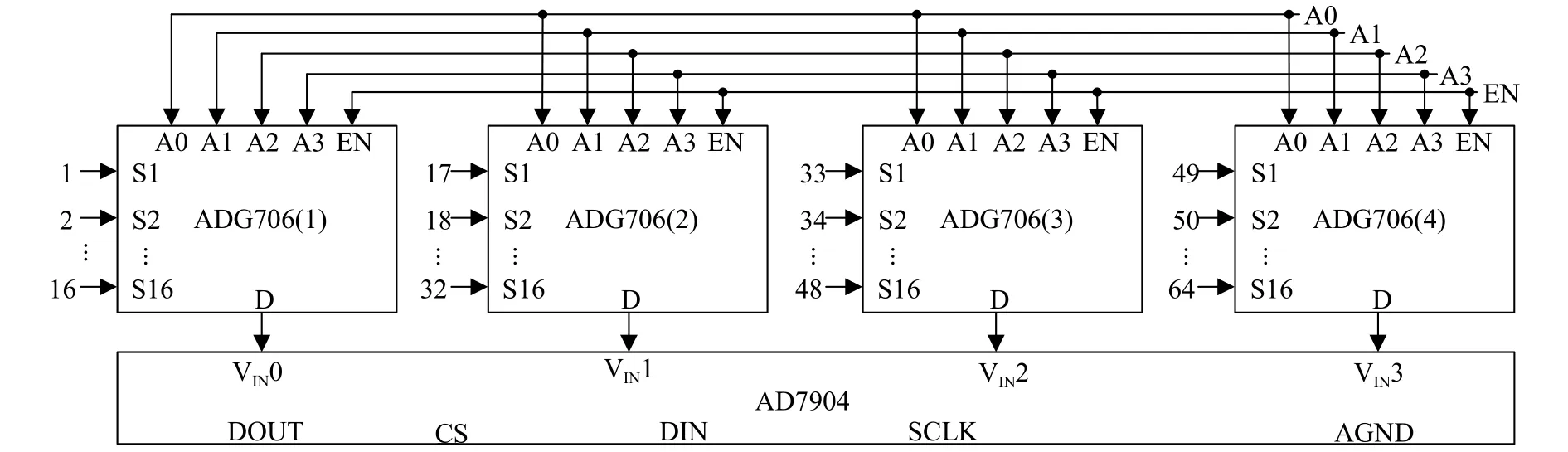

数据采集模块由模拟开关及AD转换器组成,选用4片16通道模拟多路复用器ADG706,负责实现64路模拟信号地址切换,该芯片导通电阻小、切换速度快、切换时间仅为40 ns,符合AD7904的1 MS/s采样要求,能够满足系统设计需要。AD芯片选用4通道的AD7904,该器件采样率可达1 MS/s,采样位数为8 bit,具有体积小、功耗低等优点。

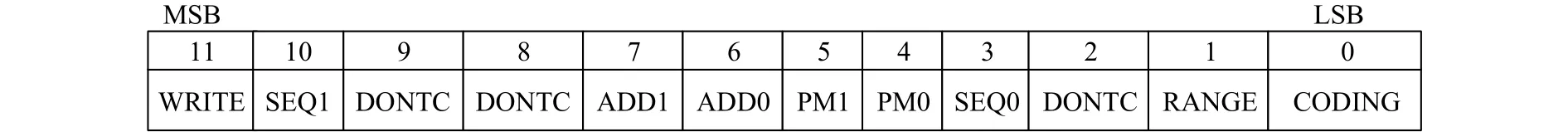

图2为AD7904控制寄存器位功能图,通过配置控制寄存器将AD7904设置为二进制编码格式,4通道循环采集,采集电压范围为0~2.5 V。

图1 系统总体设计框图

图2 AD7904控制寄存器位功能图

如图3所示,AD7904的4个输入通道分别与4片ADG706的输出端相连,通过FPGA控制A3-A0实现模拟开关地址的选通。系统正常工作时,FPGA通过对AD7904的芯片设定及ADG706的地址切换控制,使其完成对应地址下信号调理电路输出电压信号的循环采集,经AD转换后送至FPGA进行编帧处理。

2.2 Flash存储模块设计

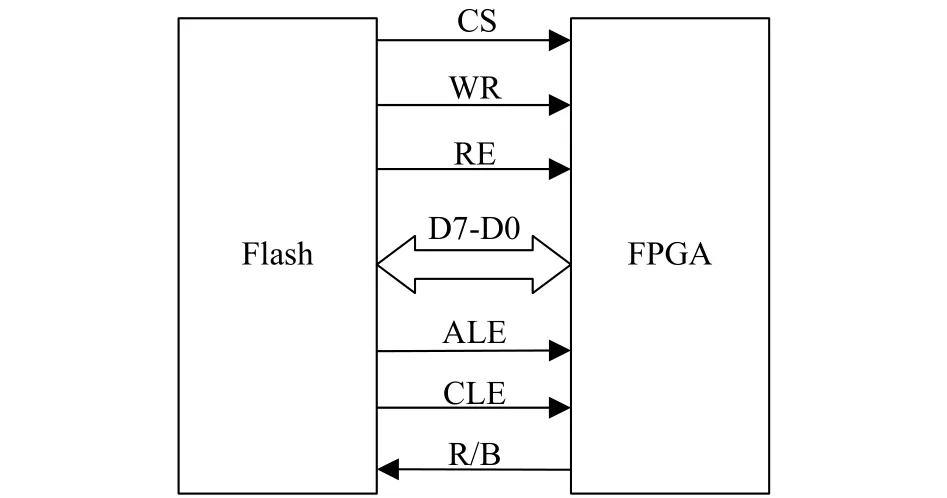

由于FPGA内部FIFO资源有限,对于长时间、大数据量的存储无法保证数据存储的可靠性,故而在该系统中先将数据存储至大容量Flash中,待系统收到有效的读数据信号,再将数据读取至FIFO中进行无线传输。FPGA与Flash的连接电路如图4所示。

2.3 无线数据传输模块设计

近年来,无线通信技术发展迅速,常用的短距离无线通信技术包括红外通信技术(IrDA)、蓝牙通信技术(Bluetooth)、WiFi通信技术和ZigBee通信技术[6]。

图3 ADG706与AD7904电路连接图

图4 Flash与FPGA的电路连接图

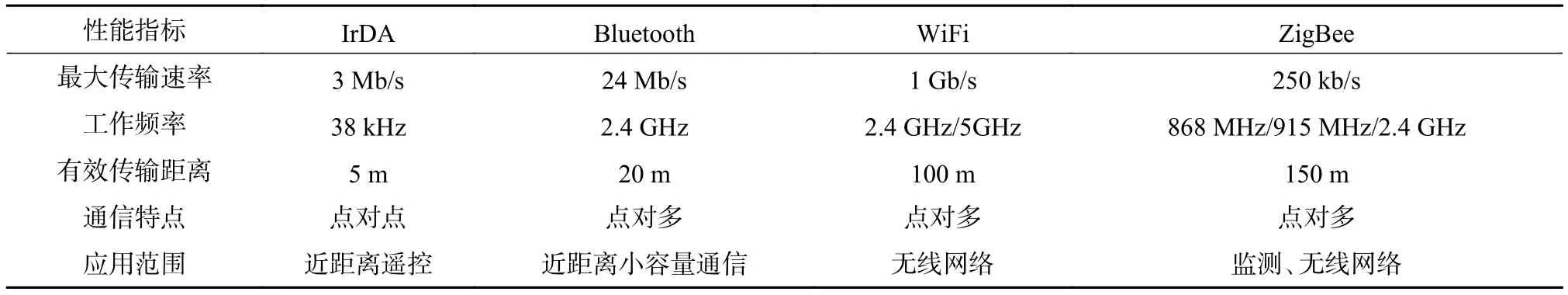

通过表1对短距离无线通信技术参数及特点进行比较,可发现WiFi通信技术与ZigBee通信技术都可实现本系统的无线传输模块,但考虑到Wi-Fi通信技术抗干扰能力弱,且WiFi功耗高,故而本设计采用功耗低、时延短、容量大且安全性能高的ZigBee通信技术来实现无线数据传输。

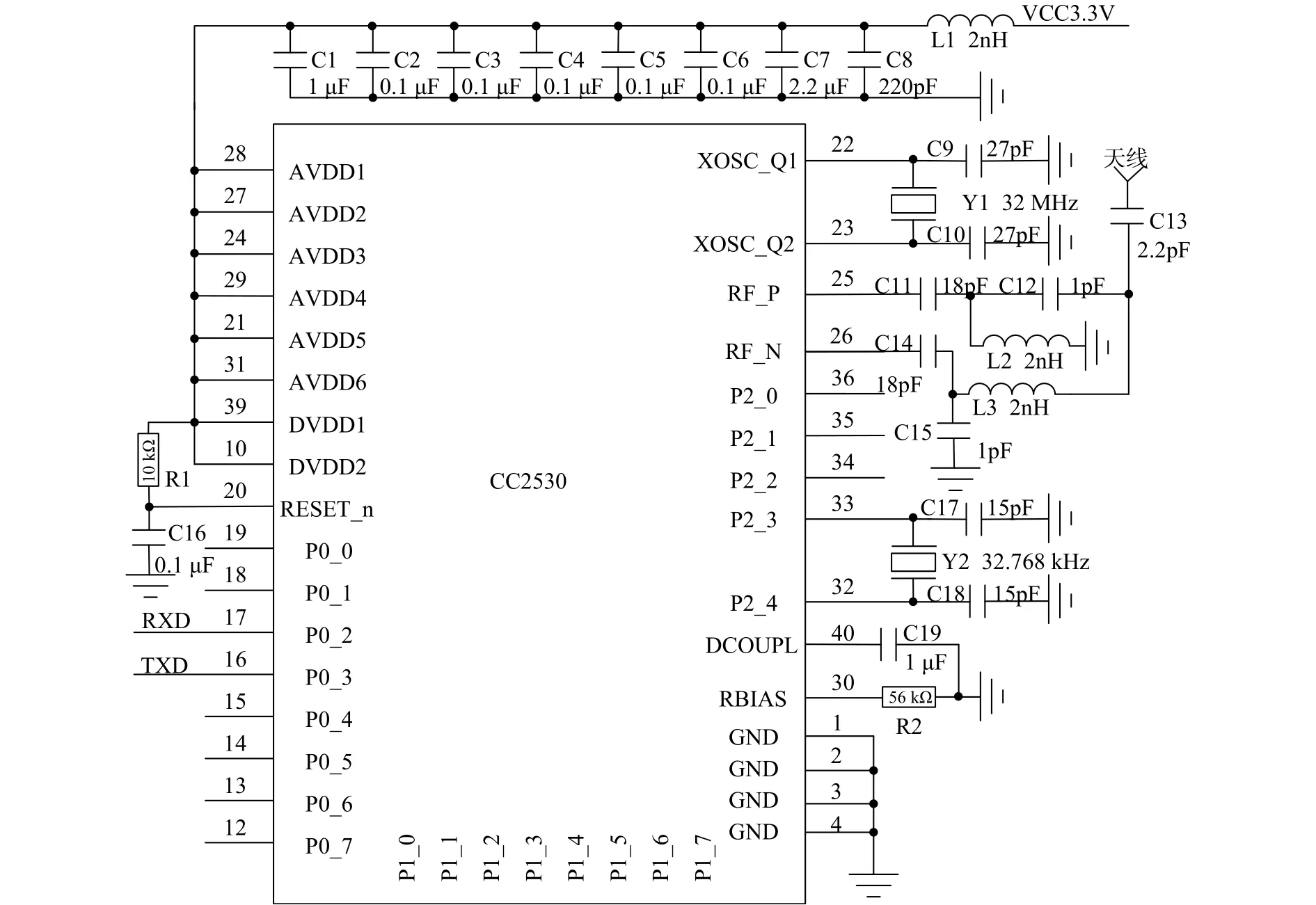

无线数据传输网络主要包括终端节点设备、路由器设备及协调器设备,数据由终端节点设备进行发送,路由器设备进行中继转发,协调器设备传输至上位机,三者协调工作实现无线数据传递。采用CC2530作为ZigBee无线通信的构成芯片,该片上系统兼容IEEE 802.15.4,支持ZigBee、ZigBee PRO和ZigBeeRF4CE标准,且功耗低、抗干扰能力强,可通过Z-stack协议栈[7]完成芯片的配置与组网操作[8]。ZigBee协议具有更好的交互操作性、节点密度管理、支持网状网络、低功耗且具有较高的安全可靠性,使得节点通信距离更远,组网性能稳定[9-10]。该ZigBee模块通过串口完成与FPGA的数据交互,通过配置,将其设置为终端节点数据发送模式[11-12],通过与FPGA的硬件连接组成无线数据传输模块,如图5所示。

在无线数据发送过程中,为保证ZigBee网络数据传输的准确性,降低系统误码率,采用蛇形天线进行信号发射[13]。

3 系统软件设计

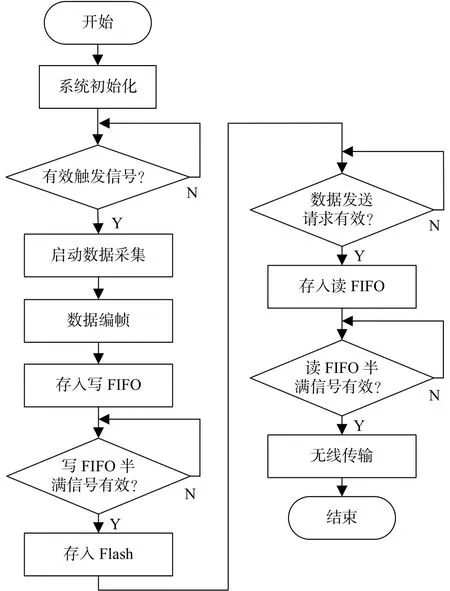

系统软件设计流程如图6所示,其中系统初始化主要完成AD控制寄存器配置、FPGA初始化等操作。具体工作过程如下:系统开始工作,FPGA完成AD7904内部控制寄存器数据参数配置后进入等待触发状态。当系统接收到有效触发信号,开始启动数据采集,通过FPGA控制ADG706确定传送给AD转换器的通道电压信号。而后,对采集数据进行编帧处理,并暂存于FPGA写FIFO中,待写FIFO半满信号有效将数据传输至Flash。当系统收到有效数据发送请求时,将Flash中数据读取至读FIFO中,并由无线传输模块进行传输。

4 系统测试结果及分析

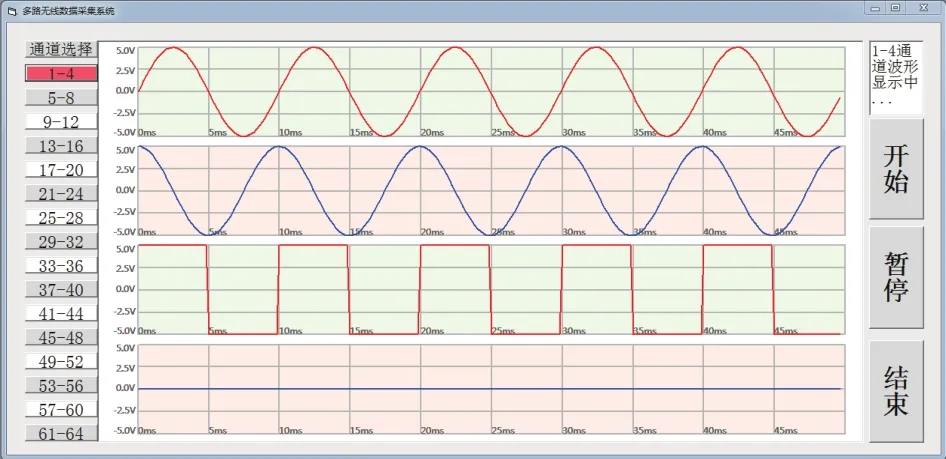

为了测试系统的有效性和稳定性,FPGA芯片选用Xilinx公司生产的Spantan-6系列XC6SLX25-2FTG256C芯片,该器件内部集成24 051个逻辑单元,拥有936 kb的块RAM与186个用户定义I/O口。由信号发生器产生三路不同的信号,分别为正弦信号、方波信号和余弦信号,波形周期均为10 ms,幅值为5 V,其他通道均为0 V电压信号,用于检测系统传输的稳定性和可靠性。

表1 常用短距离无线通信技术参数及特点

图5 无线数据发送模块

图6 系统软件设计流程图

图7为上位机软件对接收数据进行处理得到的相应波形显示。观察可得,测试信号经采集、存储及无线传输后还原的信号波形稳定,无毛刺,波形周期为9.8 ms,幅值为5 V,与信号发生器产生的待采集信号一致,且接收到的0 V电压信号波形无纹波与毛刺,表明该系统传输稳定、性能可靠,可实现预定的采集、存储及无线传输功能。

图7 上位机波形显示

在具体的工程实践应用中为增大系统的抗干扰能力,可在数据进行无线传输前进行信道编码处理,进一步保证系统的可靠性和稳定性。

5 结束语

本文通过FPGA与ZigBee的结合使用,实现多因素复杂区域的数据采集及无线传输。无线数据采集系统通过对三种不同波形信号的采集,验证了系统功能的有效性和稳定性。系统体积小、功能模块化,可根据测量环境选择不同的模拟多路复用器并更改相关的控制程序,完成特定路数的数据采集,对于较远距离的无线采集,可增加中继器的个数来实现。