Xilinx FPGA高速资源合理利用的一种思路

杨见 陈伟 许杰 陈少林

(1.四川九洲空管科技有限责任公司 四川省绵阳市 621000 2.空装驻绵阳地区某军事代表室 四川省绵阳市 621000)

随 着CML(CurrentModeLogic)、CDR、8b10b 编码/64b66b编码技术、预加重/去加重、时钟补偿等技术的出现,能够极大地减小时钟抖动、收发时钟频偏、信号衰减和线路噪声对接收性能的影响,从而使高速串行传输方式得到极为广泛的应用,而其接口信号线数量少、应用成本低等优点,更是让开发人员相比并行数据传输接口而言,更愿意选择高速串行传输方式。Xilinx FPGA 集成了可实现不同线速率的高速串行收发器硬核资源,开发人员只需要进行简单的配置即可实现高速串行应用。基于成本考虑,在工程应用中,开发人员依然遵循通过调用尽量少的资源去完成足够多的功能这一准则展开设计。本文就针对这一点对Xilinx FPGA 高速串行资源的利用提出一种设计思路进行分析并验证。

1 设计需求

QUAD116 搭建4 条常规的10G 高速链路与目标设备三通信,QUAD115 搭建3 条10G 高速链路与目标设备二通信,以及一条千兆网链路与目标设备一通信。

链路设计要求如图1 所示。

2 设计思路

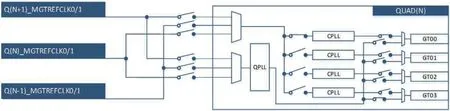

Xilinx 7 系列GTX 每四个Channel 组合成一个QUAD,每个QUAD 有两组参考时钟输入,一个QPLL,4 个CPLL,CPLL 输出时钟频率最高3.125Ghz,通信链路线速率最高6.25Gbps,QPLL 输出时钟频率则在5.93Ghz~12.5Ghz 范围内。

由Xilinx 官方手册PG047 可知,每个QUAD 的参考时钟,除了驱动自身外,还可以为相邻的两个QUAD 提供时钟驱动。如QUAD116 的参考时钟(MGTREFCLK0/MGTREFCLK1)就可以同时驱动QUAD115、QUAD116、QUAD117,但QUAD115 就只能同时驱动QUAD115 与QUAD116。

QUAD 内共享资源结构如图2 所示。

千兆网链路通过调用Xilinx“1G/2.5G Ethernet PCS/PMA or SGMII”IP 核完成底层搭建,10G 高速链路通过调用Xilinx“7 Series FPGAs GTX/GTH Transceivers”IP 核完成底层搭建,两者都是基于GTX 硬核实现。

由Xilinx 官方手册PG047 可知,千兆网链路实际线速率为1.25Gbps,IP 核需要125Mhz 参考时钟,使用GTX 的CPLL 资源;Transceiver IP 核实现10Gbps 线速率链路时所需的参考时钟可以为100Mhz、125Mhz 等,需要使用GTX 的QPLL 资源。

图1:高速通信链路规划

图2:GTX 时钟结构

图3:FPGA 时钟资源分配示意图

图4:Transceiver IP 核5 条10G 高速链路参考时钟(100Mhz)分配示意图

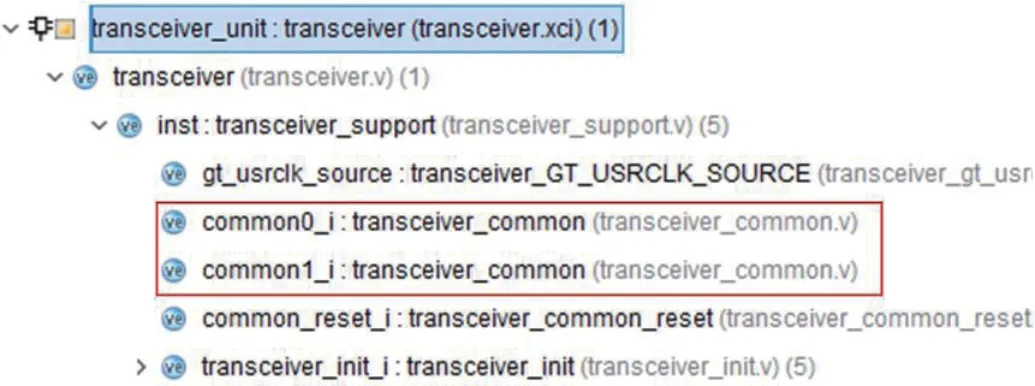

图5:Transceiver IP 核结构层次示意图(Q115 与Q116 均接入Q116 参考时钟)

图6:共享逻辑分配在IP 核内部后文件层级结构示意图

图7:共享逻辑分配在IP 核外部后文件层级结构示意图

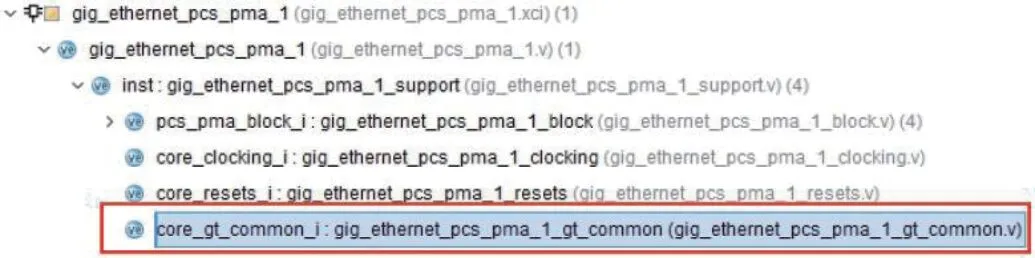

图8:共享逻辑分配在核外移除GT_COMMON 后的千兆网IP 核层级结构图

系统10G Transceiver 链路要保证通信质量,则选择高速收发两端时钟同频同源,千兆网IP 核会通过发送时钟补偿序列完成对时钟差异的校准。

那么要完成需求描述中所有通信链路的搭建,我们时钟资源的最简设计如图3 所示。

即,QUAD116 与QUAD115 的7 条高速链路均采用QUAD116的100Mhz 参考时钟进行驱动,而千兆网则直接使用QUAD115 提供的125Mhz 参考时钟进行驱动。

3 逻辑实现

首先调用“Transceiver”IP 核配置10G 高速链路,为简化操作流程,选择QUAD116 的4 条链路与QUAD115 的GT00/GT01/GT02链路在一个IP核里进行统一配置,如图4所示,而IP核“Shared Logic”则可以选择“Include Shared Logic In Core”,由软件完成10G 通信链路共享资源的分配,而不需要人工介入。

“Transceiver”IP 核结构层次示意图如图5 所示。

接着调用“1G/2.5G Ethernet PCS/PMA or SGMII v15.2”IP 核搭建千兆网,由于IP 核图形界面未提供参考时钟分配接口,仅提供“Shared Logic”分配选项。而如果共享逻辑放在核内,即使实际不会使用QPLL,IP 核依然会默认调用QUAD115 GT_COMMON模块占用QUAD115 的QPLL 资源,从而与QUAD115 的10G 高速链路发生资源调用冲突,如图6 所示。

故千兆网IP 核共享逻辑必须选择放在IP 核外,即“Include Shared Logic In Example Design”选项。在IP 核生成完毕之后打开Example Design,可以看到示例工程中IP 核与共享逻辑层级结构,如图7 所示。

手动将图中方框内文件移植到实际工程中IP 核的上层代码块中,其层级结构如图8 所示。

在上述配置完成后,开发人员就可以创建上层应用,分别实现在当前硬件基础上的最优高速设计。

4 方案可行性验证

所有功能代码添加完成后,对工程进行编译,Vivado 软件未提示错误,将目标文件写入FPGA 中,通过与目标设备进行通信测试,千兆网与10G 高速链路通信均正常且稳定,无误码,数据无丢包。

所有开发及测试均基于Xilinx Vivado 2017.4 版本完成。

5 结论

在遵循开发平台与IP 核厂商设计规则的前提下,通过对已有资源进行合理的分解与重组可以有效提高硬件利用率,节约设计成本。