具备车地传输能力的地铁列车HDLC数据侦听装置

周炯

摘 要:文章通过分析上海地铁一号线列车DINBUS总线物理层、链路层,设计了具备车地传输能力的列车运行数据侦听装置。硬件由基于SOPC II的FPGA收发模块、STM32单片机、LTM收发模块构成;列车运行时,侦听装置将数据存储于Flash中,列车停靠车站时,单片机通过LTE收发模块以UDP协议发送数据至地面服务器。在上海地铁一号线列车对该装置进行了實车测试,能够实时获取列车运行数据,实现了设计目标。进一步开发数据分析软件,即可进行列车技术状态分析,为安全运行提供保障。

关键词:数据侦听;HDLC;SOPC;车地传输;UDP协议

中图分类号:TP393 文献标志码:A 文章编号:2095-2945(2020)03-0014-03

Abstract: Based on the analysis of the physical layer and link layer of DINBUS bus in Shanghai Metro Line 1, a train operation data listening device with vehicle-to-ground transmission capability is designed in this paper. The hardware is composed of FPGA transceiver module based on SOPC II, STM32 single-chip microcomputer and LTM transceiver module. When the train is running, the listening device stores the data in Flash. When the train stops at the station, the single-chip microcomputer sends data to the ground server with UDP protocol through the LTE transceiver module. The device is tested on the train of Shanghai Metro Line 1, and the train operation data can be obtained in real time, and the design goal is achieved. With the further development of data analysis software, the technical status of the train can be analyzed to provide a guarantee for safe operation.

Keywords: data interception; HDLC; SOPC; vehicle-to-ground transmission; UDP protocol

引言

上海地铁一号线采用西门子进口的8辆编组列车,列车于1993年上线运行,距今已有20多年,已经过了2次大修,其控制系统采用了西门子的sibas系统,车辆总线为DinBus。随着车辆运营里程的增加,列车故障率呈上升趋势,故障呈现多样性。当时的车载列车诊断系统功能偏重于运行功能的安全控制,诊断系统人机界面提供的信息是有限的,仅记录列车运行中的故障信息,不具备所有信息的记录功能。车辆逐渐进入生命周期的末段,经过大修没有更换过控制系统的地铁车辆,为保证其运用可靠性,需依托车辆的运行数据进行故障分析、预测,愈来愈多的故障需要进行车辆总线底层的数据分析才能根本解决,从而保证列车的安全运行。

1 系统组成及工作方式

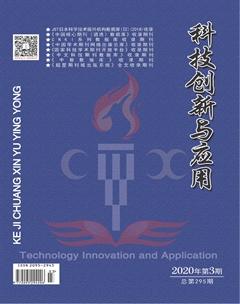

整个装置系统框图如图1所示,由四部分组成。(1)DinBus接口电路;(2)基于SOPC 的FPGA DinBus,主要完成DinBus 总线HDLC链路控制、曼彻斯特编码、解码工作;(3)STM32 单片机及其以太网接口;(4)LTE模块。单片机与FPGA以SPI方式相连;与LTE模块有串口和USB两种方式,以太网接口为连接外部PC进行有线数据下载接口。

侦听装置使用前,需将该车型的总线信息按特定格式编制成文本文件,通过以太网口下载到装置中,下载时采用TCP/IP协议。该接口还可以用于从装置上传数据至pc机,上传数据时采用UDP协议。

2 基于SOPC的总线数据收发模块

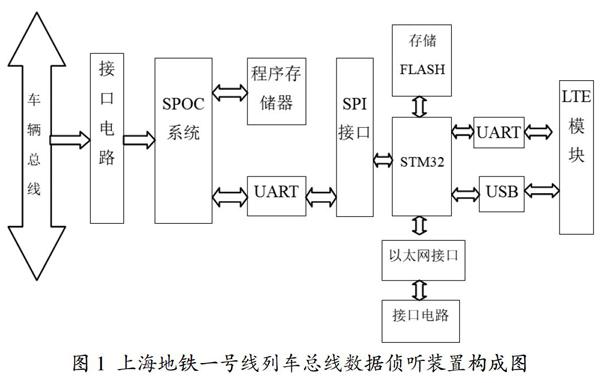

上海地铁一号线列车CCU间数据通讯采用高级数 据链路控制(High Level Data Link Control),简称HDLC,控制方式为主从方式,通讯速率500kbps。本设计的数据收发模块采用Altera公司 Cyclone IV E系列 EP4CE6E2

2C8N,由HDLC IP核和NIOS CPU两部分构成。HDLC IP软核由先导帧检测、时钟解析、同步模块、HDLC链路控制、通信存储器组成;NIOS CPU 是一个通过Avalon总线定制实现的专用处理器,其将Avalon接口、定时器模块、URA核、SPI核共同集成在一片FPGA上。收发模块结构图如图2所示。

2.1 帧检测单元

帧检测单元是一个序列检测电路,采用状态机来实现,采用16倍于总线速率的时钟信号(8MHz)为采样时钟进行采样。检测过程为:总线在空闲时是处于高阻状态的,新的数据帧开始的判断条件为:连续检测到至少16个高电平,紧接着检测到16个低电平后,检测到一个上升沿。

2.2 曼码解码、时钟同步模块

Dinbus总线的曼彻斯特编码有30个先导帧,此部分主要完成帧同步、曼彻斯特编码解码、时钟解析并锁相的工作。

2.3 数据解析&CRC模块

该部分依据HDLC规范进行链路控制、数据解析工作,并进行數据的CRC校验。

2.4 收发模块工作过程

收发模块采用了包含九个状态的有限状态机来实现,如图3所示。图中R_t1, R_t2, R_t3为过渡状态。“帧检测”模块检测到一个新的数据帧开始后,通过使能信号触发曼码解码及时钟同步模块,接收30个先导帧,进行时钟解析及同步工作(Pre_Rec),同步完成后解码出帧头(Head_Rec),根据解析出的帧头数据,判断该帧的类型及数据长度;“R_t1”→“Data_Rec”→“R_t2”→“CRC校验”完成该帧的数据接收及校验,若为功能帧,接收24位数据后转到“R_t3”→“Rec_End”状态;若为数据帧,接收相应长度的数据并进行校验,判定该条数据是否已完整接收(HDLC可通过多帧发送一完整信息),没有完整则转回“R_t1”继续接收余下数据;已完整则转至“R_t3”→“Rec_End”状态。

图3 接收控制状态机

2.5 异常时的处理

接收异常有两种情况:一是“CRC校验”错误,二是帧终止分界符与电平序列不相符。当发生异常情况时,为完整记录数据,该数据仍然保存,并加注异常码。

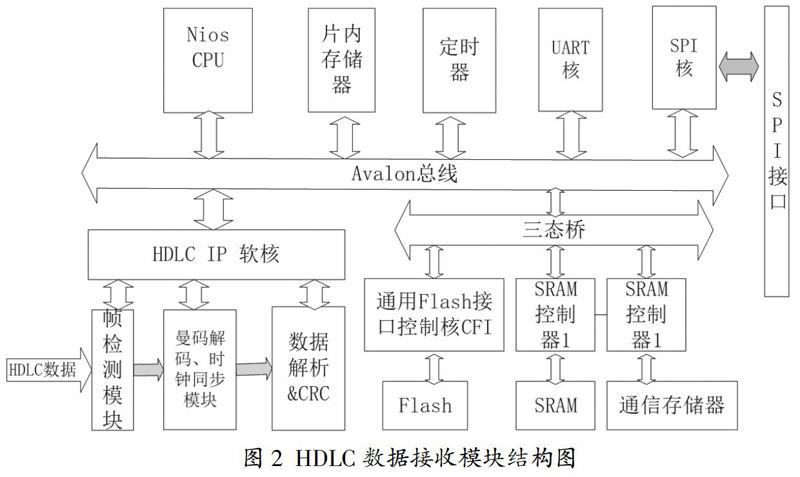

3 LTE模块

LTE模块采用N72V05模块,其结构框图如图4所示。

该模块工作温度为-40°-+85°,LTE数据频段及传输速率为:

?荩LTE FDD: B1, B3, B5, B8:non-CA cat4, Max 150Mbps(DL)/Max 50Mbps(UL)

?荩LTE TDD:B38, B39, B40, B41:non-CA cat4, Max 150Mbps(DL)/Max 50Mbps(UL)

满足上海地铁车地无线传输系统的要求,传输协议按“老车-地面通信协议接口规范”编写。

4 实车测试

4.1 试验环境

为验证设计效果,选择了上海地铁一号线AC01型增扩编列车0120号进行了静态测试,列车由3个单元构成。试验在一个单元中进行,总线拓扑图如图5所示。

总线信息为:总线通讯速率500kbps,CCU(中央控制单元)地址为01,DDU(状态显示单元)地址为02,TCU(牵引单元)地址为03、05,BECU(电制动单元)地址为04、06、07,侦听装置采用透明模式,不占地址。

4.2 试验步骤

(1)连接侦听装置,下载配置文件,设置其IP地址为222.66.139.200,传输端口30110(基于上海地铁车地传输通讯接口规范);(2)合蓄电池,加电;(3)通过DDU观察Sibas系统工作情况;(4)sibas完全启动后,设置一故障(如紧急开门),确认在DDU上已报警;(5)笔记本电脑地址设置为222.66.139.10,连接侦听装置,并下载数据;(6)开启地面服务器,测试LTE连接及数据传输。

4.3 侦听数据示例(见图6)

数据示出了02、03、04与主机01 的交互过程。

5 结束语

本文介绍了具有基于LTE进行车地传输功能的列车HDLC数据侦听装置的结构,对内部各模块的功能进行了描述。通过在上海地铁AC01列车进行现车测试,能够获取HDLC总线数据,可以通过以太网接口下载数据,也可以通过LTE进行车地传输,实现了预期功能。基于通讯协议分析,进一步开发分析软件,即可得出列车不同工况下各设备的具体工作参数;基于大数据的积累、挖掘,可为列车的运用、检修提供数据支持,实现该型列车的智能运维,为安全运营提供保障。

参考文献:

[1]International Electrotechnical Commission.IEC6l375-1.Part l:Train Communication Network[S].Geneva:1999,

[2]王如革,李新胜,赵迪.基于ARM的机车HDLC网络监控终端研制[J].铁道机车与动车,2017(08):47-48.

[3]刘杰宇.基于FPGA技术的HDLC帧收发器的设计与实现[D].北京交通大学,2010.