基于DRFM的间歇采样延时叠加干扰生成设计

张 恒,张文旭,陆满君,朱 剑

(1.哈尔滨工程大学信息与通信工程学院,黑龙江 哈尔滨 150001;2.上海无线电设备研究所,上海 201109;3.南京航空航天大学 电磁频谱空间认知动态系统工信部重点实验室,江苏 南京 211106;4.哈尔滨工程大学工业和信息化部先进船舶通信与信息技术重点实验室,黑龙江 哈尔滨 150001)

0 引言

基于数字射频存储(Digital Radio Frequency memory,DRFM)技术的脉冲压缩雷达干扰样式研究一直是电子对抗领域中的热门课题。雷达有源干扰样式主要分为压制干扰和欺骗干扰。施放压制干扰的目的是使雷达接收机达到饱和,使雷达难以发现真正的目标回波信号;施放欺骗干扰的目的是使雷达收到多个假目标回波信号,引导雷达跟踪错误的目标,达到欺骗的目的[1]。

延时叠加干扰、间歇采样直接转发干扰、间歇采样重复转发干扰等都是基于DRFM的脉冲压缩雷达干扰。延时叠加干扰要求干扰机接收完整的雷达信号,并且需要进行不失真采样,因此干扰机工作方式必须为全收全发。该工作方式导致假目标落后于真目标,这对干扰大时宽、大带宽的信号不利。而间歇采样直接转发或重复转发干扰在干扰距离上有局限性。

针对上述干扰技术的不足,本文对间歇采样重复转发干扰信号的叠加方式进行了深入的研究,提出了基于DRFM的间歇采样叠加转发干扰实现方法,并在硬件平台[2-3]上进行试验验证。

1 间歇采样延时叠加干扰生成原理

1.1 延时叠加干扰的基本原理

延时叠加是使用频繁的雷达干扰生成技术。雷达干扰机把接收的雷达信号以数字信息的方式存储在存储模块之中,然后在内部时钟驱动下进行延时叠加,生成可以使敌方雷达获取错误信息的干扰信号并转发出去,从而达到干扰敌方雷达的目的[4]。

假设雷达信号为s(t),该信号由干扰机接收,延时处理后经由天线发射出去。假设经干扰机处理后的信号为J(t),原雷达信号通过接收机匹配滤波器h(t)后输出的信号为y0(t)。由于h(t)是一个线性系统且具有时不变性,则干扰信号经过脉冲压缩后的输出信号y(t)可表示为

式中:A为干扰机的接收增益;t0为延时时间。由式(1)可以看出:干扰信号脉冲压缩处理结果与原信号脉冲压缩结果是相同的,只是幅度和延时时间有所不同;当t0>0时,假目标滞后于真目标;当t0<0时,假目标超前于真目标。

经过N次延时、叠加,并经过匹配滤波的输出信号可以表示为

由式(2)能够得出以下结论:当Nt0确定后,若延时时间参数t0变小,则延时叠加次数N变大,可以在很短的时间内产生多个欺骗信号去干扰敌方雷达侦察机;同理,若t0变大,N变小,则可在时间间隔较大的各个位置产生假雷达回波,达到欺骗对方雷达的干扰效果[5-6]。

1.2 基于DRFM的间歇采样叠加转发干扰

DRFM技术可以完整高效地存储雷达脉冲信号,因而在雷达干扰系统中得到了广泛应用。在截获雷达发射的脉冲信号后,数字射频存储器对信号进行采样量化并存储,在干扰阶段通过不同的调制方式或者延时叠加方式将所存储的信号进行处理并转发出去,实现对敌方雷达的干扰。

本文利用射频存储器可对存储的数据进行重复读取恢复这一特性,提出了一种基于DRFM的间歇采样叠加干扰的实现方法。其干扰距离更长,适用范围更广,干扰效果更加出色。

间歇采样叠加转发技术在各个不同的时间段内对雷达信号进行采样存储,并采用多种形式对所存储的信号进行处理并转发。干扰原理如图1所示。其中T0为延时时间。

图1 基于延时叠加的间歇采样干扰生成原理图

图1(a)为间歇采样重复转发干扰信号的收发时序示意图,图1(b)将图1(a)中信号延时了T0,图1(c)将图1(a)的信号延时了2T0。图1(d)为间歇采样叠加转发干扰信号时序示意图,该信号由图1(a)~图1(c)所示的三个干扰信号叠加而成。

若雷达发射信号为s(t),间歇采样信号为p(t),则采样后信号的表达式为

将p(t)用傅里叶级数展开,得到

式中:τ为采样信号脉宽;Ts为采样周期;fs为采样频率。

图1(a)所示干扰信号经过脉冲压缩的输出可以表示为

式中:y(t)=x(t)⊗h(t)。则图1(b)和图1(c)信号经过脉冲压缩的输出分别为y's(t-T0)和y's(t-2T0)。图1(d)所示间歇采样叠加转发干扰信号经过雷达匹配滤波后的输出信号形式为

若延时叠加的次数为N,延时转发的最小间隔为N,则间歇采样叠加转发干扰经过匹配滤波后的输出可以表示为

式(7)表明,间歇采样叠加转发干扰算法可以产生干扰距离更远的假目标或假目标群。

2 基于DRFM的雷达干扰机设计

基于DRFM的雷达干扰机的功能包括高速数据采集、信号参数测量、干扰策略制定、数据存储及干扰信号产生等[7]。

2.1 总体方案

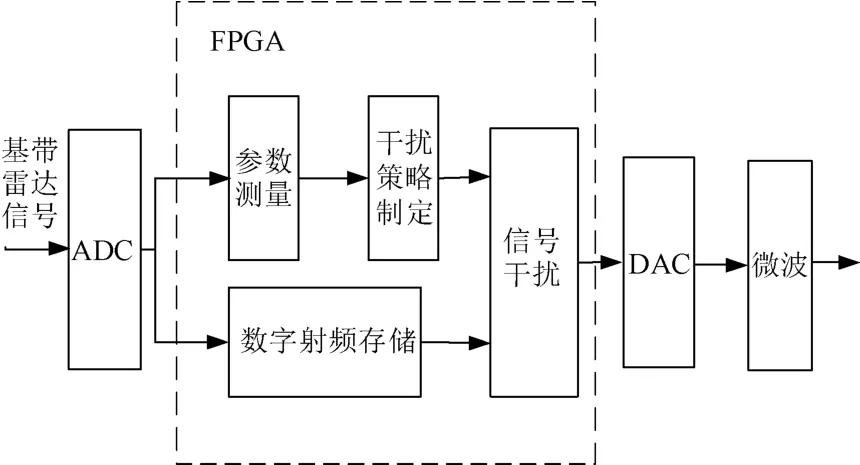

基于DRFM的雷达干扰机基带单元主要由模数转换/数模转换(ADC/DAC)模块、现场可编程门阵列(FPGA)及微波模块组成,如图2所示。其中,ADC模块完成信号的模数转换功能,DAC模块完成信号的数模转换功能,FPGA主要完成对雷达信号的干扰算法实现。微波模块主要实现上下变频功能[8],在此不做详细介绍。

图2 干扰机基带单元组成框图

干扰机的信号处理流程为:首先基带雷达信号由ADC模块模数转换后送入FPGA内进行处理,并在参数测量模块进行雷达参数测量;然后信号干扰模块根据所测雷达信号参数,将雷达信号送入多级先入先出(First Input First Output,FIFO)存储器进行延时叠加,并将处理后的信号送入DAC模块;最后经DAC模块数模转换后把干扰信号发送至微波模块进行上变频,将基带信号转变为射频信号,再经天线将干扰信号发射出去[9]。

FPGA芯片采用的是Xilinx公司的XC6VSX315T,高速模数转换芯片为ADC08D1500,数模转换芯片为DAC9739,时钟芯片为LMK01000和LF4360。

2.2 参数测量模块

参数测量模块主要实现带宽、频率、脉宽及幅度测量等功能。

(1)带宽测量。将所测得频率有符号数转化为无符号数,然后将两个无符号数相减,其差值即为信号带宽。

(2)频率测量。在脉冲信号稳定之后进行雷达脉冲测量,将FPGA内坐标旋转数字计算(Coordinate Rotation Digital Computer,CORDIC)模块输出的相位信息进行一阶差分运算,可得到瞬时频率信息,以此来表征该雷达的载频信息。

(3)脉宽测量。接收检波信号,对每次检波信号进行数值统计,记录计数总和并将数值存储到寄存器中。

(4)幅度测量。CORDIC模块通过旋转逐渐逼近,得到信号的幅度量化值。已知信号源的信号功率,且阻抗为50Ω,由功率计算公式可得到幅度量化值与信号功率的对应关系,即可通过幅度量化值得到信号功率。

2.3 信号干扰模块

基于DRFM技术来设计雷达干扰机,若要生成密集假目标的压制干扰样式[10],需要有效地利用FPGA内部丰富的存储器资源,若采用8级延时,则总的目标假目标数量为28=256。对于欺骗干扰,采用延时叠加的方式,对收到的信号利用FIFO存储器进行延时,若采用4级FIFO存储器进行延时叠加,可产生16个假目标。FPGA芯片内丰富的存储资源可满足信号干扰模块运行及使用间歇采样转发干扰策略的需要[11]。

基于上述原理分析,利用Verilog语言编写生成信号干扰模块。该模块的功能是根据间歇采样的收发控制指令,将接收的信号存储在数字存储器中进行延时和叠加,生成干扰信号后输出。

FIFO存储器作为FPGA内可直接调用的IP核,2的整数倍是其深度设置的标准,而FIFO存储器的深度由延时时间来决定。通常采用控制FIFO存储器输出读地址的方式来控制信号经过FIFO存储器的延时时间。假设FIFO存储器的读取时钟为162.5 MHz,若延时时间为5μs,FIFO存储器需延时162.5×5=813个读取时钟周期,即在FIFO存储器读取并存储雷达信号信息之后,经过813个读取时钟周期再把FIFO存储器中存储的数据通过控制使能读出并发送出去。延时时间与FIFO存储器深度的关系如表1所示。

表1 延时时间与FIFO存储器深度的关系

通过调整延时时间和FIFO存储器深度,能够灵活地实现延时叠加效果。假设延时叠加次数为4,最小延时为1μs,则第7级FIFO存储器的深度应为256,第8级FIFO存储器的深度为256×2=512。

采用如图3所示的干扰信号收发时序。其特点是:在雷达脉冲持续时间内,对信号间歇采样转发;在雷达脉冲持续时间外,对信号进行固定次数的采样转发并设定固定转发时间。该方式能降低脉冲丢失概率,并保证干扰机的掩护范围。

图3 干扰信号收发时序

3 试验验证

由上述分析可知,更改信号进入FIFO存储器后的叠加次数,或更改FIFO存储器的深度,可使延时时间和干扰时长改变,这种变化可产生不同的干扰样式。利用间歇采样叠加转发方式可以生成压制干扰和欺骗干扰。

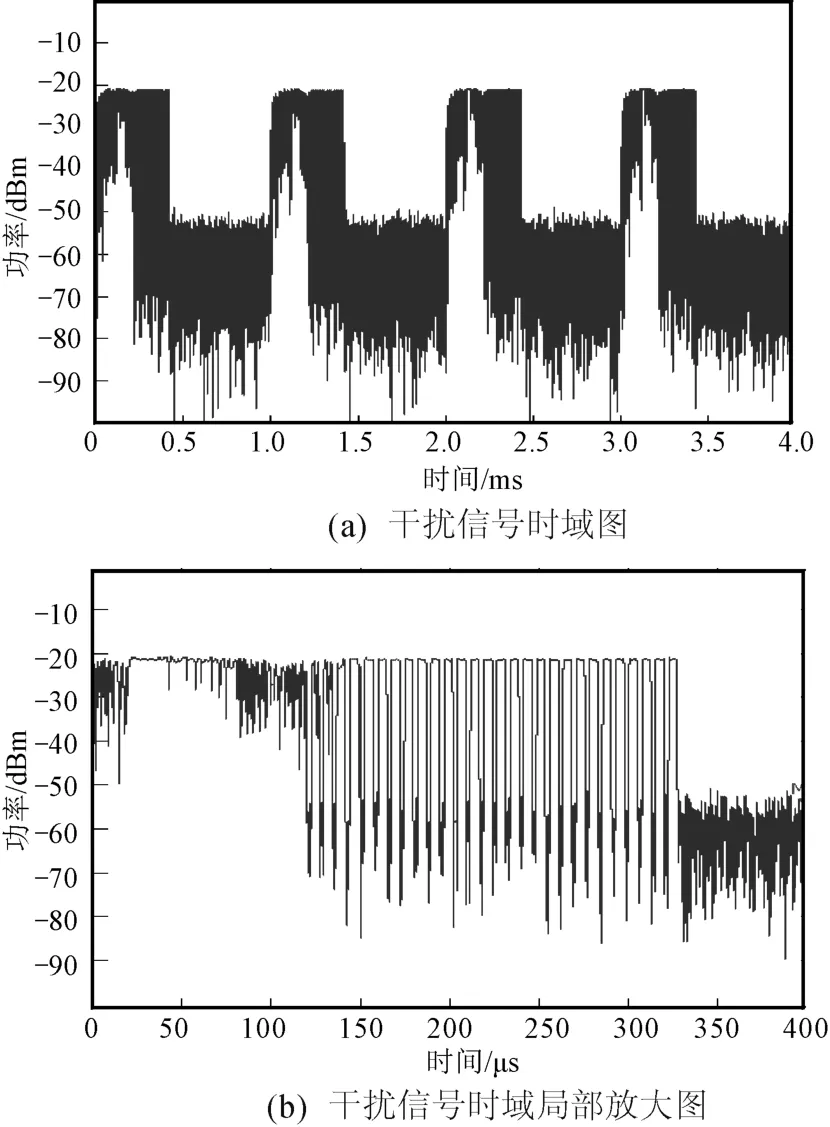

将中心频率为8.1 GHz的雷达信号注入到干扰机中,信号脉宽10μs,带宽5 MHz,脉冲重复周期1 ms,干扰样式设置为压制干扰[12]。雷达信号脉内间歇采样的收发参数为:采样脉宽1μs,转发脉宽1μs,固定转发时长200μs。脉外开窗收发参数为:采样脉宽2μs,转发脉宽6μs,开窗30次。生成基于间歇采样叠加转发的压制干扰信号如图4所示。

图4 基于间歇采样叠加转发的压制干扰信号时域图

由图4可知,干扰信号的压制干扰时长约为450μs,原雷达信号可以淹没在干扰信号中。

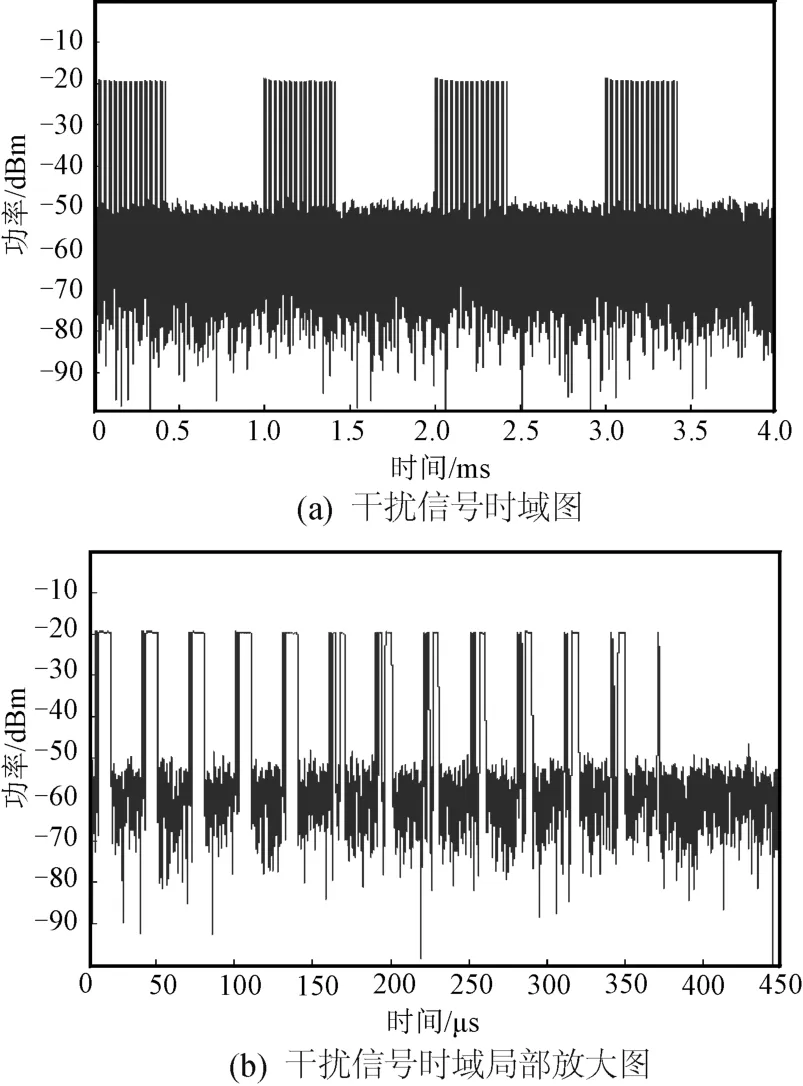

将10.1 GHz的雷达信号注入到干扰机中,其余参数不变,干扰样式设置为欺骗干扰。雷达信号脉内间歇采样的收发参数为:采样脉宽2μs,转发脉宽8μs,固定转发时长200μs。脉外开窗收发参数为:采样脉宽2μs,转发脉宽6μs,开窗30次。生成基于间歇采样叠加转发的欺骗干扰信号如图5所示。

图5 基于间歇采样叠加转发的欺骗干扰信号时域图

由图5可知,欺骗干扰假目标群的个数为14,相邻假目标群之间的最小间距为25μs。

4 结论

本文在现有脉冲压缩雷达技术的基础上,提出了基于数字射频存储技术的间歇采样延时叠加干扰实现方法,并设计对应的干扰机平台对该方法进行了试验验证。结果表明,该方法可有效地对输入的雷达信号进行参数测量以及干扰样式制定,能够高效、精准地干扰目标雷达。