基于FPGA的1553B总线接口技术研究与实现

张晓 胡颖毅 黄子硕 魏鹏

摘 要:为了满足某型机载显示器与机上其他设备的复杂任务和可靠的数据通信,文章提出了一种基于FPGA控制协议芯片SM61864G3实现1553B总线远程终端通信的设计方法。该设计将整个系统的数据处理与接口控制逻辑集成在FPGA内实现,保障系统实时的可确定性。测试结果表明:该通用接口实时性及可靠性高,实际应用效果良好。

关键词:现场可编程逻辑门阵列;1553B;SM61864G3

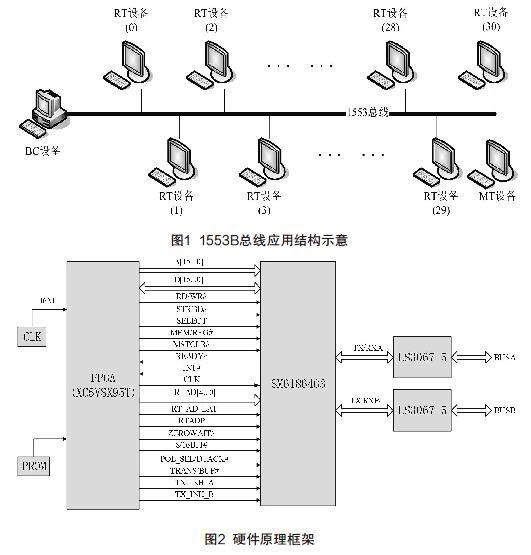

MIL-STD-1553是为数据总线定义的军方标准,该标准作为美国国防部武器系统集成和标准化管理的基础之一,被用来为各系统之间的数据和信息的交换提供媒介,1553B标准总线现已被广泛应用于飞机综合航电应用系统,并逐步扩展到航天、坦克、舰船等领域。1553B总线系统主要由3部分组成:总线控制器BC、远程终端RT、总线监视器BM,其应用结构示意如图1所示。1553B总线接口技术研究与实现作为总线通信的核心,其性能成为影响航电综合系统的关键因素。本文以某机载显示器为平台,采用嵌入式处理的接口方式,实现与机上其他设备的1553B总线通信。

该机载显示器通过1553B总线与外部设备进行信息交互,以1553B总线为主通路,通过1553B总线与综合处理机进行数据交换,自主生成显示画面,能为飞行员提供基本返航信息。本文重点研究RT模式下的应用,开展现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)的1553B总线通信设计,并进行相应的试验验证。

1 硬件系统设计

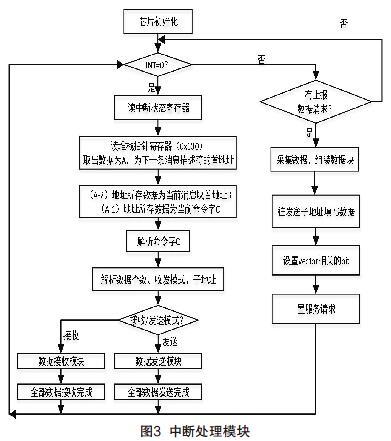

为提高接口的灵活性和扩展性,本文采用FPGA与SM61864G3进行硬件接口与软件设计实现。本设计使用的电路原理如图2所示,其中FPGA选用Xilinx公司生产的XQ5VSX95T可编程逻辑器件。SM61864G3是深圳国微公司设计研发的一款内部集成有数字协议控制电路、双路总线收发器等模块的协议芯片。本文通过FPGA来控制协议芯片的配置寄存器和内部RAM完成数据的传输。

1553B的耦合方式分为直接耦合和变压器耦合,直接耦合最长传输距离(约30.5 cm),变压器耦合最长距离(约6.1 m),由于传输距离较远,该系统采用变压器耦合的方式,耦合器两端配备终端电阻,具体硬件原理框架如图2所示,SM61864G3通过变压器LS3067-5耦合到1553B总线上,SM61864G3协议芯片完成1553B通信系统的传输层、数据链路层和物理层接口,同时FPGA和SM61864G3的接口及其底层软件构成了应用层、驱动层[1]。

SM61864G3芯片工作模式由其引脚配置决定[2],本系统的配置为16位缓冲工作模式、FPGA共享缓存模式、RT地址锁存、非零等待模式、进行忙位设置等。

2 逻辑设计

2.1 设计远程终端的流程

FPGA控制SM61864G3芯片进行上电自检,完成与综合任务处理机的通信、中断响应、数据的接收和发送,并将接口电路的状态信息(是否离线状态)实时发送给综合任务处理机[3]。FPGA接口控制软件采用模块化设计,使软件具有较好的移植性,便于后期维护,逻辑程序包含初始化模块、中断控制模块、数据处理模块,其中数据处理模块是中断控制模块的重要部分。

2.1.1 初始化模块

系统上电后,完成硬件复位和软件复位后,需要对SM61864G3相应的配置寄存器、子地址查询表以及子地址控制字进行初始化,设置非法指令区。当系统自检结束后,将“忙”位清零,此后该设备就处于在线,只要BC发送一条消息命令与该设备相关,该设备就会作出反应。

2.1.2 中断控制模块

中断控制模块用于接收1553B总线数据中断信号,当FPGA芯片接收到中断信号后,通过解析命令,根据总线相应的要求,进行数据接收和发送处理。

2.1.3 数据处理模块

数据处理模块,通过查询相应总线数据标志位,分别来进行1553B总线的接收、處理和发送上位机命令。

(1)FPGA控制SM61864G3的数据发送。作为某机载显示器,在没有特殊情况时,暂不需要进行周期性的数据发送,但需要根据机上操作人员的指令,进行指令数据发送,即数据上报。当FPGA检测到SM61864G3需要进行数据上报请求时,采集数据,组装成数据块,将对应子地址的数据字发送到相应的查询表地址中,同时按照接口控制文件要求,将相应子地址的矢量字置为“1”。FPGA中断控制模块中,当检测到命令字与发送子地址相同时,表明SM61864G3已将需要上传的数据发送到1553B总线上,此时,在FPGA中断控制模块中将该发送子地址的矢量字清零。完成数据上传后,进入中断等待状态。

(2)FPGA控制SM61864G3的数据接收。当RT接收到BC的命令,需要进行数据接收时,FPGA判断该指令为合法指令,若为合法指令,SM61864G3协议芯片回复综合任务处理机命令收到,将相应的数据存储在芯片内部的RAM缓存中,同时输出中断信号给FPGA,此时FPGA需要进行命令字的解析和判断,按接口控制文件的要求及时将BC发送的数据从缓冲区中取出。完成数据接收后,进入中断等待状态。

2.2 初始化模块

对于某机载显示器,作为RT模式,电路上电后,系统的复位电路将MSTCLR#引脚置低大约200 ms,完成对SM61864G3硬件复位;之后对SM61864G3进行软件复位,即通过FPGA对启动/复位寄存器进行相应的配置。完成复位后,FPGA对相应的配置寄存器、相应的子地址查询表以及子地址控制字进行初始化配置,设置非法指令区等。

在完成芯片初始化后,FPGA完成协议芯片的上电自检后,FPGA将子地址忙位表中的接收部分清零,此后RT(机载显示器)处于在线状态,可实时响应综合任务处理机发出的消息命令,并接收和上传1553B数据。

2.3 中断处理模块

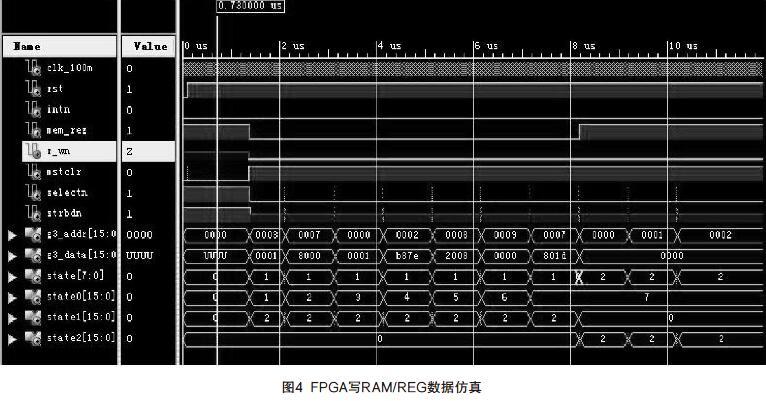

FPGA完成对SM61864G3的初始化后,系统状态机处在1553B控制主状态机的中断处理模块的等待状态。SM61864G3协议芯片具有1个8 bit地址(0x00~0xFF)的存储空间,用于存储记录消息的描述符,每个消息的描述符占用4个存储空间,从上到下依次存储消息状态、消息时间、数据指针、命令字,一共可存储64个消息的描述符。当接收到新的消息后,协议芯片将该消息的描述符存储,将下一条消息描述符的首地址更新至堆栈指针寄存器中,并向FPGA发出中断信号。FPGA接收到中断信号后,首先解析堆栈指针寄存器中存储的地址A,应从A-2,A-1地址中读取数据指针和命令字。其次,根据消息描述符存储的数据指针和命令字,在RAM中读取总线数据。如果是对于发送子地址的命令,进入发送数据模块,待发送完成,清除相关vector位即可;当判断为接收命令时,根据消息描述符中的数据块指针,找到接收数据块并保存数据至FPGA,退出中断。若需要上传数据,则将数据写入到命令缓存里,置相应的服务请求后,等待BC将数据读走。中断处理模块流程如图3所示。

2.4 读/写数据模块

本文以数据接收,即读SM61864G3协议芯片内部的缓存RAM为例来说明FPGA的时序逻辑设计[4]。SM61864G3 RAM读写时序是采用FPGA对芯片内部缓存RAM的读写操作来实现的。

FPGA设置SM61864G3的2号配置寄存器bit3为“0”,当SM61864G3收到接收数据命令,且当总线上数据传输完成后,其芯片管脚INT输出低电平,向FPGA发出中断请求。FPGA通过对SM61864G3的STRBD,SELECT,MEM/REG进行逻辑控制,在其中断控制模块中,及时将芯片RAM内数据读出。为验证逻辑正确性,编写testbench,仿真FPGA写RAM/REG数据的过程如图4所示。

3 系统测试验证

采用欧比特公司生产的仿真板卡—“EMBC1000-USB1553BEI-1错误注入型USB接口单通道1553B总线通信模块”进行调试,测试本文设计的1553B总线数据收发。以某机载显示器为测试平台,以板卡的上位机模拟综合任务处理机,通过自定义命令消息,验证1553B数据在显示器上数据和状态的显示以及数据上传功能。通过测试,系统可正确实现1553B数据的接收和发送,并处于稳定的状态,满足设计需求。

4 结语

本文采用的FPGA控制1553B接口协议芯片总线接口电路及FPGA实现数据通信的方法,应用在某机载显示器中,系统工作稳定,运行良好。

[参考文献]

[1]徐丽清,姬劳.1553B总线接口技术研究及FPGA实现[D].西安:西北工业大学,2006.

[2]DATA DEVICE CORPORATION.BU-6174X/61864X/6186X Enhanced miniature advanced communications engine[Z].Volume 2 Hardware Reference,2005.

[3]郭克平,王丹.基于BU-61864的1553B總线接口电路设计[J].科技创新导报,2013(10):38-39,41.

[4]张飞,王焕玉,徐玉朋,等.基于FPGA控制实现的1553B总线通讯设计[J].航天控制,2010(6):67-71.

Research and implementation of 1553B bus interface technology based on FPGA

Zhang Xiao, Hu Yingyi, Huang Zishuo, Wei Peng

(Beijing Keeven Aviation Instrument Co., Ltd., Beijing 101300, China)

Abstract:Aiming to accomplish the complex tasks and reliable communication between some kind of on-board display and other equipment on board. This paper presents a design method of realizing 1553B bus remote terminal communication based on FPGA control protocol chip SM61864G3. In this design, data processing and interface control logic of the whole system are integrated into FPGA to ensure the real-time determinability of the system. The test results show that the universal interface has high real-time performance and reliability, and the practical application effect is good.

Key words:field programmable gate array; 1553B bus; SM61864G3