基于以太网的FPGA远程升级可靠性设计

康志杰

摘要:现场可编程门阵列(FPGA)广泛应用在通信及信息处理等众多领域,传统的基于本地开发环境的FPGA升级方式无法满足工程现场维护的需求,基于以太网传输方式设计了FPGA远程升级系统方案,实现对FPGA配置文件的更新,为产品的升级维护提供了便利。升级过程中的异常情况,通过分析数据处理流程和引发常见问题的异常情况,分别设计了不同的异常处理机制,解决了远程升级失败的问题。对异常处理机制进行了充分测试,验证了设计的可靠性。

关键词:现场可编程门阵列;远程升级;可靠性

中图分类号:TP393文献标志码:A文章编号:1008-1739(2020)08-61-4

0引言

现场可编程门阵列(Field Programmable Gate Array,FPGA)具有并行处理架构,高速数据处理能力远优于一般CPU,因而在航空航天、医疗设备、通信、汽车及工控等领域得到了广泛应用[1]。而FPGA的配置文件升级维护,通常需要工程人员到现场利用JTAG进行升级。当待升级设备和技术人员处在不同地点时,传统的升级方式将造成时间和人力的浪费。而远程在线升级技术,可以利用以太网实现设备升级,不受人机地点的限制。此外,基于以太网的升级方式可以同时进行大批量的设备升级。目前针对远程升级的方案,主要有利用FPGA内部逻辑更新Flash[2-3]和利用CPU直接更新Flash[4]。通常情况下,远程升级成功的关键在于升级包数据准确无误地写入Flash,在升级包数据传输过程中一旦发生断电、传输错误及CPU软复位等异常,Flash中原有的配置文件完整性可能被破坏,这种情况下只能依赖JTAG重新下载配置文件。为规避这些异常带来的风险,本文针对CPU+FPGA架构类型的板卡,提出了一种可靠的FPGA远程升级方案,已成功应用在通信系统上。

1远程升级关键技术

对于CPU+FPGA架构类型的板卡,在远程升级过程中需要解决CPU软复位、板卡意外断电及数据传输错误等关键问题。

如果不做特殊处理,升级失败就会导致FPGA无法加载,产生灾难性后果。一旦发生,只能拆开设备通过JTAG重新下载程序。针对这些问题,分别设计了不同的处理技术以实现升级的稳定可靠。

1.1握手帧和传输状态机技术

升级过程中,CPU可能在任意时刻软复位,从而导致数据传输中断。针对该情况,设计了CPU和FPGA握手帧格式,如图1所示。

FPGA处理升级包的状态机,如图2所示。

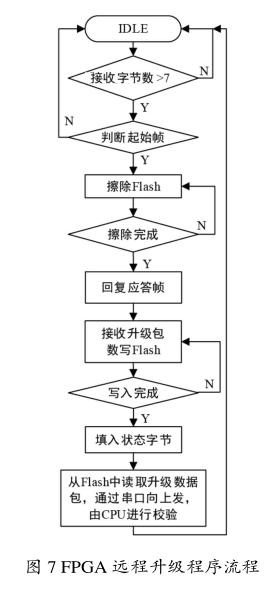

上述状态机中设计了超时计数状态,用来处理CPU因复位导致的意外停发。在帧头标志字接收、配置地址长度字接收、rbf文件接收下发及校验结果接收等状态时,若在限定时间内未接收到CPU的数据,该状态机将强制回到空闲状态,以等待下次升级。

1.2 Flash状态字保护技术

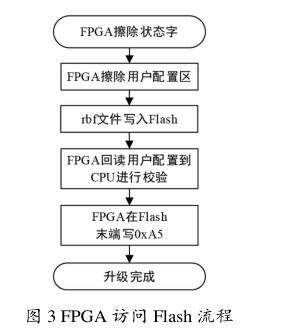

意外断电发生在FPGA访问Flash期间,会对系统产生影响,其他时间断电不会对系统产生任何影响,只需重新上电,系统即可恢复到升级前状态。因此,需要对访问Flash期间的意外断电进行保护,升级过程中FPGA访问Flash流程,如圖3所示。

在FPGA访问Flash时,首先擦除状态字节(地址0x7FFFF),待访问完毕后,重新在状态字打上0xA5标志,这样任何时刻在访问Flash时发生断电,再次上电时,因不满足由出厂配置跳转到用户配置的条件,系统只停留在出厂配置运行。出厂配置中包含升级功能,可重新启动升级过程,该方法能有效避免断电带来的“灾难性”影响。

1.3数据传输保护技术

升级过程中,升级包字节传输错误同样会导致不可预知的程序功能异常,为保证整个链路数据正确传输,整个升级过程共包含3次校验,有效保证了数据的正确传输。

第1次校验:升级包由PC机下发到板卡的CPU,升级包内包含MD5校验字节,CPU在收到升级包后,同样会进行MD5值计算,计算所得结果与升级包内MD5校验字节进行比对,若一致,则认为升级包正常接收,否则会提示升级失败。该次校验保证了数据包从PC机到板卡CPU的正确传输。

第2次校验:CPU与FPGA的握手帧CRC校验,主要为了保证握手帧中用户配置地址和升级包长度接收无误。如果该部分字节错误,可能造成Flash内原始固化的出厂文件损坏或写入错误的用户配置,这种情况下可能造成系统“变砖”。借助CRC校验,有效避免了这种情况的发生。

第3次校验:CPU下发的升级包和FPGA从Flash回读的升级包进行对比,完全一致后,CPU向上位机和FPGA分别发送升级成功标志,这样保证了要升级的程序正确写到了Flash内部,避免升级完成后程序功能出现异常。

2远程升级系统方案

2.1系统架构

远程升级系统架构如图4所示。

升級文件经由PC机、网线、CPU及FPGA传输到Flash配置芯片[5]。

2.2 CPU端处理框图

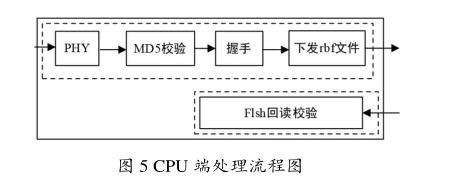

PC机通过以太网与CPU进行数据交互,CPU内模块处理流程图,如图5所示。

PC端上位机下发的升级包包含rbf文件(依赖于FPGA综合工具生成)和随路MD5校验值两部分。CPU接收到升级包后提取rbf文件,计算MD5,与随路MD5校验值比较,如果二者一致,则认为CPU正确地接收了升级包。然后CPU与FPGA握手,提取rbf文件下发到FPGA中,等待FPGA从Flash回读rbf文件进行校验,最后下发校验结果到FPGA并且上报到PC端。

2.3 FPGA端处理流程图

FPGA端处理框图如图6所示。

各个模块的功能如下:

①Flash管理模块:负责接收升级数据包、升级完成后向上发送回读数据包及升级完成后指导配置切换模块切换配置文件。

②配置切换模块:负责用户配置和出厂配置的切换。

③用户逻辑:为用户自定义功能逻辑块。

④UART_ASMI模块:工作在50 MHz时钟下,负责从串口接收数据,串行转并行后发送到ASMI_FIFO中,接收UART_FIFO发送过来的数据并行转串行向上发送。

⑤ASMI_FIFO,UART_FIFO模块:负责进行时钟域的转换,UART_ASMI与FIFO交互时钟为50 MHz,ASMI_CONTROL模块与FIFO交互时钟为10 MHz。

⑥ASMI_CONTROL:负责控制ASMI_UPDATE(ASMI_PARALLEL)核,向外部串行Flash写入升级数据,从Flash读取升级数据包,擦除Flash等。

⑦ASMI_UPDATE_IP:访问外部Flash的IP,该IP核直接控制Flash的读写。

⑧RU_CB及REMOTE_ UPDATE_IP:负责出厂配置文件和用户配置文件的切换。

FPGA远程升级程序流程图如图7所示。

3 Flash地址空间及配置文件跳转

FPGA升级完成后,能正常运行的条件是:①Flash内部按预设的地址空间存储着正确的配置文件;②由出厂配置向用户配置的跳转关系成立。

3.1 Flash地址空间分配

Flash芯片内部地址空间如图8所示。

出厂配置文件(FAC)存储在Flash存储空间的前半部分,FAC内包含升级功能及用户基本功能。而用户配置文件存放在0x40000~0x7FFFE的地址空间。0x7FFFF地址用来存储状态字,用来标识用户配置文件是否正确完好。

3.2配置文件跳转

Flash内配置文件跳转关系如图9所示。

板卡出厂情况下,Flash内要固化出厂配置和用户配置文件。板卡上电后,系统应能正确检测出用户配置文件的正确与否,然后决定是否由出厂配置文件跳转到用户配置文件去执行。

一旦Flash内部存储的出厂配置文件、用户配置文件被破坏,配置文件将无法正常执行,这种情况下只能依赖JTAG重新下载出厂配置文件。升级过程中的意外断电和CPU软复位,将会造成用户配置文件被破坏。而数据传输错误可能造成出厂配置文件、用户配置文件被破坏。在用户配置文件被破坏的条件下,仍然需要依赖出厂配置文件重新远程升级,实现新的用户配置文件的写入。因此,远程升级的关键技术在于:在意外断电、数据传输错误和CPU软复位情况发生后,系统仍然能够再次远程升级,而不是通过JTAG去下载。

4测试结果及分析

4.1测试环境

测试硬件环境为通信系统板卡,板载CPU是NXP的SOC芯片,FPGA是ALTERA的EP4C,上位机软件是自研管理软件。上位机能获取FPGA正在运行的配置文件版本号,从而能够验证升级成功与否[6]。FPGA出厂配置文件版本号为V01,初始用户配置文件版本号为V02,升级后的用户配置文件版本号为V03。

4.2测试用例及结果

测试1:CPU意外软复位对升级的影响

设计了4个时刻插入CPU软复位,测试结果如表1所示。

通过测试,在CPU异常软复位后,系统均能重新利用网络进行升级。其中,在测试用例4的测试情况下,板卡重上电后,由于用户配置已被擦除,故只能执行出厂配置。在出厂配置运行时,可以重新进行升级。上述测试用例每个进行100次测试,最终能100%升级成功。

测试2:板卡意外断电对升级的影响

设计了2个测试用例测试升级过程中意外断电的影响,测试结果如表2所示。

每个测试用例均测试100次,最终100%升级成功。测试结果表明,在系统升级过程中,因异常断电导致的系统升级失败,在重新上电后,能重新利用網络进行再次升级。

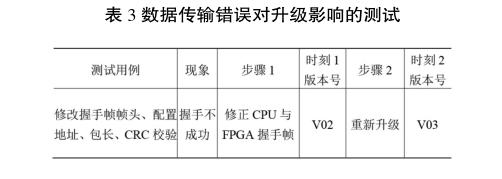

测试3:数据传输错误对升级的影响

为测试对抗数据传输错误的能力,对数据传输链路上部分字节进行修改后,测试结果如表3所示。

当握手帧出现错误字节后,均无法成功握手。此外,故意修改FPGA从Flash回读的配置文件,当送到CPU校验时,无法通过校验。测试结果表明,设计方案能应对数据传输中出现的错误。

5结束语

通过工程实际测试,该远程升级方法实现简单、稳定可靠,不会导致系统“变砖”,不需要修改硬件,易于移植。适用于大批量、非易接触设备的板卡升级,已在多种板卡上应用。

参考文献

[1]刘永恩,王俊芳.FPGA远程升级技术的分析与实现[J].无线电工程,2012,42(9):48-50,60.

[2]闫双山,胡学龙,季静,等.串口更新FPGA配置文件的一种实现方法[J].国外电子测量技术,2019,38(10):79-83.

[3]丁丁,汤晓斌,陈立德,等.基于μClinux的FPGA远程更新系统的实现[J].电子技术应用,2014,40(3):6-8.

[4]姚远.基于JTAG接口实现ARM对FPGA的Firmware远程配置[D].沈阳:沈阳航空航天大学,2011.

[5]李强,罗超,夏威,等.FPGA远程更新系统[J].仪表技术与传感器,2014(7):72-74.

[6]周琼,周鹏.单核FPGA系统的可靠性远程升级设计[J].中国新通信,2018,20(2):47-49.