数字钟电子设计研究

梁可 常楠 郭磊 段昭烈

摘 要:本设计是采用数字电路技术实现基本时钟功能时、分、秒,并能进行整点报时和校准的制作。数字钟适用于家庭钟设计,倒计时装置设计,也适用于各种电气设备和其他医疗设备上。为达到巩固数字电路与模拟电路的学习知识并实际运用的效果,本设计主要采用中小型规模集成电路设计数字钟电路。

关键词:数字钟;译码计数;数字电路

1前言

数字钟常用于人们的生活中,能在跑步时计时,能在手表上报时,能在闹钟响铃。人们生活中无处不在,它能具象出时间的流逝,使人们生活更加高效。

1.1设计背景

数字钟是一种用简单数字电路技术可实现的电子设计,仅用简易的电子元器件便可实现准点报时,计数等要求。

1.2设计目标

本设计主要是利用如计数器、触发器、与门、异或门等数字逻辑器件,将脉冲进行计数,并用6位数码管显示出来,其主要功能是能较精确的进行时间显示和时间校准,并实现整点报时的附加功能,具体设计要求:

(1)产生的秒脉冲频率精确;

(2)可完成整点报时功能;

(3)数码管显示时间准确,可实现校准功能。

1.3必备条件

要求使用晶体振荡器产生频率为1Hz的时钟基准信号电路,电路秒信号发生器由CD4060和CD4013组成。它与电容、电阻、石英晶体等元器件共同组成32768Hz振荡器,后进行14级二分频,[2]再采用D触发器(CD4013)进行二分频,输出1Hz的时秒信号。通过数字逻辑运算,采用74LS390计数,经七段显示译码器CD4511直接驱动LED数码管显示对应时间,并能通过单刀双掷开关对时钟进行校时,在整点时蜂鸣器进行报时。

1.4方案比较

1.4.1方案一

通过1个NE555定时器与多个电阻和电容组成多谐振荡器,输出频率为1kHz的信号,再经分频器74F160产生1Hz时钟脉冲所需的频率,(或经过3个74LS90级联而成的千分频器产生1Hz脉冲)提供给计数单元,并通过译码驱动在数码管上显示出来。[1]采用NE555芯片组成的多谐振荡器可输出符合要求的频率脉冲,其计算可由公式得:

计算得:

通过计算结果与仿真当R2调整为10kΩ左右时,输出频率更加接近于1KHz。

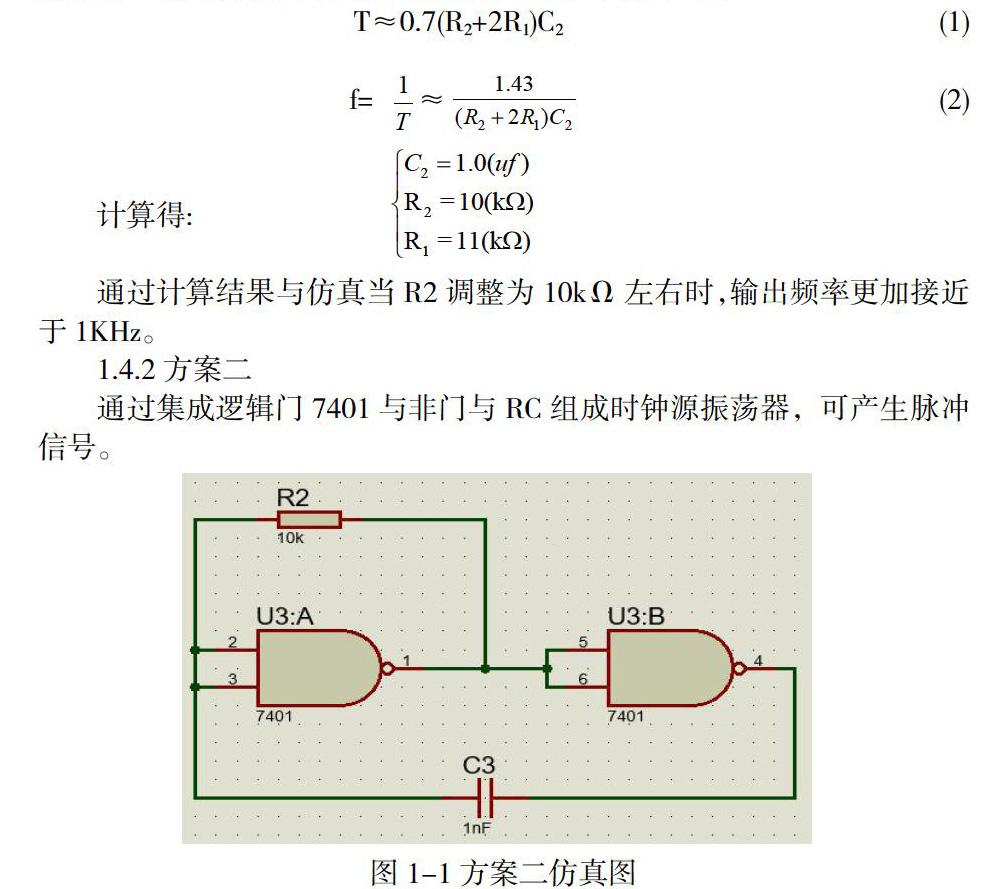

1.4.2方案二

通过集成逻辑门7401与非门与RC组成时钟源振荡器,可产生脉冲信号。

1.4.3方案三

对发出的秒冲信号进行设计,采用32768Hz的晶体振荡器和外接电阻、电容、石英晶体共同组成振荡器,通过CD4060并进行14级二分频,再经D触发器(CD4013)进行二分频,输出1Hz的秒信号。

1.5方案论证

方案一NE555构成的多谐振荡器难以准确输出1KHz的频率脉冲,可能时钟不准确,同时其对电阻和电容的精度要求较高。不易输出符合要求的频率脉冲。

方案二采用RC组成的振荡电路,不仅与时间常数τ相关,还取决于阈值电压VTH,两者均易受电源电压,温度等因素干扰,因此频率稳定性差。故不采用此方案。

方案三采用石英晶振产生脉冲信号,有着输出频率准确,不易干扰的优点。

1.6方案选择

由于数字钟电路的设计,注重时钟显示的准确度,精准的时间是数字钟的核心,因此采用32768石英振荡器稳定输出32768Hz(215)脉冲,再经CD4060进行14分频计数再外加级D触发器(CD4013)二分频,输出1Hz的时基秒信号。可输出1Hz脉冲,因此采用方案三准确输出1Hz脉冲,提高了方案的准确性。

2各单元模块功能介绍及电路设计

数字钟设计主要含有5个单元模块,它们分别是:1Hz时钟信号模块、60进制和24进制计数器模块、译码驱动数码管显示模块、校时模块和整点报时模块。

2.11Hz时钟信号模块设计

该模块因无法一次性直接产生1Hz的低信号脉冲,因此采用石英晶体振荡电路,它与CD4060组成32768Hz(215)振蕩器,再外加D触发器(CD4013)二分频,因此采用了14级二分频,输出1Hz的时脉冲信号。

1Hz时钟信号模块的两个电容(C3,C4)是晶振的负载电容,分别接在晶振两端和对地的电容间,一般使用以皮法为单位的电容,它的值过大或过小都会影响到晶振的谐振频率和输出幅度。[2]

式中Cd,Cg分别为接在晶振和对地电容间,Cic(集成电路内部电容)+△C(PCB上电容)一般为3至5pf。这两个电容串联后并联在谐振通路上,会影响振荡频率。[2]

2.2计数模块设计

数字钟的分钟和秒钟计时电路要设计为60进制计数器是分钟和秒钟计时电路,为减少器件使用量,分别用两个74LS390芯片构成60进制计数器。将两芯片的个位芯片接成十进制计数器,而将十位计数单元将10进制计数器转换为6进制计数器。

(1)60进制计数器

60进制计数器:在计数部分,采用74LS390芯片构成60进制计数器,将其中一片74LS390设计成10进制计数器,另一片设计成6进制计数器。两片74LS390按反馈清零法串联而成。秒计数器兼具60清零和进位的功能,因此输出脉冲进行清零外,同时还作为分计数器的输入脉冲CP1。分秒计数器基本功能相同,因此此可作为秒计数器的同时,也可作为分计数器。[1]

秒与分钟十位计数器应为6进制计数器,为使芯片构成更加简单,采用相同的器件,对进制进行接线改制。采用将10进制计数器转换为6进制计数器的电路连接方法,分个位与十位基本一致。

(2)24进制计数器

数字钟中各位计数器功能基本相同,但小时的整体计数应为24进制计数器,运用反馈清零法,将两个74LS390级联,接成模100计数器,其中U11构成十位计数器和U12构成个位计数器,在此基础上,借助与门译码和计数器译码清零的功能,将U11的Q2端和U12的Q1端接在与门的输入端。工作时,在第24个脉冲作用后,十位数计数器输出为0010,个位数计数器输出为0100,经与门后,两者在计数器U11和U12的清零端CR使其返回0状态,形成24进制计数器。

2.3译码驱动显示模块設计

译码器对计数器的输出值进行译码,得到数码管显示数据,用于驱动七段数码管的译码器常用的有CD4511,在本设计中用于驱动LED驱动共阴极显示数码管。将其与七段数码管连接即可完成不同数字的显示,数码管dp端为小数点端,在本设计暂不使用,因此接地。

2.4校时模块设计

校时模块可暂时先采用单独的脉冲接入计数器的输入端进行调试。

(1)外接开关S1。

(2)选择蜂鸣器为发声器件。

在校时模块外加入整点报时功能,即在时间出现整点时,数字钟会自动发声,采用555芯片输出稳定电平通过蜂鸣器后,可以使人听到,达到准点报时目的。

3系统调试

采用Proteus软件对计数模块、译码器驱动模块、七段译码显示模块、脉冲发生器、校时模块进行了仿真,达到了目的。

3.1硬件调试

在数字钟硬件调试中,利用Proteus对计数驱动显示模块、校时模块和频率发生模块分别进行了仿真。通过控制单刀双掷开关SW1作为开启端,SW2、SW3、SW4作为校时端,因为信号的精确性和稳定性不可能做到分毫不差,因此电路中需要校准时间功能的电路,人为地调整时间的误差。每搬动一次单刀双掷开关产生一个计数脉冲,实现校时功能。

在总模块分秒计数部分均实现了60进制显示,时计数部分实现24进制清0显示,校时部分搬动单刀双掷开关一次即可调整时间。

4结论

本文从设计的电路应用数字电路计数器、555多谐振荡电路、32768Hz晶振与分频器产生1Hz脉冲功能。在电路设计中为节约电路设计成本,采用一片74LS390可完成两片其他计数器的技术功能。

参考文献:

[1] 康华光,电子技术基础-数字部分[M].高等教育出版社,2014.

[2]徐红霞,数字钟电路的设计[J].广东技术师范学院学报,2008(03):17-20.

作者简介:

梁可(1998—),女,汉族,四川成都,本科,研究方向:电气工程及其自动化。

常楠(1998—),女,汉族,河北唐山,本科,研究方向:电气工程及其自动化。

郭磊(1997—),男,汉族,四川仁寿,本科,研究方向:单片机开发、自动化。

段昭烈(1999—),男,汉族,四川广安,本科,研究方向:单片机开发、自动化。