一种应用于TMR磁强计的12位SAR ADC

梅金硕 崔天宝

摘 要:设计了一种应用于隧道磁阻(TMR)磁强计中的12位逐次逼近型模数转换器(SAR ADC)。其中,DAC电路采用改进式的分段电容阵列,减小面积的同时保证采样精度不受分段耦合电容的影响,采用优化时序以消除外接共模电平的需要并减弱采样过程中MOS开关非理想效应的影响,额外添加失调存储技术以消除电路中的直流失调电压。基于0.35um BCD低压工艺对该结构进行电路设计,利用Cadence Spectre进行指标仿真。仿真结果表明,该SAR ADC对带宽500KHz的模拟正弦信号转换信噪比(SNR)达到67.86dB,有效位数达到10.98位,整体功耗仅为5.75mW,满足TMR磁强计接口电路中模数转换器的性能要求。

关键词:TMR磁强计;SAR ADC;模数转换器;分段电容式

DOI:10.15938/j.jhust.2020.06.004

中图分类号: TN431.1

文献标志码: A

文章编号: 1007-2683(2020)06-0023-07

A 12-bit SAR ADC for Tunnel Magnetoresistance Magnetometer

MEI Jin-shuo, CUI Tian-bao

(School of Sciences, Harbin University of Science and Technology, Harbin 150080,China)

Abstract:A 12-bit successive approximation type analog-to-digital converter is designed for tunnel magnetoresistance magnetometer. An improved segmented capacitor array is employed in the DAC circuit adopts, which can reduce the area and ensure the sampling precision not to be influenced by the segmented coupling capacitor. Meanwhile, optimized timing is used to eliminate the need for external common-mode level and to reduce the non-ideal effect of MOS switch during sampling process, and additional offset storage technology is added to eliminate the DC offset voltage in the circuit. Based on the 0.35um BCD low-voltage process, the circuit design of the structure is carried out, and the index simulation is carried out by Cadence Spectre. The simulation results show that the signal-to-noise ratio (SNR) of the ADC is up to 67.86 DB at 500 KHz bandwidth, and the effective bit number is up to 10.98 bits. The total power consumption of the ADC is only 5.75 mW, which meets the performance requirements of the Analog-to-digital converter circuits of the TMR magnetometer interface circuit.

Keywords:TMR magnetometer; SAR ADC; analog-to-digital converter; segmented capacitance

0 引 言

隨着集成电路、惯性制导、便携式测量等方面需求的不断增加,对各种传感器以及接口电路的精度要求也随之提高[1-2]。模数转换器(ADC)作为连接外界模拟信号与数字处理系统间的桥梁,在传感器接口电路中的重要程度逐年提高[3-5]。为保证传感器对外界信号的高精度、低失真采集,同时兼顾较高续航能力与便携式可植入应用背景,需要对高转换精度低功耗面积的ADC展开进一步研究[6-9]。在众多类型的ADC中,逐次逼近型(SAR)ADC由于其架构简单、易于在较低功耗与较小面积背景下实现并能够达到中高精度等特点,成为众多传感器接口电路中ADC的主要研究方向[10]。

本设计拟应用于某型惯性导航设备中TMR磁强计内部的接口电路,采用0.35μm BCD低压工艺完成电路设计与版图实现。该设计可实现500KHz带宽模拟交流信号的模数转换,转换位数为12位,信噪比高于60dB,有效位数大于10位,ADC整体功耗不超过10mW,版图面积低于2mm2。

1 原 理

SAR ADC的结构框图如图1所示。主要由采样保持电路、比较器、逐次逼近逻辑(SAR Logic)、数模转换器(DAC)电路构成。

SAR ADC的原理为一种二进制搜索算法。模拟信号经过采样保持电路采样后输入至比较器,依次与逐次逼近逻辑反馈的二进制权重电平进行比较。每一次比较得到一位数字输出信号,比较次数越多得到的数字输出越能精确地还原模拟输入信号。对于N位的SAR ADC来说,至少需要经过N次比较才能完成一次模数转换。

以位数较低的四位SAR ADC为例,逐次逼近的工作过程如图2所示。假设输入模拟信号采样后得到电平信号为21/32Vref,在第1个周期,四位数字逻辑置位输出1000,控制DAC通过二进制权重选择输出模拟电平1/2Vref,与输入信号共同进入比较器作比较。由于Vin>1/2Vref,确定最高位数字输出D4=1,此后控制逻辑最高位输出始终保持高电平以存储比较结果;第2个周期数字逻辑置位输出1100,DAC输出模拟电平为3/4Vref与输入信号进行比较,由于Vin<1/2Vref,确定次高位数字输出D3=0;第3个周期数字逻辑置位1010,DAC输出模拟电平为5/8Vref进行比较,Vin>5/8 Vref,确定次低位数字输出D2=1;第4个周期数字逻辑置位1011,DAC输出数字电平为11/16Vref进行比较,Vin<11/16 Vref,确定最低位数字输出D1=0。即经过四个转换周期,得到最终四位数字输出为1010,完成四位SAR ADC的模数转换功能。

SAR ADC的工作原理较为简单,实现方法有很多种,按照DAC单元电路的区别,可主要分为电压定标型、电荷定标型和电流定标型三种。其中电荷定标型采用二进制电容进行电荷转移,配合开关逻辑完成二进制算法。此结构可将采样保持电路与DAC电路融为一体,降低设计难度、节省芯片面积;而且,在现有工艺下电容的匹配精度更高,更易实现较高精度转换;此外,相比其他种类,电容结构没有直流通路不存在静态功耗,已成为目前应用最多的结构类型,也是本设计采用的DAC类型。

但传统二进制电容阵列的电容值随转换位数的提高呈指数型上升趋势,对于本设计所需的12位转换精度,最大电容将达到单位電容的211倍,DAC电容之和为212倍单位电容。这将极大占用芯片面积,并降低整体的转换速率。

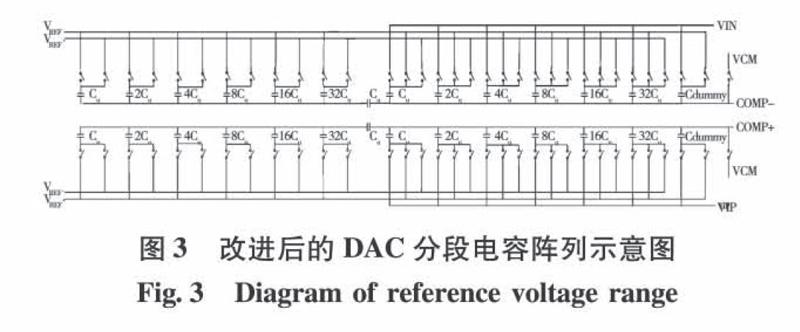

为解决该问题,本设计采用分段式电容阵列,该结构由MSB电容阵列与LSB电容阵列通过分段电容Cu级联构成,为得到最小的DAC电容阵列,本设计选取面积最优的“6+6”分段方案。分段电容值选取为单位电容Cu,分段后MSB与LSB电容阵列中最大值均为25Cu,DAC电容之和近似为27Cu,相比传统二进制电容阵列缩小了32倍,大幅降低了实现所需的芯片面积。

为了消除分段电容的整数取值带来的匹配性问题,本设计采用改进型的采样方法,改进后的DAC分段电容阵列如图3所示 [11]。信号通路只接入MSB分段与一倍单位电容的冗余电容Cdummy,使得分段电容不参与信号的采样过程,从而避免因分段电容的取值误差而引入的采样误差。

SAR ADC的工作过程中需要共模参考电压VCM的参与,因此需要提供一个足够稳定且具备足够驱动能力的共模电平。常规方法是将ADC外部偏置的直流电平接入内置缓冲器和尺寸较大的存储电容以保证驱动能力和电平的稳定性。但该方法对缓冲器的驱动能力和存储电容的尺寸要求较高,对芯片的面积和功耗都有所影响。为避免这一问题,简化电路复杂程度,根据您参考文[12],本文对VCM的产生方法做出改进,改进前后的SAR ADC电路结构如图4所示。其中左侧图为常规产生共模参考电压的电路结构,右侧图为改进后的简化电路结构。

该结构利用开关动作来代替差分缓冲器以实现共模电平VCM的提供。具体的工作过程如下:

在采样相位前,添有一个放电相位,开关S3闭合使电容两侧极板短接,泄放掉前一周期残余的存储电荷以得到较为理想的采样相位初始状态;在采样相位,采样开关S2,共模开关S1闭合,采样电容开始采样输入信号。由于差分结构两端电容完全对称,平分采样电荷,则完成采样后电容右侧极板充电至(VIP-VIN)/2。比较器输入端电压为(VIP-VIN)/2。对于共模电平为VCM的差分输入信号,该电压即可等效为所需的VCM,以供在比较相位完成比较功能。

在电路仿真过程中,会发现不同周期产生的等效共模电平数值稍有不同,呈现周期性波动状态,但与VCM理论值极为接近。并且每一周期的等效VCM都可视为当前周期信号的绝对共模,即便输入信号发生共模偏移,使用该结构也能够正确完成比较。此方法消除了SAR ADC 中缓冲器和存储电容的需要,使得SAR ADC结构除中比较器再无额外的有源器件,功耗和面积都得到了降低。

考虑到寄生电容的存在,可能会导致DAC中开关的建立时间稍有不同,一些开关比另一些状态建立的更快。当输入为至轨电压时,开关管源衬两端反接会导致电荷注入效应的加剧,使得采样电压出现误差,这种现象如图5(a)所示。解决该问题常规的方法是比较器输入端连接较大电容,但这种方法毫无疑问会增加额外面积。在本文中,对采样时钟作延迟处理,令权重最高位开关晚于其余各位开关导通,使得近轨输入电压的采样误差问题得到解决,改进后的逼近效果如图5(b)所示[13]。

2 电路设计

本文所设计的全差分SAR ADC整体电路结构如图6所示。主要包括下极板采样的12位DAC,高速高精度比较器和逐次逼近逻辑电路。信号Autozero控制每一次采样前完成对电容极板残余电荷的清零;IN控制输入信号进入采样电容阵列以及共模电平的生成;A为采样相位;Ad为采样信号A的延迟信号,B为逐次逼近比较相位。

DAC单位电容的容值选取取决于电容失配(mismatch),采样电路KT/C噪声和芯片面积3个方面,其中电容失配,KT/C噪声与电容大小成反比关系,决定电容取值的下限,芯片面积决定电容取值的上限。

为保证采样噪声不是影响ADC转换精度的主要因素,要求采样噪声小于量化噪声,对于12位的SAR ADC来说,量化噪声为

δ2(e)=LSB212=(Vref212-1)2/12(1)

则有:

KTCS≤δ2(e)(2)

考虑电容失配时,引入12位DAC的微分非线性方差[6][14]:

δ2DNL≈218(σ0C0)2LSB2(3)

一般要求:

3δ<12LSB(4)

本设计所选0.35μm BCD低压工艺中提供两种标准电容工艺MIP和PIP。查阅工艺参数文件,可知MIP的单位面积电容密度更高,失配率更低,故选择MIP型电容。综合以上分析,本设计选择面积为400μm2,电容值为267fF的MIP电容作为SAR ADC中DAC的单位电容,采样电容总大小为17pF,DAC中电容总面积约为0.1mm2。

对于比较器的电路实现,本文选择预放大与动态锁存比较器级联的高速高精度比较器方案。预放大器将输入信号放大至锁存比较器能够有效识别的幅值后,动态锁存比较器通过正反馈将信号迅速放大至能被数字电路有效识别的幅度,这种高速高精度比较器结合了开环放大器的负指数响应特性和锁存比较器的正指数响应特性,如图7所示。前置开环放大器在t1时间内将输入信号VOL放大到可以能够被动态比较器识别的VX,动态比较器在t2时间内VX正反馈到至轨电压VOH以被数字信号所识别,整个比较过程的时间为t1+t2,该时间小于单独使用开环放大器或锁存比较器需要的时间。

比较器整体电路结构如图8所示。由预放大器与锁存比较器级联构成。其中预放大器的增益由动态比较器的失调电压VOS和比较器整体精度所决定。一般动态比较器的失调电压约为几十毫伏,此处设定VOS为100mV,12位ADC能够产生的最小比较信号为1/212Vref。为保证Latch比较器的比较结果不受失调电压影响,选取预放大倍数为200,为后续设计预留余量。预放大器需要在锁存比较器之前完成信号的稳定放大,则要求其带宽要远大于比较器的时钟频率。对于开环放大器来所,为获取较大带宽则需要单极增益较小,最终选择3级预放大方案,并采用失调存储结构,利用电容存储各级比较器存在的失调电压,提高整体比较精度 [15]。

预放大器的电路图如图9所示。M1,M2为NMOS输入管,M5,M6为二极管连接的PMOS负载管。引入负载管M7,M8形成正反馈连接,额外提高增益,为保证运放仍能维持稳定状态,M7,M8的宽长比应该小于 M5、M6,否则构成强正反馈,无法建立稳定工作状态。为抑制回踢噪声通过寄生电容从输出端耦合回运放输入端影响比较结果,层叠cascode管M3,M4以用作隔离 [16]。

该结构的直流增益为

AV≈gm1gm5-gm7+1ro1(5)

单位增益带宽为

GBW=AV·P1=gm1CL(6)

对各运放电路进行交流仿真,得到其幅频特性如下:第一级直流增益为6.8dB,单位增益带宽为114MHz,相位裕度为115°。二、三级直流增益为20.6dB,单位增益带宽为110MHz,相位裕度为87°。三级增益之和为251,带宽远高于锁存比较器时钟频率,满足预放大电路设计要求。

锁存比较器可以分为两部分:动态再生比较器与RS锁存器。图10为Latch比较器整体电路结构,中间部分为带控制信号的动态再生比较器,两侧电路共同组成RS锁存器。其中晶体管PM0为比较器作为电流源,PM1,PM2为差分输入端,PM3,NM1,NM2,NM5受控制信号clk控制,PM4,PM5与NM3,NM4构成反相器首尾相连的正反馈结构。当控制信号clk为高电平时为采样相位,反馈环路被短路,输入信号进入正反馈两端,完成信号差值的采集功能。clk为低电平时为比较相位,输入端关断,反馈环路开始工作,前半周期采集的信号差被正反馈不断放大到至轨电压,完成比较功能。

由于采样相位动态比较器处于偏置状态并未进行比较,输出端不能表示比较结果,因此需要接入RS锁存器,将上一周期比较相位的输出结果额外锁存半个周期以掩盖采样相位的输出电压,直到产生新的比较结果。因此此种结构的动态再生比较器的输出与输入间存在半个控制周期的延迟。

为降低比较器静态功耗,尽量降低电流源PM0提供的静态电流。增大输入管尺寸有助于提高比较器的比较精度。钟控管PM3,NM1,NM2,NM5尺寸尽量缩小,以减弱在导通关断过程中的电荷注入和时钟馈通效应对比较器的精度的影响。

对比较器整体电路进行瞬态仿真,输入幅度为2mV,频率为1MHz的正弦信号,与共模信号作比较。时钟控制信号频率为20MHz,占空比为50%。仿真结果如图11所示。对于该输入信号能够完成准确比较,满足系统设计需求。

SAR ADC中的SAR 逻辑部分所处理的信号为数字信号,在电路结构的选择上以简单易实现,可靠性强为原则。本设计选用目前使用最广泛的一种结构,如图12所示。

该结构是最早出现的逐次逼近逻辑电路,利用两层带有复位和置位端口的D触发器构成12位移位寄存器。其中上层D触发器实现移位功能,下层实现寄存功能输出12位数字结果D12~D1。电路输入端中,CLK为时钟信号,COMP为比较器输出信号;RESET为逻辑复位信号,低电平有效;SET为逻辑置位信号,低电平有效;输出端D12至D1作为SAR ADC 整体输出的12位并行数字输出信号。移位寄存功能如图13所示。图中令比较结果一直为零,能够更直观地观察到移位的动作。

3 仿真验证

确定整体电路结构后,采用0.35μm BCD低压工艺,实现上述SAR ADC的整体电路设计工作,并完成版图设计工作如图14所示。整体电路采用5V单电源供电,版图面积为1.5mm2。

首先对SAR ADC进行瞬态仿真,过采样情况下的仿真结果如图15所示。其中平滑曲线为SAR ADC的输入模拟信号,折线为经过模数转换得到的数字信号还原回的模拟电平。可以看出该SAR ADC的转换结果能够完成对输入正弦信号的正确跟随,輸出与输入之间相隔一个转换周期。

设置输入模拟正弦信号频率为135kHz,带宽为500kHz,采样时钟频率为1MHz,使得SAR ADC处于奈奎斯特采样频率进行瞬态仿真,在该条件下将ADC的转换数字结果还原回模拟电平后每个转换周期采样一点,对瞬态仿真得到的数字码流进行FFT变换,得到输出结果的频率响应如图16所示。

噪底为-110dB,信号带宽范围内信噪比为67.86dB,有效位数达到10.98位,符合设计预期。在5V的单电源供电电压下,整体平均功耗仅为5.75mW,满足系统设计要求。

4 结 论

本文设计了全差分结构的12位电荷重分配式SAR ADC,DAC部分采用下极板采样技术,选取“6+6”分段方案,以获取较小电容面积;只有MSB段电容参与采样以避免分段电容带来的采样精度误差;采用改进的开关切换方案消除了外接VCM与缓冲器的需要;优化反馈时序以消除电荷泄露带来的转换误差。比较器部分采用开环预防大器与动态锁存比较器级联模式,采用IOS与OOS两种失调消除技术消除比较器本身引入的失调电压。仿真结果显示,对于频率为500kHz的差分正弦输入信号,该SAR ADC在1MHz的奈奎斯特采样频率下,信号带宽内信噪比为67.86dB,有效位数为10.98位,电路整体功耗为5.75mW,整体版图面积为1.5mm2,满足电路设计指标,符合磁传感器中模数转换器的应用要求。

参考文献:

[1] 卞金洪, 王吉林, 周锋, 高精度压力传感器中温度补偿技术研究[J]. 哈尔滨理工大学学报, 2011, 13(6):55.

BIAN Jinhong, WANG Jilin, ZHOU Feng. Research of Temperature Compensation on High Accuracy PressureSensors [J]. Journal of Harbin University of Science and Technology, 2011,13(6):55.

[2] 李巍, 满春涛, 孙晓波, 等.基于D-最优的半球谐振陀螺仪误差参数辨识研究[J]. 哈尔滨理工大学学报, 2017, 22(2):34.

LI Wei, MAN Chuutao, SI Xiaobo, et al. Research on Test Plan of Hemispherical Resonator Gyros Error Model Coefficients Based on D-optimal Criterion[J]. Journal of Harbin University of Science and Technology, 2017,22(2): 34.

[3] PHILLIP E. Allen, Douglas R. Holberg. CMOS模拟集成电路设计[M]. 北京: 电子工业出版社,2011.

[4] 曹一江, 王振群, 陈建春, 等. 用于低功耗 A/D 转换器的运算跨导放大器设计[J]. 哈尔滨理工大学学报, 2010, 15(2):84.

CAO Yijiang, WANG Zhenqun, CHEN Jianchun, et al. Design of an OTA in a Low Power A/D Converter [J]. Journal of Harbin University of Science and Technology, 2010,15(2):83.

[5] 蔡俊,徐美華,冉峰. 10 位逐次逼近型 A/D转换器的芯片设计. 半导体技术, 2004, 29(4): 73.

CAI Jun, XU Meihua, RAN Feng. Design of a 10Bit Successive Approximation A/D Converter. Semiconductor Technology, 2004, 29(4): 73.

[6] CHAE Y, SOURI K,K. MAKINWA A A. A 6.3 μW 20 Bit Incremental Zoom ADC with 6 ppm INL and 1 μV offset[J], IEEE J. Solid-State Circuits, 2013, 48(12): 3019.

[7] GNEN B, SEBASTIANO F, VAN Veldhoven R, et al. A 1.65 mW 0.16 mm2 Dynamic Zoom ADC with 107.5 dB DR in 20 kHz BW[C]// In Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2016: 282.

[8] AGAH A, VLEUGELS K, GRIFFIN P B, et al. A High-Resolution Low-Power Incremental Sigma-Delta ADC With Extended Range for Biosensor Arrays [J]. IEEE Journal of Solid-State Circuits, 2010, 45(6):1099.

[9] NAVEEN Verma, ANANTHA P. Chandrakasan. A 25μW 100kS/s 12b ADC for Wireless Micro-Sensor Applications[C]// IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig, 2006:222.

[10]卢宇潇. 髙速低功耗逐次逼近式ADC研究与实现[D]. 上海:上海交通大学,2014.

[11]宋孝立. 16位1MS/s CMOS SAR A/D转换器设计及校准技术[D]. 西安:西安电子科技大学, 2014.

[12]Gilbert Promitzer. 12-bit Low-Power Fully Differential Switched Capacitor Noncalibrating Successive Approximation ADC with 1 MS/s[J]. Journal of Solid-State Circuits (JSSC), 2001,36(7): 1138.

[13]T.O. Anderson. Optimum control logic for successive approximation Analog-to-Digital Converters[J]. Computer Design, 1972,11(7):81.

[14]WAKIMOTO T, LI H, MURASE K. Statistical Analysis on the Effect of Capacitance Mismatch in a High-Resolution Successive-Approximation ADC. Electrical and Electronic Engineering, 2011, 6(S1): 89.

[15]李冬. 基于逐次逼近结构的高速低功耗模数转换器研究[D]. 南京:东南大学, 2017.

[16]孙彤. 低功耗逐次逼近模数转换器的研究与设计[D]. 北京:清华大学, 2007.

(编辑:温泽宇)

收稿日期: 2020-01-15

基金项目: 国家自然科学基金(51502063).

作者简介:

崔天宝(1994—),男,硕士研究生.

通信作者:

梅金硕(1981—),女,博士,副教授,硕士研究生导师,E-mail:meijinshuo@126.com.