多层缓冲数据传输优化的设计研究

摘 要:新型的非易失性存储器(NVM)技术的发展带来了几乎与传统DRAM一样的存储性能,这使以往内存、磁盘的二元结构变成内存、NVM及磁盘的数据传输结构,在此情况下出现了多种缓冲数据流的路径。因此文章介绍了管理和设计由DRAM、NVM和SSD组成的多层数据缓冲路径。文章利用NVM特性的多层缓冲数据路径,完成数据缓冲时间的设计。同时提出了用于评估不同数据流完成时间的评价模型,最后提出了一个圆形系统,用于检测目标工作量和系统时间成本模型。

关键词:非易失性存储器;近内存计算;存储系统

中图分类号:TP393.06 文献标识码:A 文章编号:2096-4706(2020)24-0117-03

Design and Research of Multi-layer Buffer Data Transmission Optimization

ZHAO Xiaofei

(Lanzhou Petrochemical Polytechnic,Lanzhou 730060,China)

Abstract:The development of new nonvolatile memory(NVM)technology has brought almost the same storage performance as traditional DRAM,which makes the binary structure of memory and disk become the data transmission structure of memory,NVM and disk. In this case,there are many kinds of buffered data flow paths. Therefore,this paper introduces the management and design of multi-layer data buffer path composed of DRAM,NVM and SSD. In this paper,the design of data buffer time is completed by using NVM characteristic of multi-layer buffer data path. At the same time,an evaluation model is proposed to evaluate the completion time of different data streams. Finally,a circular system is proposed to detect the target workload and system time cost model.

Keywords:nonvolatile memory;near memory computing;storage system

0 引 言

內部存储需要访问数据,如访问在非挥发性存储(例如SSD)上的数据时,缓冲管理器会先将这部分数据注入缓冲器,等到这部分数据被需要时再将数据放入挥发性内存(Dynamic Random Access Memory,DRAM),即动态随机存取存储器,最为常见的系统内存来完成访问存储。这一数据缓冲管理的规范方法基于以下事实:

(1)数据必须复制到DRAM才能完成在新型存储上的访问。

(2)存储的速度比DRAM慢[1-3]。

但随着新型的非易失性存储器(Non-Volatile Memory,NVM,)技术的发展颠覆了这些前提。NVM是一种时下比较流行的存储技术,其主要的实现技术包括相变存储器(Phase-Change Memory)和忆阻器存储器(Memristors)[4-7],该类设备既有DRAM低延迟读写的特性也具备SSD的持久写入以及大存储空间等优点。

NVM类存储设备与传统规范存储技术之间的两个区别:

(1)要处理磁盘驻留的数据,缓冲管理器首先必须将其复制到DRAM,然后才能执行其他操作。相比之下,得益于NVM设备具有CPU可直接寻址的地址表,因此CPU可以直接使用存储在NVM的数据。

(2)NVM缩小了易失性和非易失性设备之间的性能差距。因此,当NVM类设备被用作缓冲池时,传统的缓冲管理器设计与NVM硬件并不兼容。即,缓冲管理器将NVM当作内存来处理时,缓冲数据流无需经过内存;当NVM被当作存储来对待时,NVM几乎可以提供与内存相当的延迟性。

NVM这种与以往缓冲管理器不兼容的特点,即类似内存又类似磁盘的特性为缓冲管理器管理的缓冲数据流提供了多种迁移路径及全新策略设计空间。

为此,本文探索了一组由DRAM、NVM和SSD组成的多层存储结构及多层缓冲数据传输优化的设计,以最大化存储层次结构中不同设备之间数据迁移的效用,从而提升整体系统性能。具体为:

(1)引入了多层缓冲数据传输优化,提出了不同介质之间多层缓冲数据传输优化结构的政策(第2.1节)。

(2)提出了基于时间的数据流传输评价模型来衡量存储系统数据流传输设计时间敏感性指标模型(第2.3节)。

(3)实践了基于上述两点的与ZFS文件系统工作机制结合起来的原型测试系统,实践了主要不同数据流的时间指标的测试(第3节)。

1 研究背景

在现代计算机体系当中,内部存储器的数据流主要是由缓冲器以及缓冲管理器控制。缓冲管理器将计算机的可用内存分区为几组固定大小的区域,这些区域统称为缓冲区。操作系统或者数据库系统等更高级别计算机访问控制组件(如大型集群应用或数据库查询执行引擎等)不用查询页面文件(Page)是否在缓冲区,他们只需要请求缓冲管理器来检索该页面。如果缓冲区中不存在其他组件请求的页面,缓冲管理器会从存储中检索该页面。

缓冲管理器的作用是维护内存中缓冲区里的每个页面的瞬态元数据。此元数据包括对页面的主动引用次数,以及该页面自存储进入缓冲区以来是否已修改等信息。如果缓冲区中已经存在另一个组件请求的页面,则会增加对页面的主动引用次数,并返回包含该页面的缓冲区的地址。否则,缓冲管理器会根据更换策略(例如最近使用最少的)选择更换缓冲区。如果选择替换的页面文件未做任何修改,缓冲管理器会将这些页面文件传输到存储上的相应页面,然后,它将请求的页面从存储中复制到替换槽中,并返回插槽的地址。

2 研究内容

2.1 多层次缓冲数据流结构设计

在多层缓冲数据流的设计中,将讨论新型存储介质参与的比较有实际意义且认为可以提升计算机内部存储完成缓冲数据时间的路径,如:绕过部署在DIMM插槽的NVM介质时,相同的数据传输效果,在不同路径下的完成时间等,如图1所示。

2.2 数据流路径

读取缓冲数据流路径,一般的计算机系统中的内存缓冲数据默认的传输数据读取路径包括三个步骤:将数据从磁盘移至NVM(1或者6),然后移至DRAM(13),最后移至处理器缓存(11)。同样,默认写入路径包括三个步骤:将数据从处理器高速缓存移动到内存(12),然后移动到NVM(14),最后移动到磁盘(3)。在这种情况下缓冲管理器如何利用图1中NVM(部署于DIMM及PCI)带来的附加数据流路径(1,2,3,4,13,14)来优化数据流路径从而发挥NVM的特性来提高整体系统性能。

与磁盘不同,处理器可以直接通过读取操作直接访问NVM上的数据(2)。要访问磁盘上的数据,在其他缓冲管理策略中,缓冲管理器会将其复制到内存(9),然后处理器才能对其进行操作。使用NVM缓冲池后,缓冲管理器可以利用这个新的数据流路径,同时将缓冲数据读取到内存缓冲池及NVM缓冲池。

在这种情况下,研究内容是当缓冲管理器发现内存内的缓冲池需要被替换,或者丢弃时,缓冲管理器仍然会选择保留NVM缓冲池内的数据,直到NVM缓冲池也被填满时、才会丢弃NVM缓冲池内较冷的数据,而当缓冲管理器发现已被从内存缓冲池驱除的页面缓存再次被请求时,可由NVM缓冲池直接提供给处理器。

處理器通过写操作直接将数据保存在NVM上时,缓冲管理器利用此路径以较低的缓冲池开销提供同步持久性。写入操作绕过内存,因为数据必须最终持久化的写入磁盘,使用这种缓冲路径时缩小了整体写入操作的延迟,同时消除对内存的冗余写入。因此它也给内存空出多余的空间用于其他缓冲页面数据。

在这种情况下,释放了大量原本用于写入缓存的内存缓存池,因此确保包含日志和检查点记录的异步写入操作不会驱逐内存中的更热数据,同时更大的NVM存储空间更为适合带有日志的异步写入操作。

当在写入期间绕过NVM,缓冲管理器确保只有频繁内存的页面缓存数据才会存储在NVM上。这种优化减少了对NVM的写入次数,因为只有当缓冲管理器识别的较为频繁的页面缓冲数据存储在NVM缓冲区之中。

2.3 缓冲数据流评价模型

数据流容量变化模型,将多层缓冲数据流建模为具有n级,即L1、L2,…,Ln的线性结构。位于某一层的缓冲数据表示为Li,每完成一次数据流缓冲的命中率为H(在同一次数据缓冲过程中,各个层级的命中率为取定值),在该层次的存储结构中性能由两个因素决定:平均完成时间ti和介质缓冲容量Ci。i级中所有存储块都必须存在于每个级别中,当大于i(即在层次结构中的所有较低级别,偏更靠近外部存储),可以存储在系统中的最大信息等于最低级别Cn的容量,因为存储在系统较高级别的所有块的副本必须存在于Ln中,所以数据流传输容量大小变化模型为:

hi=H(Ci)-H(Ci-1)

块数据流完成时间模型,hi表示缓冲层次结构中i级成功数据访问的相对数量。然后,每完成一次全部缓冲块请求的有效平均访问时间为:

T=

2.4 模型机建立

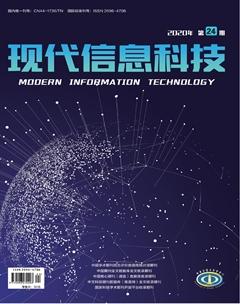

依据数据流路径中的要求,模型机的软件构架如图2所示,部署在DIMM插槽的DRAM及NVM介质由系统内核(Linux系统)提供驱动,数据流由/CPU Scheduling控制;部署在PCI的NVM介质将有ZFS文件系统负责驱动及组织;最后SDD/HDD则有操作系统的块文件API驱动。

3 实际测试

3.1 数据读取情况

如图3所示,数据读取在绕过部署在DIMM的介质时,不同数据流大小在不同路径下的时间性能表现,可以看出新型存储介质完成时间更快,且数据集愈大完成时间更快。

3.2 数据写入情况

如图4所示,数据写入在绕过部署在DIMM的介质时,传统路径对数据大小较为敏感,数据流越大,写入时间越长。

4 结 论

本文介绍了管理和设计由DRAM、NVM和SSD组成的多路径的多层数据流的技术。介绍了一种基于完成时间的用于评估路径性能的数据模型,建立了一个可以用于测试的原型机系统,并在此模型下讨论了是否绕过新型存储介质的数据流路径的性能。结果表明,NVM等新型存储机制带来的多种传输路径在不同数据流大小的工作负载下提高了系统完成传输时间,从而提升了系统响应时间。

参考文献:

[1] TARANTOLA A. Intels 3D memory is 1,000 times faster than modern storage [EB/OL].(2015-07-28).https://www.engadget.com/2015/07/28/intel-3d-memory-1000-times-faster/.

[2] FERRON-JONES M. A New Breakthrough in Persistent Memory Gets Its First Public Demo [EB/OL].(2017-05-16).https://itpeernetwork.intel.com/new-breakthrough-persistent-memory-first-public-demo/.

[3] CUTRESS I,TALLIS B. Intel Launches Optane DIMMs Up To 512 GB:Apache Pass Is Here [EB/OL].(2018-05-30).https://www.anandtech.com/show/12828/intel-launches-optane-dimms-up-to-512gb-apache-pass-is-here.

[4] RAOUX S,BURR G W,M.BREITWISCH M J,et al. Phase-change random access memory [J].IBM Journal of Research and Development,2008,52(4):465–479.

[5] Hewlett Packard Enterprise. HPE Unveils Computer Built for the Era of Big Data [EB/OL].(2017-05-16).https://news.hpe.com/a-new-computer-built-for-the-big-data-era/.

[6] RENEN A V,LEIS V,KEMPER A,et al. Managing Non-Volatile Memory in Database Systems [C]//In Proceedings of the 2018 International Conference on Management of Data.New York:Association for Computing Machinery,2018:1541-1555.

[7] KWON Y,FINGLER H,HUNT T,et al. Strata:A Cross Media File System [C]//In Proceedings of the 26th Symposium on Operating Systems Principles.New York:Association for Computing Machinery,2017:460-477.

作者簡介:赵晓菲(1987.10—),女,汉族,河北衡水人,高职教师,硕士研究生,研究方向:内存计算。