一种新型的级联Sigma-Delta调制器的建模设计

曹仕林, 陈红梅, 尹勇生

(1.合肥工业大学 微电子设计研究所,安徽 合肥 230601; 2.合肥工业大学 教育部IC网上合作研究中心,安徽 合肥 230601)

随着集成电路的快速发展,数字芯片的集成度和计算能力不断提升,高性能数据转换器的需求也不断提升。传统Nyquist-ADC对工艺匹配要求高,Sigma-Delta ADC采用过采样和噪声整形技术抑制带内量化噪声,以速度换取转化器的高精度,目前已经在中低频应用领域占据主导地位。

对于过采样率为M、Nbit量化的L阶Sigma-Delta调制器,其信噪比(signal noise ration,SNR)表示为:

10(2L+1)lgM

(1)

通过(1)式可以看出,想要提高调制器的精度,可以通过增加量化位数、增加调制器阶数或增大过采样率来实现。但增加量化器的位数需要对应的多位反馈DAC,这将引入DAC的非线性问题;增大过采样率对于信号带宽有着严格的限制;增加调制器的阶数将引入高阶调制器的稳定性问题[1]。级联结构(multi-stage noise shaping,MASH)利用低阶调制器级联组成高阶形式,是提升Sigma-Delta调制器精度很好的选择,不存在稳定性问题。

但是对于二阶Sigma-Delta调制器,只有增加量化位数和过采样率来提升精度。目前多位 DAC的动态校准匹配技术已经相对成熟,但依然会大大增加电路设计的复杂度;对于音频信号20 kHz的带宽,过采样率为256时采样频率已达到10.24 MHz,进一步增加过采样率已不符合实际要求。本文提出了一种新型的级联结构的Sigma-Delta调制器,结合级联结构的相关技术,对二阶Sigma-Delta调制器进行改进,使二阶调制器和一个额外的一位量化器组成级联结构,以此提高二阶Sigma-Delta调制器的噪声整形能力。最终的仿真结果显示,在加入电路的非理想因素仿真时,信噪比达到114.4 dB,结果已经超过二阶Sigma-Delta调制器信噪比的理论值。

1 级联结构Sigma-Delta调制器

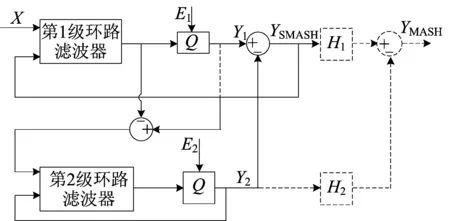

传统的级联Sigma-Delta调制器和Sturdy-MASH调制器如图1所示。

图1 传统的级联Sigma-Delta调制器和Sturdy-MASH调制器

图1中,虚线部分为传统的MASH结构Sigma-Delta调制器,通过将前一阶段的量化噪声输入到下一阶段来实现高阶噪声整形。H1、H2数字滤波器作为消除逻辑用于抵消第1阶量化误差,总输出的计算公式为:

YMASH=STF1H1DX+(NTF1H1D-

STF2H2D)E1-NTF2H2DE2

(2)

其中,STF1、STF2分别为第1、第2级环路的信号传递函数;NTF1、NTF2为噪声传递函数;E1、E2为量化误差。

通过选择H1D=STF2D和H2D=NTF1D可以消除第1级量化噪声E1,其中下标D表示数字电路用于区分模拟环路滤波器。在理想情况下,数字电路和模拟电路的完全匹配可以最终消除。最终输出为:

Y=STF1STF2X-NTF1NTF2E2

(3)

但是,由于模拟滤波器与数字滤波器不匹配,输出端会出现(NTF1STF2D-STF2NTF1D)E1。为了降低这种误差,需要高增益运放和精确的调制器系数来降低由不匹配造成的误差泄露[2]。关于MASH结构的许多研究中都釆用两级运放获得80 dB以上的直流增益,以实现高精度的传输函数,但是这会增加设计的复杂程度。

为了降低器件匹配性造成的影响,文献[2]提出了一种Sturdy-MASH(SMASH)Sigma-Delta调制器,其输出形式如图1中实线部分所示。

调制器移除了后端的数字逻辑结构,在数字域的第1阶段量化器输出时,将第2环路输出反馈到第1环路。信号和噪声传递函数为:

YSMASH=STF1X+NTF1(1-STF2)E1-

NTF1NTF2E2

(4)

当选择STF2=1-NTF2,得到:

YSMASH=STF1X+NTF1NTF2(E1-E2)

(5)

这种结构的优点就是去除数字抵消逻辑从而去除模拟数字间的器件匹配问题造成的噪声泄露,文献[3-6]先后对这种技术进行了研究,但最终的输出中还是会存在第1级的量化噪声。

为了彻底消除第1级量化噪声,文献[7-9]中提出了一种基于延迟的噪声抵消Sturdy-MASH(delay based noise cancelling sturdy MASH,DNC-SMASH)。在这种结构中,第1个环路的输出被延迟1个时钟,延迟的效果由围绕量化器的DAC补偿。DNC-SMASH的输出表达式为:

YDNC=z-1STF1X+NTF1(z-1-STF2)E1-

NTF1NTF2E2

(6)

通过选择,可以完全消除E1。这样输出中只会出现第2级量化噪声,能够很好地增大调制器的噪声整形能力。

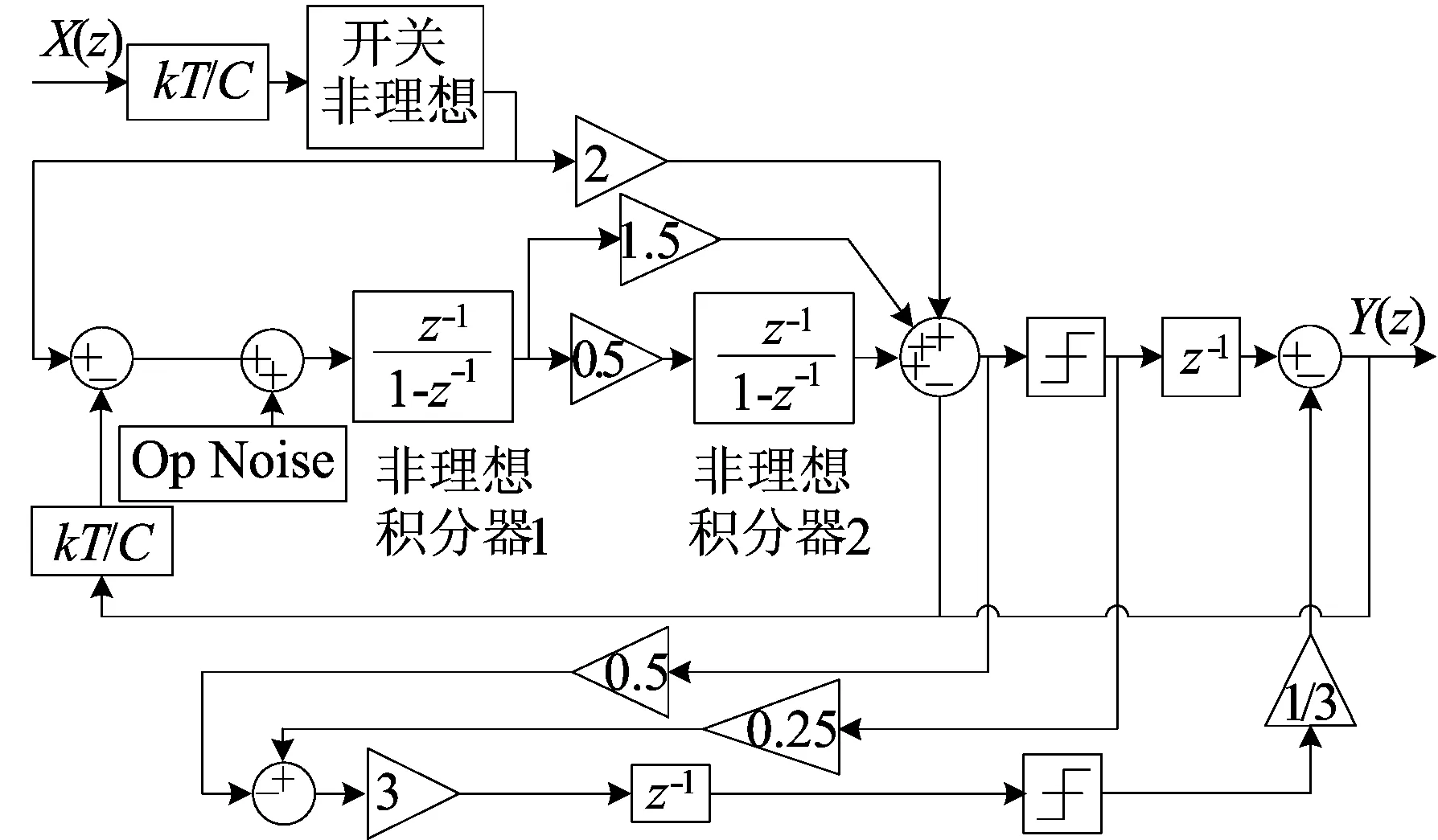

2 新型级联Sigma-Delta调制器

本文提出的级联Sigma-Delta调制器如图2所示。在第2级调制中去除了虚线部分的环路滤波器,通过一个量化器来处理第1级的量化误差。对于DNC-SMASH结构的输出函数的条件STF2=z-1,选择通过一个延迟来实现。调制器在Matlab中的线性模型如图3所示。

图2 DNC-SMASH架构和本文提出的架构

图3 调制器的Simulink建模图

调制器第1级的环路采用低失真的前馈结构,其噪声和信号传递函数表示为:

(7)

(8)

第1级的量化噪声作为第2级的输入,经过延迟和量化器,在第1级的量化输出的数字域中减去,第2级的STF2=z-1、NTF2=1,带入(6)式可以得到最终输出表达式,即

YDNC=z-1X-(1-z-1)2E2

(9)

DNC-SMASH结构中,最后的量化噪声为NTF1NTF2E2,本文的调制器总的量化噪声表示为NTF1E2=(1-z-1)2E2,对于只有2个积分器的Sigma-Delta调制器仍然满足二阶的噪声整形。

对于传统的ADC的量化误差在电路中应是很小的值,但对于Sigma-Delta调制器中一位的量化器,因为一位量化器的输出在高低电平之间跳变,所以将量化误差作为信号,其幅度也在高低电平之间变化,从而不会出现一个非常小的幅值信号被传输到第2个量化器而造成更大的误差输出。同时,级联Sigma Delta调制器中第1级噪声包括许多闲置噪声项,第2级量化噪声更接近真实白噪声。因此这种结构消除了第1级的量化噪声,最终输出中只有第2级的量化噪声,所能达到的信噪比更高。

略去复杂的计算和大量的仿真工作验证,调制器系数最终选择a1=0.5,a2=1.5,a3=2,g1=0.25,g2=0.5,k=3,调制器的整体性能达到理想的效果。在理想情况下仿真,结果显示信噪比达到120.5 dB,有效位数达到19.7 bit。

3 非理想因素分析与仿真

在实际应用中,非理想因素对于电路的影响是不容忽视的,本文在设计Sigma-Delta调制器时要估测非理想因素对实际电路的影响,用于指导模拟电路的设计。本设计中去除了数字逻辑部分,因此对于元件匹配的非理想因素要求不高,只需要考虑到电路的噪声以及运放的非理想等。

3.1 积分器噪声

积分器噪声主要是开关热噪声产生的。在多阶的Sigma-Delta调制器中,第1阶的噪声影响最大,因此主要考虑第1个积分器产生的噪声。假设输入信号的幅度为A,则输入为满幅度的输入功率为SS=A2/2,故而可以得到SNR为:

(10)

由此可见,噪声大小与采样电容CS有关,CS越大,积分器噪声越小,然而,CS的选择还需要综合考虑功耗和速度的问题。通过(10)式可以计算出采样电容的值。本文中M=256,且希望精度达到16位,综合考虑,确定第1级的CS=3 pF,即

(11)

3.2 运算放大器的有限直流增益

运放是积分器中的重要组成部分,在理想状态下,希望运放的增益为无穷大,然而在实际中增益是有限的。对于理想的运放而言,其增益无穷大,基于理想运放积分器的传输函数为:

(12)

而在实际情况中,有限运放的增益导致了积分器存在泄露,这种情况下的传输函数为:

(13)

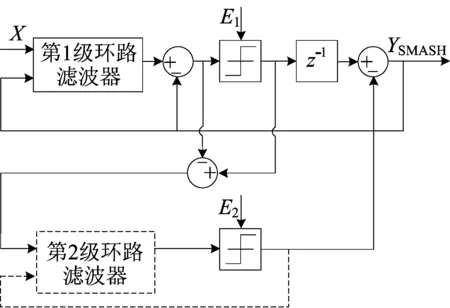

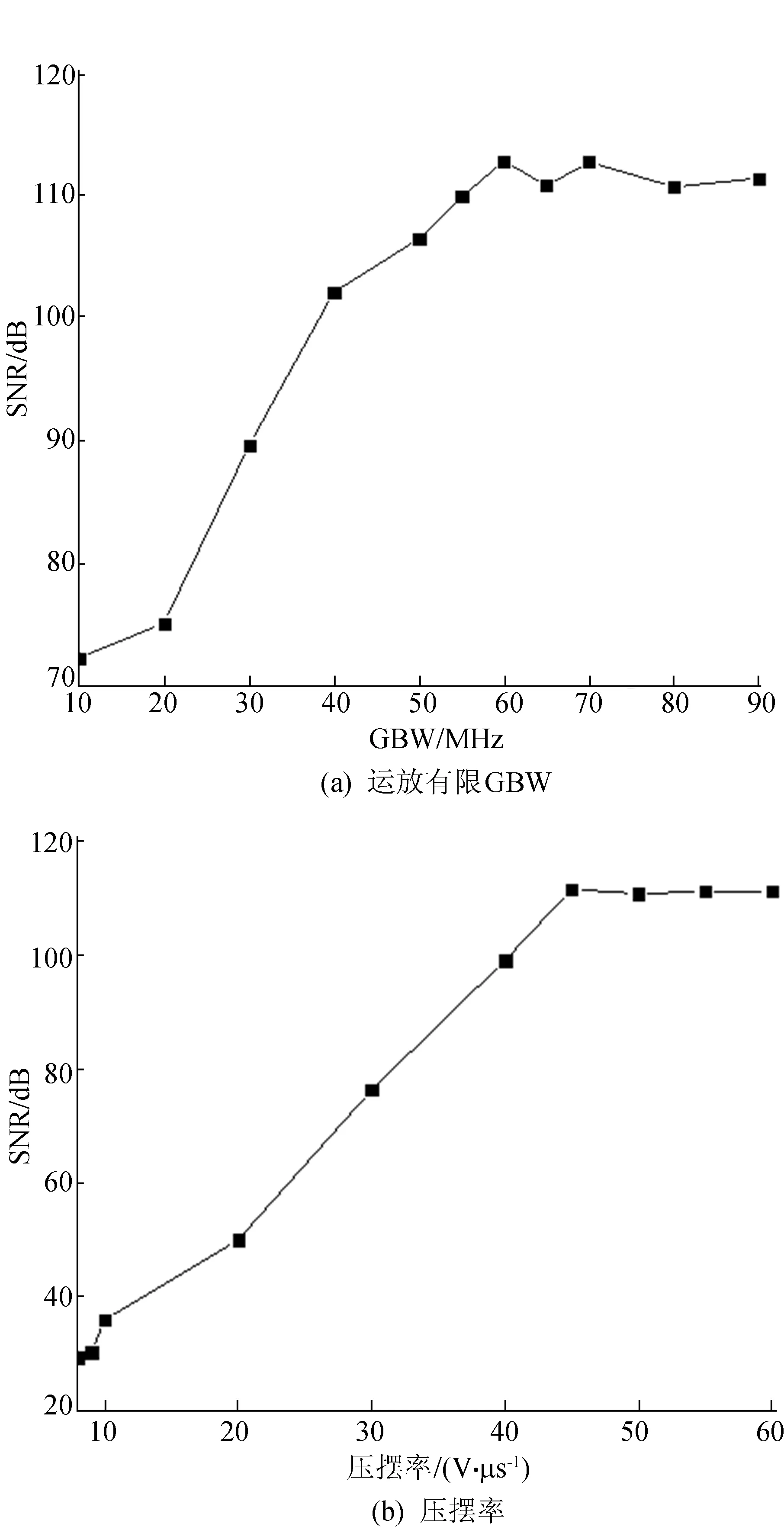

对于积分器而言,如果运放的开环增益不够大,那么就会引起Sigma-Delta 调制器的非线性,进而降低了调制器的SNR,因此在设计电路的过程中要保证运放的开环增益。通过仿真得到运放增益对于Sigma-Delta调制器SNR的影响,加入与文献[10]中的运放增益结果的比较,如图4所示。从图4可以看出,当运放增益达到40 dB,信噪比基本不再变化,而传统2-1级联结构调制器增益需要达到60 dB以上,说明此结构具有SMASH结构的优点,不需要过高的运放来补偿模拟与数字的不匹配。

图4 运放增益对调制器信噪比的影响

3.3 运放的有限增益带宽与压摆率

运放的有限增益带宽积(gain-band width product,GBW)会引起系统的建立产生误差,运放有限GBW造成的积分器建立误差会增加MASH调制器最后一级的量化误差,这与其对单环拓扑结构的影响相同;此外,对MASH结构来说这还会使前一级的噪声残留下来,并泄露到输出。对于运放的非线性建立是由于运放有限的压摆率造成的。非线性建立带来的误差最终表现为失真,对调制器性能的影响较大。通常使运放的压摆率足够大以避免非线性建立带来的误差,但是压摆率越大,需要的电流也就越大,则功耗也越大。

调制器的信噪比与运放的有限增益带宽和压摆率的关系如图5所示,该结果是通过仿真验证得到的,当有增益带宽增加到60 MHz时、压摆率增加到45 V/μs时,信噪比基本不再变化。

图5 运放有限和压摆率对调制器信噪比的影响

4 仿真结果

整个Sigma-Delta调制器加入非理想因素的行为级仿真的模型如图6所示。

图6 调制器加入非理想因素的Simulink模型

综合对非理性因素的分析,非理想因素的取值如下:运放有限直流增益为40 dB,有限增益带宽为60 MHz,压摆率为45 V/μs,采样电容为3 pF。

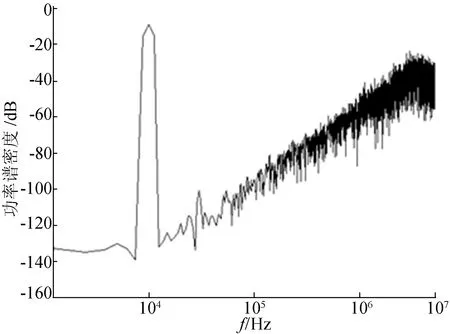

本文级联Sigma-Delta调制器在加入非理想因素情况下的输出频谱图如图7所示,加入非理想因素时调整器的SNR达到110.5 dB,有效位数达到18.06 bit。仿真结果说明,本文的级联Sigma-Delta调制器的性能与2阶Sigma-Delta调制器相比,SNR已经超过其理论值。而且这种结构还继承了SMASH结构的优点,不需要高增益的运放来补偿模拟与数字间的不匹配,积分器运放的增益仅需40 dB就能满足电路高精度的需求。

图7 加入非理想因素的调制器输出PSD

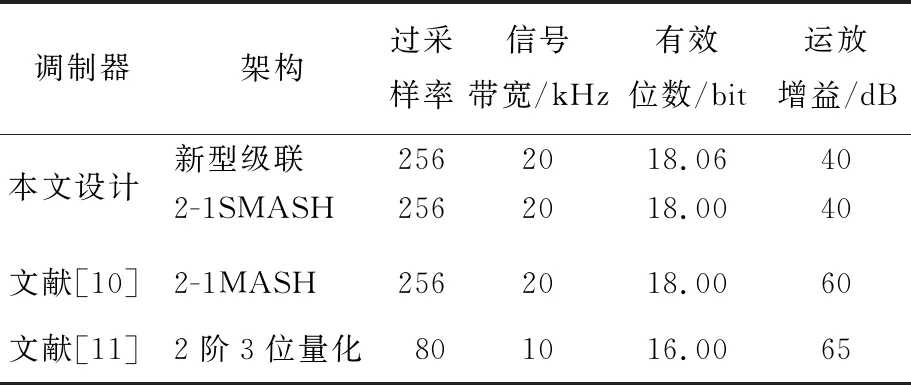

本文提出的新型级联结构与传统的2阶、2-1级联以及本文搭建的2-1 SMASM结构Sigma-Delta的性能对比见表1所列。

表1 几种调制器的性能对比

本文中的级联Sigma-Delta调制器对比于传统2阶和2-1级联结构Sigma-Delta调制器在性能上有明显的优势。

5 结 论

本文基于Matlab Simulink设计了一款新型的级联结构的Sigma-Delta调制器,以二阶Sigma-Delta调制和额外的量化器级联,达到了更好的噪声整形效果。仿真结果表明,当输入信号带宽为20 kHz,过采样率为256时,理想调制器有效位数高达19.72 bit,考虑非理想因素后有效位数为18.06 bit。仿真结果相比于二阶Sigma-Delta调制器实现了更高的精度。