一种高效的源同步总线收发编码方法

徐磊 纪小明 赵永春

摘要:源同步串行总线是FPGA片间互连的常用方式。针对传统的源同步串行总线传输方法对线路的利用率不高的情况,提出了一种高效的源同步总线收发编解码方法,可以显著提高源同步串行总线的传输效率。

关键词:FPGA;源同步;编码方法

0 引言

现场可编程门阵列(FPGA)是近年来快速发展的新型可编程逻辑器件,主要应用于集成电路的定制电路开发验证[1]。在数字系统中,多片FPGA互连传输数据需要稳定高效的接口,源同步串行总线是FPGA片间互连的常用方式。源同步系统中每两个部件之间数据进行单向或双向传递,在和数据同向的传递方向上同时传递一个和数据保持特定相位关系的参考时钟,在数据的源端,参考时钟和数据保持确定的相位关系,而在数据的目的端,另外一个部件可根据参考时钟的相位来准确捕获对应的数据[2]。系统采用源同步机制,可以允许发送端在数据信号线或时钟信号线上出现周期性或随机的信号抖动,即使数据或时钟因为抖动出现偏差,只要确保两者的时序关系保持一致就可以保证收端获得正确的信号[3]。

FPGA片间有传输数据需求时,传统的源同步串行总线编码方法,以n根线路传输m位宽数据为例,n根线路中固定一路传输随路时钟,再选一路传输高有效的同步脉冲,同步脉冲指示传输的有效数据的起始,再将m位宽数据进行并串转换并依次序平铺在剩余的n-2根线路上,易知并串转换后数据长度为ceil[m/(n-2)],其中ceil为向上取整。接收端进行解码时,使用随路时钟采集同步脉冲的状态,当检测到高有效的同步脉冲时,认为接收到了有效数据的低位,开始对串行的有效数据进行缓存,逐次接收数据,在第ceil[m/(n-2)]次时,串行有效数据全部接收完毕,此时再串并转换就最终恢复出m位宽数据。传统的源同步串行传输方法如图1所示。

显然,传统的源同步串行总线传输方法,连续传输的最小间隔为ceil[m/(n-2)],即数据传输延迟。

1 高效的源同步总线收发编解码方法

传统的源同步串行总线传输方法对线路的利用率并不高,尤其是同步脉冲这一路并未参与有效数据的传输,为了提高线路利用率,减小连续传输的最小间隔(传输延迟),本文提出了一种高效的源同步总线收发编解码方法。

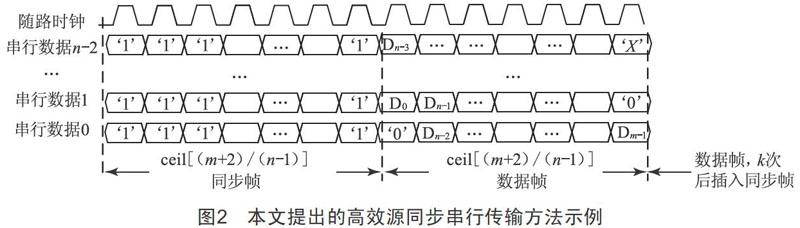

以n根线路传输m位宽数据为例,n根线路中固定一路传输随路时钟,剩余的n-1路全部用来传输有效数据,同时将有效数据分为数据帧和同步帧两种类型。本文提出的高效源同步串行传输方法原理如图2所示。

数据帧的设计:m位宽数据在最低位和最高位之外分别增加一位“0”,形成m+2位宽数据,将m+2位宽数据进行并串转换并依次序平铺在剩余的n-1根线路上,并串转换后串行数据长度为ceil[(m+2)/(n-1)]。

同步帧的设计:同步帧与数据帧的长度保持一致,也为ceil[(m+2)/(n-1)],同步帧的数据全部为“1”。

发送端在首次传输数据帧之前先发一次同步帧,之后每隔ceil[(m+2)/(n-1)]长度传输1次数据帧,在连续发k次数据帧后插入一次同步帧,后续按k次数据帧插入一次同步帧的规律持续发送。同步帧的插入确保接收端同步性的判断和维持,插入间隔k可设置为100万次。

接收端使用随路时钟采集其余n-1线路的状态,每次对连续的ceil[(m+2)/(n-1)]长度串行数据进行判断,如果其内容全部为“1”则检测到了同步帧。数据帧是由“0”作为起始和结尾的,故这样检测得到的同步帧是唯一的。检测到同步帧后,对后续的连续k次ceil[(m+2)/(n-1)]长度串行数据做串并转换,并舍弃起始和结尾的“0”就得到了最终的有效数据。k次之后驗证接收到的是否是同步帧,若是则说明总线传输稳定,接收的数据正确可靠,若否则说明总线出现传输错误。验证了同步帧后,按k次数据帧接续1次同步帧的规律对总线进行有效数据的提取和同步性验证。

由上述设计可知,本文提出的高效源同步总线收发编解码方法,连续传输的最小间隔和传输延迟为ceil[(m+2)/(n-1)],相比传统方法有显著提升,并引进了错误检测机制。

2 效果对比

本文提出的编码方法能显著提高源同步总线的传输效率,具体以5线传输64 bit数据为例,传统源同步串行传输方法如图3所示。源同步时钟用1根线,数据同步有效标志用1根线,64 bit并行数据经过并串转换需要ceil[64/(5-2)]=22个时钟节拍传输,因此连续传输间隔为22个时钟周期。

5线传64 bit数据的高效源同步串行传输方法如图4所示。源同步时钟用1根线,其余4根线全用于有效数据的传输。数据帧的长度为ceil[(64+2)/(5-1)]=17,同步帧的长度与数据帧相同。同步帧的插入间隔在源同步条件下可以比较大,比如10 000次数据帧后插入1次同步帧,因此同步帧的影响可以忽略不计,从而线路资源全用于有效数据的传输。

设随路时钟为150 MHz,周期为6.66 ns,则2线传输28 bit数据包的传输效率对比如表1所示。新编码方法在线路资源不变的情况下,传输效率提升了29%。

3 结语

源同步高速接口使用并行链路连接,以时钟和多位数据相伴传输,解决了接收方的数据同步问题[4]。针对传统的源同步串行总线编码方法效率不高的情况,本文提出了一种更高效的编码方式,该方式可以充分利用线路的带宽资源,显著提升数据传输速率。

[参考文献]

[1] 卿启新.基于FPGA的LVDS视频信号转换系统设计实现[D].广州:华南理工大学,2011.

[2] 顾峰,吕余清.应用源同步技术实现高速ADC与FPGA互连[J].电子技术,2016(10):30-33.

[3] 张骅.源同步接口芯片的测试[J].集成电路应用,2003(10):62-64.

[4] 许勇.一个源同步高速接口的设计[J].高性能计算技术,2003(4):29-33.

收稿日期:2020-08-03

作者简介:徐磊(1987—),男,陕西西安人,硕士研究生,工程师,研究方向:电子对抗技术。