基于PCI总线的RS232串口通信设计与实现

田成富 汪鹏志

摘要:在针对国防工业、导航、通信等领域中,广泛使用串行接口UART与外围设备进行通信。提出了一种基于PCI总线的8路异步传输标准的设计方案,该方案采用专用芯片XR17D158作为从设备挂接在MPC8280的PCI总线,实现PCI-232 接口的硬件结构方案,并在VxWorks系统下开发设备驱动程序。本文重点分析了所用芯片的功能、硬件设计、寄存器配置,并给出了VxWorks操作系统下驱动程序的具体实现方法。

Abstract: In the field of defense industry, navigation, communication, power and so on, it widely uses serial interface Universal Asynchronous Receiver/Transmitter (UART) to communicate with peripheral equipment. This paper presents a design plan for 8 asynchronous transmission standard based on PCI bus, which adopts the special chip xr17d158 as a slave device mount to peripheral component interconnect(PCI) bus of MPC8280, acieve the hardware structure scheme of the PCI-232 interface, and develops the device driver in the VxWorks system. This paper focuses on the function, hardware design, register configuration of the used chip, and gives the implementation method of the driver in the VxWorks operating system.

关键词:UART;PCI总线;VxWorks系统

Key words: UART;PCI;VxWorks system

中图分类号:TN958 文献标识码:A 文章编号:1006-4311(2020)28-0160-03

0 引言

伴随著通信行业的不断发展,越来越多的计算机或设备通过不同通信接口实现互连互通,实现信息共享和设备的集中控制与管理,其中串口通信具有结构简单、线路成本低、实时性强、可靠性高等优点,被广泛应用到各个领域[1]。因此多串口扩展已成为通信设备接入的重要手段。PCI总线作为基于PCI电气规范开发的高性能工业总线,广泛应用于工业控制、通信及网络等领域。由于大部分I/O设备不具备PCI总线功能,开发具有多端口通用串口和PCI总线的接口卡成为技术发展的必然要求。本系统采用专用集成芯片XRl7D158开发了基于PCI总线的8路RS-232高速串行通讯卡,为通信设备提供额外的高性能串行接口,适用于连接各类串行设备,实现数据的高效交互。

1 系统硬件设计

本文采用Exar公司推出的一种兼容3.3V和5V的专用芯片XRl7D158[2],该芯片支持8路UART通道转换PCI总线的功能,通过多路串行接口扩展可减少系统开销、节约印制板空间。该通信模式满足PCI2.3规范,工作频率33MHz,32位的数据总线能充分利用CPU带宽,实现大量数据的同步传输。为满足多接口实时并行上传下载信息,每个通道都拥有可编程触发电平的64字节发送/接收缓冲FIFO,通过参数配置可分别实现921.6kbps波特率的传输速率。基于MPC8280主控与XR17D158的硬件接口框图如图1所示。

图中信号按功能划分可分为:地址/数据线、接口控制信号、系统信号三种。

①地址/数据线:PCI_AD31-0为地址/数据多路复用的输入/输出信号;PCI_C/BE3-0为总线命令和字节使能多路复用信号;PCI_PAR为奇偶校验信号,用于对PCI_AD31-0和PCI_C/BE3-0信号进行奇偶校验。

②控制信号:PCI_FRAME为帧周期信号,表示一次数据传输的开始与持续时间;PCI_TRDY为主设备准备就绪信号,PCI_IRDY为从设备准备就绪信号,表示芯片数据传输就绪,需要与PCI_TRDY配合使用;PCI_DEVSEL为设备选择信号,表示选定该从设备;PCI_IDSEL为初始化设备选择信号,表示参数读写配置期间,从设备被选定;PCI_INTA为中断线,用以请求一个中断事件。

③系统信号:PCI_CLK为时钟信号;PCI_RST为复位信号。

2 XR17D158寄存器配置

XR17D158具有三种不同的寄存器组[3]:PCI局部总线配置寄存器、设备配置寄存器,串口配置寄存器其功能特性如图2所示。

2.1 PCI局部总线配置寄存器 主要包含设备号、厂家号、版本号、奇偶校验、存储基地址、中断引脚等相关信息。系统上电后,主控MPC8280根据PCI总线上读取的XR17D158插卡信息为从设备XR17D158分配相应的存储地址与空间、端口地址和中断号等参数,实现即插即用的自动参数配置。其中基地址寄存器BAR作為重要配置参数存储在0x10地址空间,其高20位BAR[31-12]作为设备配置寄存器和串口配置寄存器的基地址。中断线寄存器位于0x3C地址空间,主要存储芯片挂接的物理中断号。XR17D158的相关信息也可保存在外接EEPROM中,系统上电后XRl7D158检测EEPROM是否有效,并读取EEPROM中相关信息用来标识PCI卡。其中,局部总线配置寄存器大部分具有只读功能。

2.2 设备配置寄存器 主要存储中断配置、定时/计数控制与状态、软件复位、休眠、工作模式、复用功能输入输出配置以及设备标识和版本号等相关信息。设备配置寄存器地址由基地址寄存器BAR和偏移量组成,偏移量范围为0x80-0x93。XR17D158的8路串口可分别工作在8x和16x采样率的模式,通过配置工作模式寄存器8xMODE,可选择各串口的采样率。通过对REGB寄存器的位操作,控制XR17D158中IIC总线的输入输出,实现对外接EEPROM的读写操作。

2.3 串口配置寄存器 主要包含兼容16550规范的控制/状态寄存器和64深度的发送/接收缓冲FIFO,每路串行接口都有独立的UART配置寄存器作为串行数据传输控制和状态信息指示,对于串口UARTn而言,其寄存器偏移量为0x200*n(n=0~7)。主要实现各串行通信的波特率设置、中断使能与状态指示、数据发送与接收、工作模式设置与检测等功能。设备配置寄存器和串口配置寄存器共占4K的PCI总线存储器地址空间。

当外部输入时钟为14.7456MHz时,通过配置可编程波特率发生器(BRG),利用公式(1)可实现最大波特率921.1kps传输。本文为实现115200波特率的传输速率,选择4倍预分频系数,即预分频系统寄存器MCR[7]=1;16X采样率,即采样模式寄存器8xMODE[x]=0;分频因子2,即分频因子寄存器DLM=0x00、DLL=0x02。

(1)

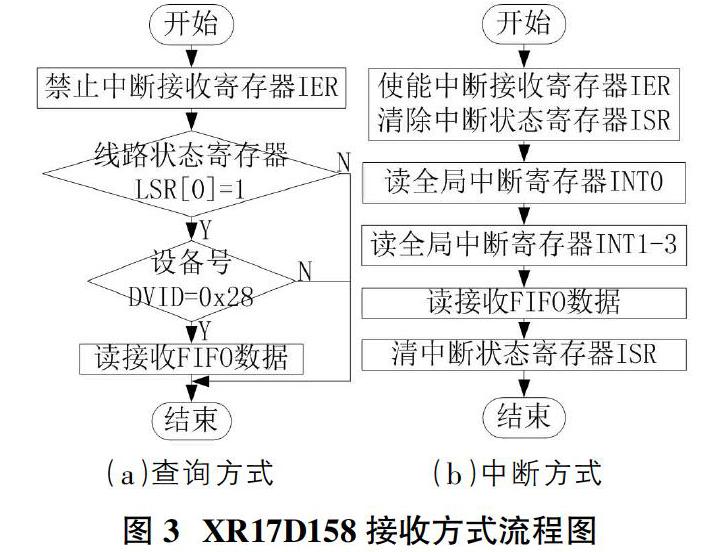

XR17D158支持在映射的存储器地址进行PCI突发模式读/写操作。①读操作主要由接收移位寄存器RSR和接收保持寄存器RHR组成。RSR用于检测每一位数据的有效性,当检测到停止位时,表明一个有效数据接收完成,并将完整数据载入RHR中,将中断状态寄存器ISR或线路状态寄存器LSR置位,以便主控设备对RHR中数据进行处理。因此,XR17D158可采用中断方式和查询方式从PCI总线接收数据,其设计流程如图3所示。②写操作由输出移位寄存器TSR和发送保持寄存器THR组成,当有效数据由主机写入THR后,再由发送控制逻辑加上起始位、奇偶校验位和终止位存入TSR,并按设定的波特率将数据逐位移出。

查询接收方式设计流程:

①先失能串口中断IER=0,禁止所有中断,使串口工作在查询模式;

②读取线路状态寄存器LSR[0]位,判断数据是否从PCI总线上接收数据保存在接收保持寄存器RHR;

③读取设备号DVID,判断设备号是否为XR17D158特有的设备号0x28,如此重复。因此采用查询方式时需要创建任务定时对线路状态和设备号进行查询判断。

中断接收方式设计流程:

①先使能串口FIFO接收中断IER[0]=1,同时清除中断标志位ISR=0;

②读取全局中断寄存器INT0,判断哪个通道触发中断;

③读取全局中断寄存器INT1-3,判断中断源触发类型;

④当满足FIFO中断时,读取缓冲区数据。并清除中断状态。以中断方式接收数据时,当中断产生后,程序直接进入中断入口函数执行,该方式具有效率高,及时性强等优点。

3 软件设计

3.1 驱动程序设计

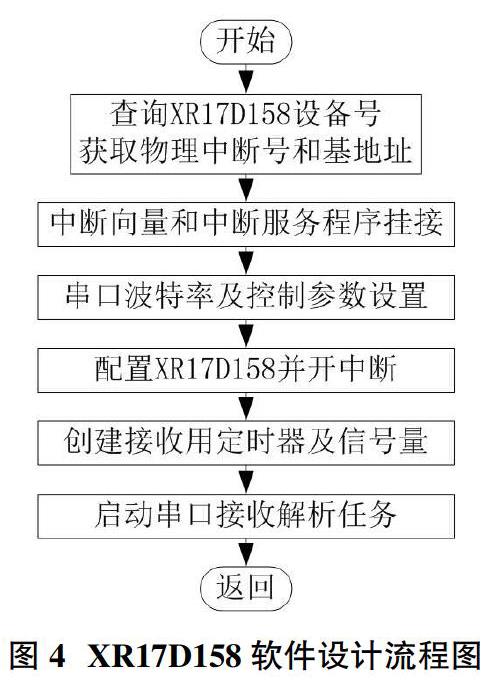

本设计采用具有多任务、可扩展、组件化的VxWorks操作系统,与Linux操作系统相比具有实时性强、及时处理多任务调度的优点[4]。内核采用操作系统自带MPC8280的板级支持包移植而来,其软件设计基本流程如图4所示。

在PCI总线上有MPC8280和XR17D158两种设备,各设备具有独一的设备号,因此调试阶段可调用pciDeviceShow()函数,打印PCI总线上所有设备号等信息。在实际软件设计过程中,通过调用pciFindDevice (D158_VID, D158_DID, index, &bus, &dev, &func)查询挂接的XR17D158设备[5]。调用sysPciConfigRead (bus, dev, func, 0x3c, 1, &bIntNum)和sysPciConfigRead (bus, dev, func, 0x10, 4, &uMemBase)获取芯片挂接的物理中断号和分配的基地址。其中物理中断号用于中断向量和中断服务程序的挂接,基地址用于定位各串行接口的寄存器组,实现对波特率和控制参数的配置,XR17D158的PCI配置空间的初始化基本完成。

XR17D158作为具有PCI总线的多串行接口芯片,在驱动设计中可将底层函数封装后以标准串口驱动进行调用,具有较好的灵活性,主要实现的函数如下:

①cmsIoctl()通过传入参数对串口驱动进行控制,包括波特率设置与获取、工作模式设置与获取、回调函数与参数设置、数据长度与格式的定义;

②cmsPollInput()轮询读取串口中数据,便于应用程序调用read()接口读取数据;

③cmsPollOutput()采用轮询方式发送串口数据;

④cmsTxStartup()用于中断函数使能发送;

⑤cmsCallbackInstall()用于传递安装中断回调函数与参数。

XR17D158的驱动函数以标准串口模式封装后,对XR17D158的操作可以按标准串口进行操作,具体步骤如下:

①初始化XR17D158中相关寄存器和配置函数,调用ttyDrv()安装驱动程序到I/O系统;

②根据系统所指定的串口号(/tyCo/x),调用ttyDevCreate()为系统添加指定串口;

③串口初始化完成后,调用open()函数打开对应串口;

④根据open()函数返回的文件句柄,调用read()和write()函数对串口进行读写操作,串口的初始化由传入ioctl()函数的参数决定,主要配置如下:1)调用ioctl(fd, FIOBAUDRATE, baud)配置串口的波特率;2)调用ioctl(fd, FIOSETOPTIONS, OPT_RAW)配置串口数据传输模式;3)调用ioctl(fd, SIO_HW_OPTS_SET, CREAD | CS8 | CLOCAL)配置串口一帧数据的格式。

3.2 测试验证

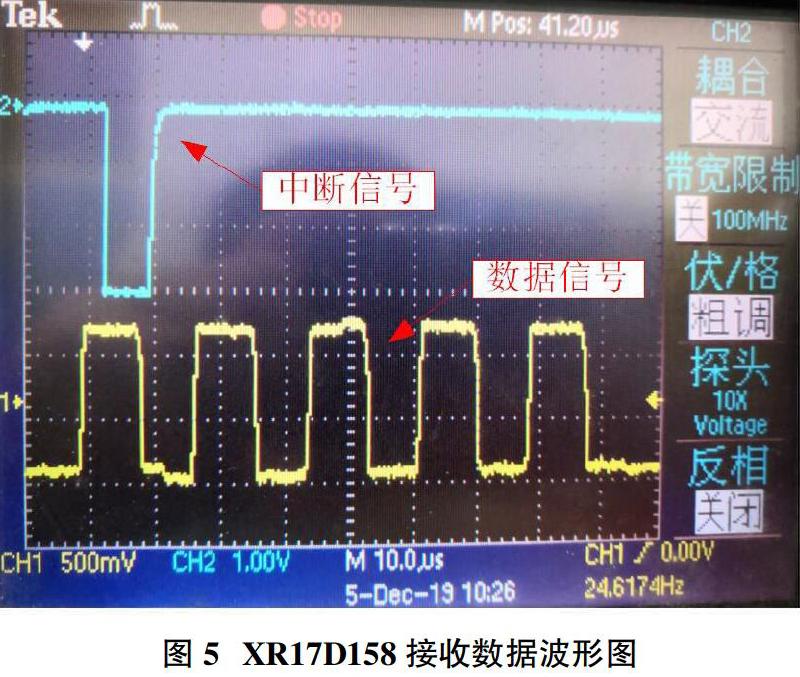

利用外部设备以115200bps的速率向8路串口发送测试数据,时间间隔为100ms。通过示波器对其中一路传输数据观察如图5所示。

图中CH1为XRl7D158接收数据波形,CH2为INTA的中断信号。可知,当INTA为低电平时触发中断,XR17D158开始接收串口数据。一帧数据用时80us,其中包含一位起始位、八位有效数据位、一位停止位,满足波特率115200bps的传输速率。通过对8路串行通道,2小时的测试验证,未出现误码和丢包现象,满足通信设备对串口稳定性的运行要求。

4 结论

本文利用XRl7D158芯片实现PCI总线和8路串口之间的通信,弥补传统主控器中串行通信接口少的局限性,利用一卡多用实现多路设备的高频率通信避免一般通信设备转接复杂,设计繁琐等缺陷。基于XRl7D158设计的适配卡具有结构紧凑,通信距离长,最多可支持8路设备接口,解决了大部分I/O设备没有PCI总线接口的问题,在现实中具有广阔的应用前景。

参考文献:

[1]何秋婭,徐学军.基于VxWorks的串口服务器研究与实现[J].计算机应用与软件,2015,32(9):223-226.

[2]安彦波.工业机器人开放式控制系统的研究[D].哈尔滨工业大学,2010:38-40.

[3]冯毅.基于WinDriver的多路串行设备驱动开发[J].电子技术,2014,6:61-63.

[4]邝安玄,刘明,朱守园.VxWorks下串口设备驱动设计与实现[J].航空计算技术,2018,48(4):78-81.

[5]孙广明,唐建.基于高可靠CPCI接口的4通道串口设计[J].电子设计工程,2017,25(23):90-93.

基金项目:船舶工业国防科技预研基金资助项目(6141B04050101)。

作者简介:田成富(1986-),男,河南周口人,工程师,硕士,研究方向为无线通信、网络通信。