基于XC3S1600E的以太网远传模块实现

王少龙

(中国长城科技集团股份有限公司,湖南 长沙 410006)

0 引言

本文给出了完全用现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)的控制逻辑来实现以太网控制器及远传模块的封装与解析,其中,以太网控制器符合IEEE802.3标准,远传模块遵循高级数据链路控制(High-level Data Link Control,HDLC)协议,并通过软件实现100 M以太网和8 M远传接口之间的流量控制[1]。

1 总体设计方案

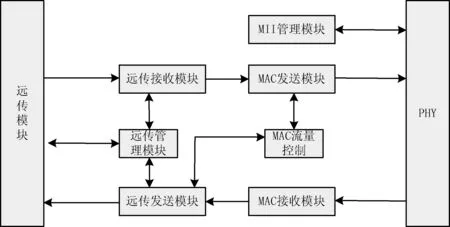

以太网远传模块的FPGA设计工作包括:(1)以太网MAC子层的FPGA设计;(2)MAC与物理层(PHY)的MII接口设计;(3)远传接口HDLC协议的FPGA封装与解析;(4)以太网与远传模块之间流量控制的设计。总体结构设计框架如图1所示。

图1 以太网远传模块的结构设计框架

该以太网远传模块的整个系统包括:以太网MAC发送处理模块、以太网MAC接收处理模块、以太网MAC流量控制模块、MII处理模块、远传发送模块、远传接收模块、远传管理模块[2]。

(1)MAC发送处理模块和MAC接收处理模块,主要完成MAC帧的发送和接收处理,主要实现MAC帧的封装、解析、错误检测,模块与外部物理层芯片(PHY)之间通过并行数据接口(MII)相连。(2)MAC流量控制模块,实现了MAC全双工模式中的流量控制功能,完成MAC与远传模块之间的流量控制。(3)MII管理模块提供了介质独立接口(MII),符合标准的IEEE802.3标准,主要对PHY芯片BCM5461S进行初始化。(4)远传发送模块,主要执行HDLC帧的发送,包括将从MAC接收到的数据帧封装成HDLC格式的帧,并向MAC流量控制报告发送缓冲区的状态;远传接收模块主要执行HDLC帧的接收,将从远传接口接收到的HDLC格式的帧进行HDLC协议解析以及错误检测,并将解析后的数据帧发送到MAC发送模块。(5)远传管理模块,用来管理远传的速率、主从模式设置等。以太网远传模块的应用连接如图2所示。

图2 以太网远传模块的应用连接

2 MAC发送模块

MAC发送模块将从远传接收模块接收到的数据,进行MAC层协议封装,并将封装好的数据包通过MII接口发送给PHY[3]。MAC帧结构如表1所示。

由于本项目中和以太网站点之间收发数据是全双工模式,因此,在MAC发送模块中无须载波帧听和冲突检测,MAC发送模块从远传接收模块接收到数据帧开始标志后,从远传接收模块中的接收FIFO中读取要发送的数据,当从远传接收模块接收到数据帧结束标志后,表示当前读取的数据包读取完毕,MAC发送模块对数据进行MAC层协议封装,并将数据转换为4位宽度的并行数据,通过MII接口发送给PHY,最后,由PHY将数据发送到网络上[4]。

表1 MAC帧结构表

MAC发送模块由CRC生成模块(crc_gen)、发送计数模块(tx_cnt)和发送状态机(tx_statem)模块等组成,其内部结构如图3所示。

图3 MAC发送模块结构框架

2.1 CRC生成模块(crc_gen)

CRC生成模块对发送数据进行CRC计算,将产生的32位CRC校验值填写到数据帧的帧校验序列字段(FCS)内。由于MAC模块与PHY接口之间为4位并行接口。为了提高效率,设计时,使用4位并行CRC计算,算法中通过使用次态函数,并通过循环迭代进行移位操作。使用4位并行CRC计算方法,发送模块可以一边发送数据到PHY,一边计算CRC。当数据发送完成后,紧接着发送计算完成的CRC校验值。

2.2 发送计数模块(tx_cnt)

发送计数模块由前导码计数器、MAC帧长度计数器、帧填充计数器、帧间隙计数器组成。其中,前导码计数器用于控制MAC帧前导码的发送,MAC帧的前导码由7个字节的0×55和一个字节的0×d5组成;MAC帧的长度计数器用于计数MAC帧的发送长度,MAC帧的最小长度为64字节,其中,校验位共4个字节,当MAC帧的长度小于64字节时,就要进行帧填充;帧填充计数器用于计数填充位的位数;帧间间隙周期大于等于96个比特时间,帧间隙计数器用于计数帧间间隙周期。

2.3 发送状态机模块(tx_statem)

发送状态机模块完成MAC发送过程的控制,是MAC发送模块的核心。发送状态机由空闲状态(Idle_State)、前导码发送状态(Preamble_State)、数据发送状态(Data_State)、填充码发送状态(PAD_State)、校验位发送状态(FCS_State)、帧间间隙状态(IPG_State)、延迟状态(Defer_State)等8个状态组成。MAC发送状态的状态转意如图4所示。

图4 MAC发送状态转移

发送模块的初始状态为延迟状态;在延迟状态下,若信道空闲,则状态机进入帧间间隙状态,在帧间间隙状态等待一个帧间间隙后,如果在帧间间隙的前2/3个周期检测到信道忙信号,状态机将重新回到延迟状态,否则状态机进入总线空闲状态。

状态机进入总线空闲状态之后,MAC发送模块一直检测远传接收模块是否有发送请求,判断远传接收模块是否有数据要发送到以太网接口。如果检测到远传接收模块的发送请求,状态机就进入前导码状态,开始发送前导码,前导码由7个字节的0×55组成;前导码发送完毕后,发送一个字节的帧起始定界符,帧起始定界符为0×d5。发送完前导码和帧起始定界符后,状态机进入数据发送状态,MAC发送模块每次从远传接收模块的FIFO中读取一个字节,并先将该字节的低4位发送到MII接口、再将高4位发送到MII接口,当读取发送数据帧的最后一个字节时,根据数据帧的长度,状态机将进入到校验状态或者填充状态。

如果数据帧的长度在发送范围内(64≤L≤1 518),状态机就进入校验状态。在校验状态,发送模块发送CRC生成模块计算出的CRC值。FCS字段的CRC值发送完后,该MAC帧发送完成,状态机进入延迟状态,重新进入初始状态,等待新的发送请求。

如果数据帧的长度小于64个字节,状态机就进入填充状态,发送模块发送填充码,满足最小帧长度后,状态机进入校验状态。若数据帧的长度大于1 518字节,发送模块将放弃该帧的发送,状态机直接进入延迟状态,重新进入初始状态,等待新的发送请求。

3 MAC接收模块

MAC接收模块主要完成MAC帧的接收处理。将从外部PHY接收到的4位并行数据转换为8位并行数据,对转换后的数据进行MAC协议解析、前导码检测、地址识别、CRC校验、长度判断等操作后,将正确接收的数据移除前导码和CRC值后,通过远传发送模块接口写入远传发送模块的发送FIFO中,并通知远传发送模块帧起始和帧结束信号。

MAC接收模块由4个部分组成,包括:CRC校验模块、地址识别模块、接收计数器和接收状态机模块等,MAC接收模块的结构框架如图5所示。

图5 MAC接收模块框架

CRC校验模块与CRC生成模块算法相同,CRC校验模块对接收的数据进行CRC计算,并通过检查输入帧的CRC值来验证帧的正确性。

地址识别模块完成接收帧目的MAC地址的识别,若目的MAC地址匹配上,则该帧被接收,否则,帧将被丢弃。

接收计数器模块主要对接收字节及帧间间隙进行计数,包括接收字节计数器(Byte_cnt)和帧间间隙计数器(IFG_cnt)组成。在接收帧过程中,接收字节计数器将对接收字节进行计数,通过该计数器识别帧中的各个字段,如前导码、目的地址字段、数据、校验等,也可以完成帧长的判断。帧间间隙计数器对两帧之间的间隔时间进行计数, IEEE802.3规定,两帧之间的间隔至少96个比特间隔。因此,如果两帧之间的间隔小于96个比特间隔,帧将被丢弃。

接收状态机完成MAC接收过程的控制,是MAC接收模块的核心。接收状态机由空闲状态(Idle_State)、前导码状态(Preamble_State)、帧起始定界符状态(SFD_State)、数据接收状态(Data_State)、丢弃状态(Drop_State)等5个状态组成,其状态转移如图6所示。

图6 MAC接收状态转移

状态机的初始状态处于空闲状态,在该状态下检测接收数据有效信号。接收模块检测到接收数据有效信号为“1”,且接收数据为0×55后,状态机跳转到前导码状态,否则为空闲状态。在前导码状态若数据有效信号为“1”,且连续接收7个0×55后,状态机进入帧起始定界符状态,否则,跳转回空闲状态。

在帧起始定界状态,若数据有效信号被清零,跳转回空闲状态;若数据有效信号为“1”,且接收数据为0×d5,则根据帧间间隙计数器的值进入不同的状态。如果帧间间隙所确定的时间大于96个比特时间,则状态机进入数据接收状态进行数据接收,直到数据接收完毕后进入空闲状态,以重新等待接收新的数据;如果帧间间隙计数器所确定的间隔小于96个比特时间,则状态机将进入丢弃状态,并一直维持丢弃状态直到数据有效信号结束(MRxDV信号为0)。之后,状态机再回到空闲状态等待新的数据接收。

4 MII管理模块

MII管理模块完成MAC与外部PHY之间的接口管理,主要完成对PHY芯片的配置或者读取PHY芯片的状态信息。MII接口主要包括:时钟信号MDC、双向数据信号MDIO。时钟信号MDC利用系统时钟分频产生,在本项目中,MDC选用6 M。利用移位寄存器对PHY的控制数据进行写入操作或者对PHY的状态信息进行读出操作,当对PHY的控制数据进行写入操作时,移位寄存器将待写入的控制数据进行并串转换;而在读状态信息时,移位寄存器将读取出数据进行串并转换。

5 远传模块程序设计说明

5.1 远传管理模块

远传管理模块主要设置远传模块的速率以及远出模块的主从模式。远传模块的速率有128 Kbps,256 Kbps,512 Kbps,1 Mbps,2 Mbps,4 Mbps,8 Mbps等8种速率,在本文的应用中,远传模块的速率为8 Mbps。

5.2 远传接收模块

远传接收模块从远传接口上接收到的数据遵循HDLC协议格式,因此,远传接收模块要对接收到的数据帧进行HDLC协议解封装,将解封装后的数据存放在远传接收FIFO中,并向MAC发送模块提供帧开始、帧结束信号。远传接收模块的程序框架如图8所示。

图8 远传接收模块程序框架

HDLC的帧起始和结束标志都是 “7E”(01111110),在起始和结束标志之间为数据字段和帧校验序列。为了避免将数据中的“7E”误为标志,在发送数据时,要进行“插零”操作,即连续5个“1”后要插入一个“0”;在接收数据时,要进行“删零”操作,即要将接收到的5个“1”后面的“0”删除掉。HDLC采用生成多项式为x16+x12+x5+1的CRC算法进行帧校验,对除了插入的“0”以外的所有数据进行校验。

HDLC协议解封装的过程:在接收的数据流中检测帧起始和结束标志;当检测到数据流中有连续5个“1”时,对数据进行“删零”操作,即将5个“1”后面紧随的“0”删除掉;把接收的串行数据转换为并行数据,并存入接收FIFO中;对经“删零”后的数据进行CRC校验,当接收到完整的一帧,检查CRC校验值是否正确,若正确,则向MAC发送模块产生发送请求;若CRC校验失败,则将该帧数据丢弃。HDLC的基本帧结构如表2所示。

表2 HDLC帧结构

5.3 远传发送模块

远传发送模块完成的功能是将从MAC接收模块接收到的数据帧存放在远传发送FIFO中,将存放在发送FIFO中的数据读取出来,并进行HDLC协议封装,将封装后的数据串行发送到远传线路上。远传发送模块的程序框架如图8所示。

图8 远传发送模块

HDLC协议封装的过程:首先,发送帧起始标志“7E”;其次,发送数据段,并对发送数据逐位做CRC计算,数据发送完毕后,发送计算出的16位CRC校验值。在协议封装时,需要对包括CRC计算值在内的数据进行“插零”操作,即连续5个“1”后面需要插入一个“0”;数据和CRC值发送完毕后,发送帧结束标志“7E”。

6 以太网模块与远传模块之间流量控制

在本应用中,以太网模块的传输速率为100 Mbps,而远传模块的传输速率最高为8 Mbps,因此,要想数据能够正确、可靠传输,需要在两者之间增加流量控制。流量控制可以通过缓存FIFO或者MAC的PAUSE控制帧来实现。本应用中,流量控制通过发送和接收MAC控制帧——PAUSE帧来实现。

MAC接收模块检测到有效的数据帧时,将接收到的数据发送到HDLC发送模块,并存放在HDLC Transmit FIFO中,程序根据HDLC Transmit FIFO的剩余缓冲区的大小来产生PAUSE帧发送的开(Xon_gen)、关(Xoff_gen)信号。

在本应用中,最大帧长度为1 518字节。PHY发送一个最大帧需要的时间为(8+1 518)×8/(100×106/S)≈122 μs,而远传发送模块以8 M的速率发送一个最大帧需要的时间为(2+1 518)×8/(8×106/S)= 1 520 μs。

因此,当HDLC Transmit FIFO的剩余缓冲区小于1 400 (1 520-122=1 398≈1 400)字节时,产生PAUSE帧发送开始信号Xon_gen,MAC发送模块检测到Xon_gen信号后,发送PAUSE帧,PAUSE帧的pause quanta的值为300 (1 520/5.2≈300),即让PHY等待1 520 μs再开始发送数据;当发送了PAUSE帧后,MAC流量控制模块对pause quanta的值(512/8)×300=19 200)进行减计数,每一个MAC_tx_clk的上升沿,pause quanta值累计减“1”,当HDLC Transmit FIFO的剩余缓冲区大于1 400字节时,此时,若puase quanta计数值大于0,则产生PUASE帧发送停止信号Xoff_gen,MAC发送模块检测到Xoff_gen信号后,发送一个PAUSE帧,PUASE帧的pause quanta的值为0,即令PHY停止等待,重新开始发送数据。

7 结语

根据上述设计方法,已成功地在XC3S1600E芯片上实现了以太网远传模块的功能。XC3S1600E芯片是XILINX公司的SPAN3E系列,最大逻辑门数为160万门,可提供的分布式RAM为231 Kbits,Block RAM为648 Kbits。设计出的以太网远传模块通过如图2所示的连接方式进行数据传输时,两端的PC能互相ping包,能正确传送文件。在传送文件时,远传线路上的速率最高可达7.2 Mbps,平均传输速率大于7 Mbps,能满足应用的需求。