源极引线在开关过程中对栅源电压的影响分析

陈之勃

源极引线在开关过程中对栅源电压的影响分析

陈之勃

(辽宁工业大学 电子与信息工程学院,辽宁 锦州 121001)

分析了氮化镓FET的栅极动态参数,并与硅MOSFET加以对比。分析了栅极驱动电路等效电路及电路模型,分析了驱动回路寄生电感应对驱动回路阻尼比的影响。分析了阻尼比与寄生电感、寄生电容、栅极串联电阻的关系。为了获得合适的阻尼比需要尽可能低的寄生电感,适当增加串联电阻,可以获得“无”超调量的驱动响应。简述了米勒效应会导致栅极电压振铃以及可能形成的误导通,通过施加栅极负偏置电压可以消除,也可以采用零电压开通消除米勒效应,SPWM变换器只能采用硬开关工作模式。

氮化镓FET;寄生电感;寄生电容;阻尼

氮化镓FET的高电子迁移率,极低的寄生电容使得功率变换器的频率得到有效的提高,有效地减小了功率变换器、无源元件的体积。

氮化镓FET的极低寄生电容使得驱动电路变得简单、容易。然而,随着开关速度的提升,驱动线路的寄生电感产生的感生电势对氮化镓栅极将产生不可忽视的影响。

由于极低的栅极寄生电容使得栅极驱动回路的阻尼因数过小引起栅极电压过冲甚至超过栅极极限电压而烧毁;米勒效应将引起开通过程和关断过程的振铃,导致开通过程出现反复的开通-再关断,关断过程出现反复的关断-再开通的现象,可能引起瞬态共同导通烧毁氮化镓FET。

1 氮化镓FET动态参数

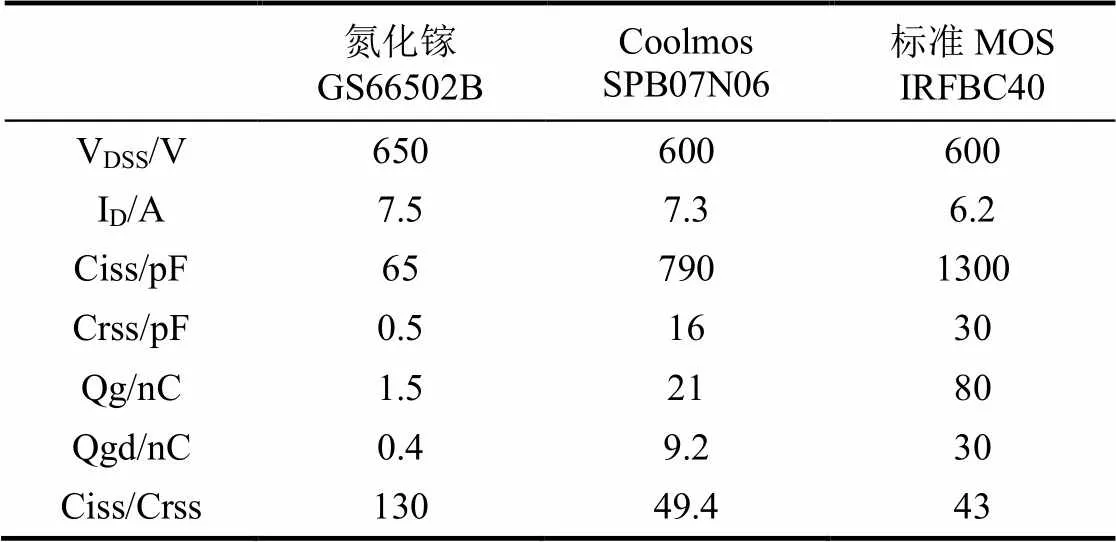

以650V/7.5A的GS65502B为例,输入电容65 pF,米勒电容0.5 pF,栅极电荷Qg1.5nC、Qgd0.4nC。与GS65502B的额定电压、额定电流接近的Coolmos和第三代硅MOSFET的栅极特性如表1。

从表1中可以看到,氮化镓FET的输入电容是Coolmos的8%,米勒电容是Coolmos的9%;分别是第三代MOSFET的5%和1.67%。

表1 氮化镓与硅MOSFET栅极特性对比

表明在相同的驱动能力下,氮化镓的开关速度将分别为Coolmos的11倍和第三代MOSFET的60倍;或者在相同的开关速度下,氮化镓的栅极驱动电流仅仅为Coolmos的8%或第三代MOSFET的1.67%。

2 寄生电感对驱动回路性能的影响

2.1 封装产生的寄生电感

随着氮化镓FET的开关速度的急剧提升,栅极驱动回路的寄生电感将不容忽视,否则会引起超调的栅极电压。

导线的寄生电感无处不在,单引线的寄生电感为0.5 nH/mm。

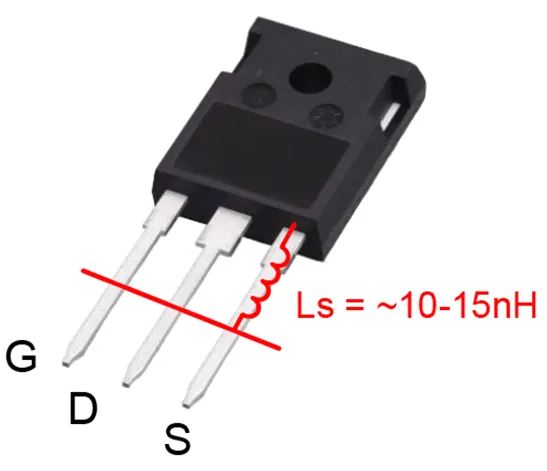

对于功率半导体器件来说,管脚距管壳6 mm处到管芯的寄生电感:TO247源极到管芯13 nH,漏极到管芯5 nH,如图1。

图1 TO247管脚的寄生电感

TO220/D2PAK:源极到管芯7.5 nH,漏极到管芯4.5 nH。

如果加上驱动回路的寄生电感,TO247封装至少有50 nH,TO220封装也有40 nH。

2.2 驱动回路中其他寄生电感

为了降低驱动回路的寄生电感,需要采用功率半导体器件的低寄生电感封装,还要驱动电路的低回路寄生电感以及驱动芯片的低寄生电感封装。绝大多数氮化镓FET采用了极低寄生电感封装,可以将寄生电感降低到1 nH甚至更低。剩下的寄生电感就是电路走线、电源旁路电容器寄生电感和驱动IC的寄生电感,一般不低于20 nH。

将驱动IC紧靠氮化镓FET的栅极与源极,最好走线方式的寄生电感一般不低于10 nH。

驱动IC的寄生电感不容忽视。产生寄生电感的路径为:电源旁路电容器寄生电感,电源旁路电容器到驱动IC正电源端走线的寄生电感,驱动IC正电源端到驱动输出端寄生电感,从驱动输出端到驱动IC电源公共端寄生电感和驱动IC电源公共端到电源旁路电容器的走线寄生电感。这些寄生电感的每一部分一般不低于2 nH,总的寄生电感10~15 nH,加上驱动IC到氮化镓FET栅极走线寄生电感,整个驱动回路寄生电感将不低于20 nH。

3 不考虑米勒效应时栅极动态分析

3.1 栅极驱动回路

通常对栅控器件的理解为栅极驱动回路的等效电路,如图2。

图2 栅极驱动回路的等效电路

图2中忽略源极引线电感的效应,这种忽略可以是源极的主电极引线与栅极信号引线相分离的方式。

图3等效电路的优点是仅仅为一阶电路,数学解析式简单,容易分析。

对于驱动速度比较慢的工作状态,图3电路可以应用,随着栅控器件开关速度的提高,驱动回路的寄生电感及阻尼系数变得不可忽视,特别是对栅极电压幅值敏感的氮化镓FET。因此,带有回路寄生电感的栅极驱动回路的等效电路如图3。

图3 带有回路寄生电感的等效电路

3.2 动态响应分析

为了分析简化,先不考虑ds的作用,得栅极电压gs的解析式为:

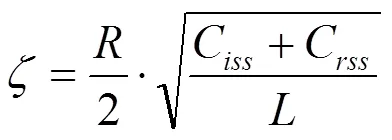

其中阻尼比ζ为:

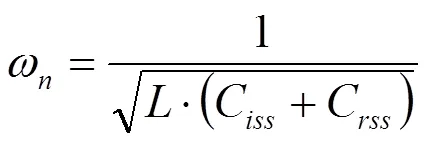

谐振频率为:

不同阻尼比的单位阶跃响应超调量如图4。

如果选用常规的10 Ω,对应的阻尼比将减小到0.29对应的超调量超过35%。比较容易出现栅极电压超过氮化镓FET的栅极电压极限值的现象,进而烧毁氮化镓FET。

4 工程中的解决思路

4.1 尽可能地减小寄生电感

先进的氮化镓FET封装技术可以使器件的栅极到源极的寄生电感降低到1 nH以下,如果选用背面散热的型号,如GS65508T,可以将驱动芯片置于氮化镓FET的电路板底层,减小寄生电感到最小(可以小于1 nH)。

选择寄生电感低的驱动IC封装,例如将SO-8改为GAL封装或引线尺寸更小的封装,可以有效地降低驱动IC引起的寄生电感。

选择低寄生电感的电源旁路电容器。

通过以上措施,可以将栅极驱动回路寄生电感降低到5 nH以下,如果利用布线来抵消驱动回路寄生电感,可以进一步降低驱动回路寄生电感。

4.2 加大栅极与源极间的电容

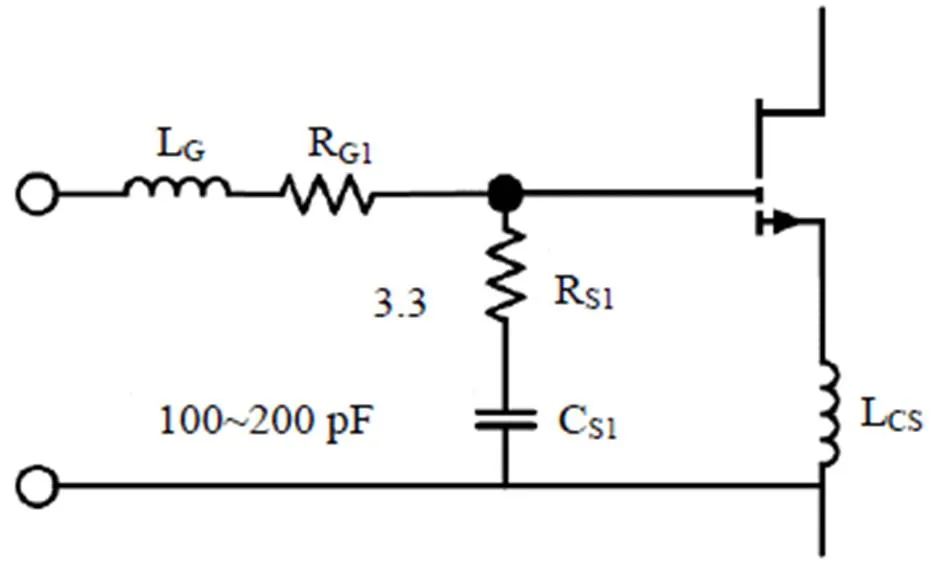

根据公式(2)除了减小驱动回路寄生电感,加大栅极串联电阻外,还可以通过加大栅极对源极的等效电容获得足够的阻尼比,如在栅极与源极之间并联RC电路,如图5。

图5 在栅极、源极之间并联RC电路

图中的电阻RS1起到保证驱动回路阻尼比的作用。这种增加阻尼的方式减缓了氮化镓FET的开关速度,如果能获得尽可能低的驱动回路寄生电感到20 nH以下,没有必要采取这种增加阻尼方式。

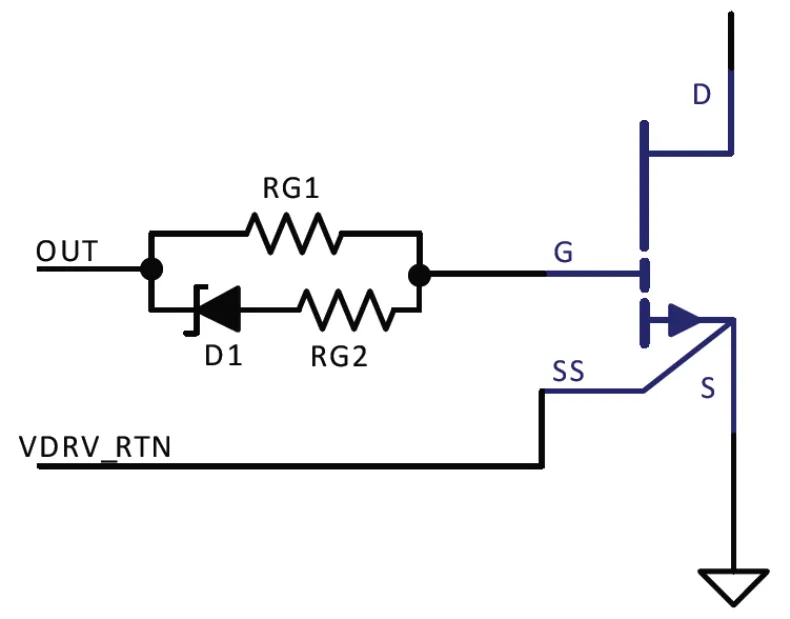

4.3 不对称栅极电阻

采用不对称驱动方式,如图6。

图6 不对称驱动方式

利用比较大的开通串联电阻获得足够的阻尼,使开通过程的栅极电压不产生过度的超调量。

用比较小的关断串联电阻获得快的关断时间。

4.4 栅极、源极电压箝位

防止栅极电压过冲还可以采用限幅方式,如采用稳压二极管限幅方式,如图7。

5 开关过程的瞬态误导通及防止

5.1 瞬态误导通的产生

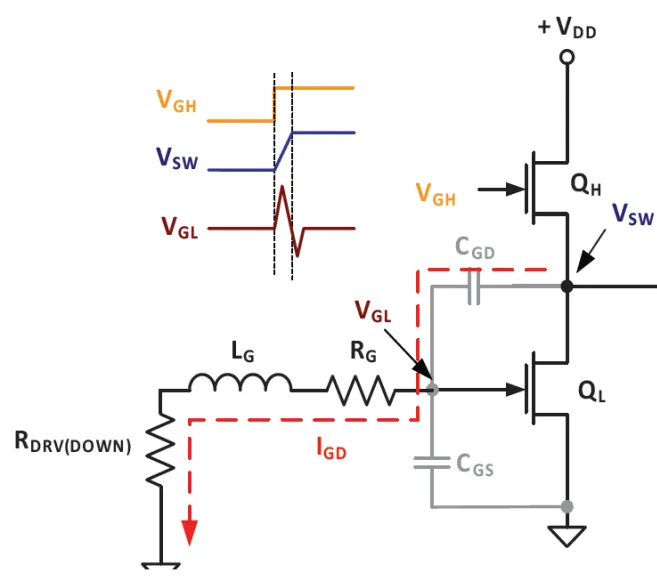

桥式变换器中关断的开关在另一只开关开通过程,其漏极-源级电压会快速上升,通过米勒电容耦合到栅极。如果栅极电压在这个米勒效应作用下超过了导通阈值电压就会产生误导通,并构成桥臂的瞬态共同导通[1]。电路模型如图8。

图7 利用稳压二极管限幅

图8 开关过程的等效电路

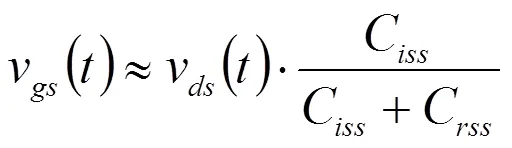

由于栅极驱动电路的寄生电感的存在,当ds快速上升过程中由于寄生电感的存在使得驱动电流无法随之快速改变,为了简化分析,可以将这个过程中忽略驱动回路的影响。可以认为仅仅是Crss和Ciss的分压,即:

栅极变化幅值为:

施加栅极负偏置电压后的栅极电压幅值为:

5.2 施加栅极负偏置电压消除瞬态误导通

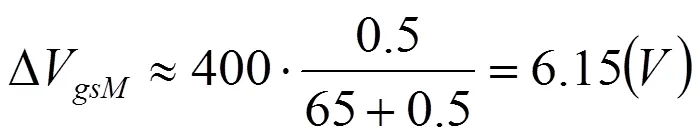

当dsM为400 V,SD65502B对应的栅极电压变化幅值为:

这个数值远远超出导通阈值电压1.3 V,需要加以抑制。施加-6 V栅极反偏电压后的栅极电压幅值为:

可以确保栅极电压不达到导通阈值电压,如图9所示。

5.3 零电压开通消除瞬态误导通

消除栅控器件米勒效应最好的办法就是让氮化镓FET在零电压状态下开通。这样cd=ds,漏极-栅极之间的高幅值、快速变化的电压不存在,米勒效应消失。

工作在这种状态的功率变换器有LLC半桥谐振变换器、桥式/半桥谐振式变换器。这类功率变换器除了没有米勒效应外,也消除了开通损耗。

6 结论

氮化镓FET具有极低的寄生电容。驱动氮化镓FET时,如果驱动电路的寄生电感不能做到尽可能低,很容易出现比较大的超调量。通过采用极低寄生电感封装的氮化镓FET,最短的电路走线和低寄生电感的驱动以及低寄生电感的电源旁路电容器,可以使得驱动回路具有比较低的特征阻抗,通过适当增加栅极外接串联电阻可以使超调量降低到10%以下。

通过不对称驱动技术,可以获得比较高的阻尼比和关断速度。

采用栅极负偏压将栅极振铃幅值抑制到导通阈值电压以下。

各类SPWM逆变器中的开关工作在硬开关状态,无法实现零电压开通工作状态。

[1] 陈永真. 桥式变换器的瞬态共同导通分析及解决方案[J]. 电力电子技术, 2008(6): 84-86.

[2] 陈永真. 高效率开关电源设计与制作[M]. 北京: 中国电力出版社, 2008.

Analysis of Influence of Source Lead on Gate Voltage During Switching

CHEN Zhi-bo

(School of Electronics & Information Engineering, Liaoning University of Technology, Jinzhou 121001, China)

The gate dynamic parameters of gallium nitride FET were analyzed and compared with silicon MOSET. The equivalent circuit and circuit model of the gate drive circuit are analyzed, and the influence of the parasitic inductance on the damping ratio of the drive circuit is analyzed. The relation between damping ratio and parasitic inductance, parasitic capacitance and grid series resistance is analyzed. In order to obtain an appropriate damping ratio, the parasitic inductance should be as low as possible and the series resistance should be appropriately increased to obtain the drive response with “no” overshoot. The miller effect can cause the gate voltage ringing and the misdirection may be formed. The miller effect can be eliminated by applying the negative offset voltage of the gate, and the Miller effect can be eliminated by zero voltage switching. SPWM converter can only use hard switch mode.

gallium nitride FET; parasitic inductance; parasitic capacitance; damping

TM46

A

1674-3261(2021)01-0019-04

10.15916/j.issn1674-3261.2021.01.005

2019-12-20

陈之勃(1985-),男,辽宁盖州人,实验师,硕士。

责任编校:孙 林