PCB 设计的信号完整性解析

赵一鸣

(1.浙江大华技术股份有限公司,浙江 杭州 310000;2.浙江省视觉物联融合应用实验室,浙江 杭州 310000)

PCB 设计时我们常遇到下面情景,当PCB 上两个信号走线紧挨着且长距离平行走线时,信号之间容易互相干扰;或者走线不平滑有拐角出现,走线经过接插件、过孔时会出现振铃等信号质量问题。

上面的是我们PCB 设计人员常遇到的串扰和反射信号完整性问题。下面我们先来看下反射问题。

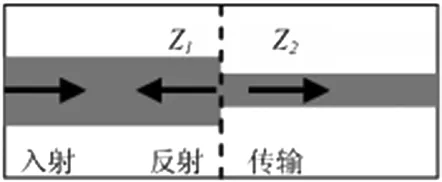

当信号沿着走线传输时,它有一定的瞬态阻抗,而当其瞬态阻抗发生变化时,部分信号就会将沿着与原传播方向相反的方向回传,而另一部分将向前继续传播,但信号幅度有所改变(如图1所示)。我们通常将瞬态阻抗发生改变的地方称为阻抗突变,阻抗突变引起了信号反射。

图1

分析反射问题我们通常运用Altium Designer 软件来进行仿真工作。

用软件进行反射波形仿真时要注意以下几个要点:

(1)每个元件的模型必须正确。

(2)有电路作为源的驱动。

(3)设定激励源。

(4)设定电源和地网络。

(5)PCB 层叠设定。

反射问题的实质其实是传输线的阻抗发生了变化,所以解决阻抗的突变是处理反射的最好手段。那么采取某些方法使得阻抗突变减小,从而改善反射问题是接下来要讨论的内容。

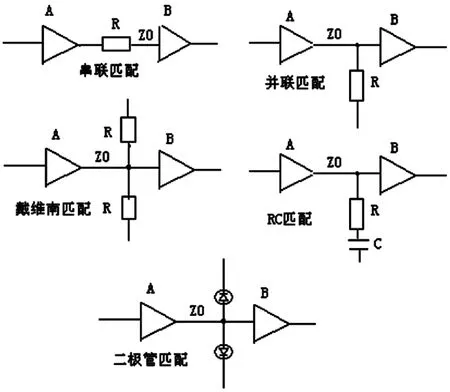

解决阻抗突变常用的阻抗匹配方式有以下几种,如图所示:

(1)串联匹配通常是在输出端上串接一个电阻,使其与传输线的阻抗一致;比较常用是33欧姆的电阻。

(2)并联匹配是在负载端并联电阻或电容,使其阻抗等于传输线特性阻抗。

图2

(3)戴维南匹配是在负载端的电源端上拉电阻R1和在地端下拉电阻R2,通过R1和R2来吸收反射,其等效电阻R1/R2等于传输线阻抗,减少对输出端的驱动要求。

(4)RC 匹配是在负载端并联电容和电阻,电阻来消除反射,电容来减少功耗。

(5)二极管匹配常用于差分信号,对信号的过冲、欠冲有抑制作用,但其无法与线路特性阻抗匹配,所以反射不能消除。

从上面方法来看,串联匹配和并联匹配可能是比较有效的、实用的解决信号反射的方法,接下来用Altium Designer 仿真来看下两种匹配方式的效果。

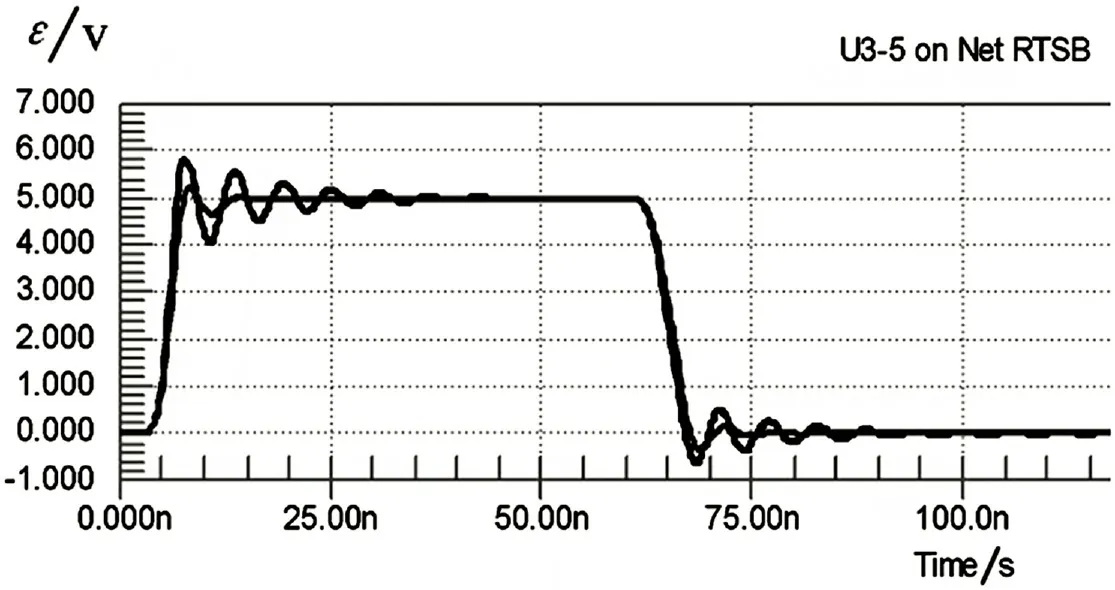

从图3可以看出串联匹配对反射的改善有一定的作用,减小了二次反射波形的幅度,由于二次反射所占比例不大,所以对整体波形的影响不是很大。

图3

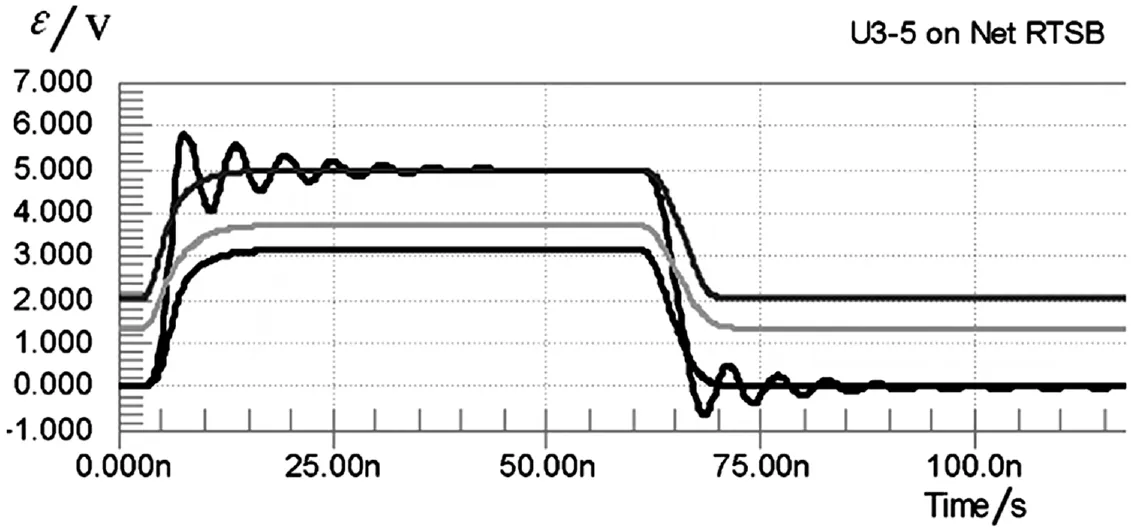

图4所示并联匹配,终端阻抗匹配可以消除一次反射,在根本上解决了反射问题。从如中可看出端接到地使高电平电压下降,端接到电源使低电平变高,同时端接到电源和地就会出现低电平上升、高电平下降,但变化的幅度比前者有所减小。

图4

综上来看,终端匹配是消除信号反射比较推荐的方法,它是在信号能量反射回输出端之前在负载端就把反射消除了,消除了一次反射,减小了噪声等。而串联匹配是在输出端消除由负载端反射回来的信号,消除了二次反射。两种方法各有所长,需要根据实际情况来具体分析。

接下来我们说下减小信号串扰的设计方法。最有效减小串扰的方式是增加走线之间的间距,有足够的空间的话遵守3H/3W 定律;层叠设计可使信号路径与回路平面紧耦合,走线细一些,留出足够的空间规避串扰,适合DDR 这种速率不是特别高的并行信号。

理想带状线没有远端串扰,所以高速串行总线要求TX 与RX 分开,保证串扰不会传向接收端;串扰是有饱和时间的,减少耦合长度同样能减少串扰,即使只是在有空间的地方拉开;要尽量避免长距离平行的微带线;相邻层走线的串扰相对同层之间更大,需要避免。

在不考虑损耗的情况下,要加大信号与其回流路径之间的耦合;跨分割会引起严重的串扰、EMC 问题需要注意;同样阻抗匹配也能有效的减小串扰;包地要谨慎,数字信号不建议包地处理。

PCB 的信号完整性是一个系统问题,要灵活运用理论知识及方法来解决实际中遇到的信号质量问题。