一种基于SIPOS 结构的高压深结复合终端

王振硕,李学宝,马 浩,吴昊天

(华北电力大学 新能源电力系统国家重点实验室,北京 102206)

对于高压功率芯片,目前最常采用平面结终端技术。平面结终端技术主要有场板(FP)、场环(FLR)、结终端延伸(JTE)和横向变掺杂(VLD)。现有研究结果表明,单一的平面结终端技术虽然各有优势,但是在高压场景下难以满足耐压需求。场环终端容易受到界面电荷和表面电场峰值的影响[1],并且场环终端占用芯片面积较大,芯片有效利用率偏低。场板技术的缺点在于场板末端与硅衬底之间的电位差很大,很容易在场板末端击穿,因此场板技术往往不单独使用[2]。而结终端延伸结构容易受到界面电荷和表面电场峰值的影响,高压深结器件多区结终端延伸结构在设计和工艺上要求极高。横向变掺杂结构也容易受到界面电荷和表面电场峰值的影响,而且高压深结器件的横向变掺杂结构末端电场强度过于集中,容易造成耐压水平下降。因此,单一平面结终端结构难以满足高压芯片的耐压需求。

针对单一的平面结终端技术存在的缺陷,也有学者提出了新材料和新技术,如多晶硅场板[3]、SIPOS技术[4]以及沟槽型场环结构[5]等,虽然这些新材料和新技术可提升芯片终端耐压水平,但仍然难以满足更高电压等级芯片的研制需求。

为此,许多学者提出采取复合平面结终端技术的设计方案。复合平面结终端技术最常用的是场环与场板的结合[6]。然而在高压功率器件中,场板末端与硅衬底之间的电位差很大,致使击穿电压的提高很困难。而多层偏移场板技术在设计时每个场板的位置和长度的确定是个难题。文献[7]对单区JTE 与场板的复合结构进行了优化,减小了界面电荷的影响。文献[8]设计了一种GCT 的VLD-JTE 的复合终端结构。文献[9]设计了一种VLD-FR 的复合终端结构。这两种复合结构都可以有效缓解高压深结VLD 结构末端因曲率问题导致的耐压效率偏低的问题。但是这两种复合结构的设计和分析都尚未关注在实际工艺中所产生的界面电荷对击穿电压的影响。

鉴于此,本文结合VLD、JTE 和SIPOS 结构的优势,提出了一种复合终端结构,不仅提高了高压深结器件的击穿电压,也可以有效减小界面电荷对终端耐压的影响。在此基础上,本文设计了一个耐压为3.3 kV 的复合终端结构。仿真结果表明,即使在存在界面电荷的情况下,所提终端结构的击穿电压也可达到4000 V 以上,同时也分析了关键影响因素对所提复合终端结构击穿电压的影响规律。

1 复合终端结构及其原理

1.1 VLD 与JTE 复合终端结构

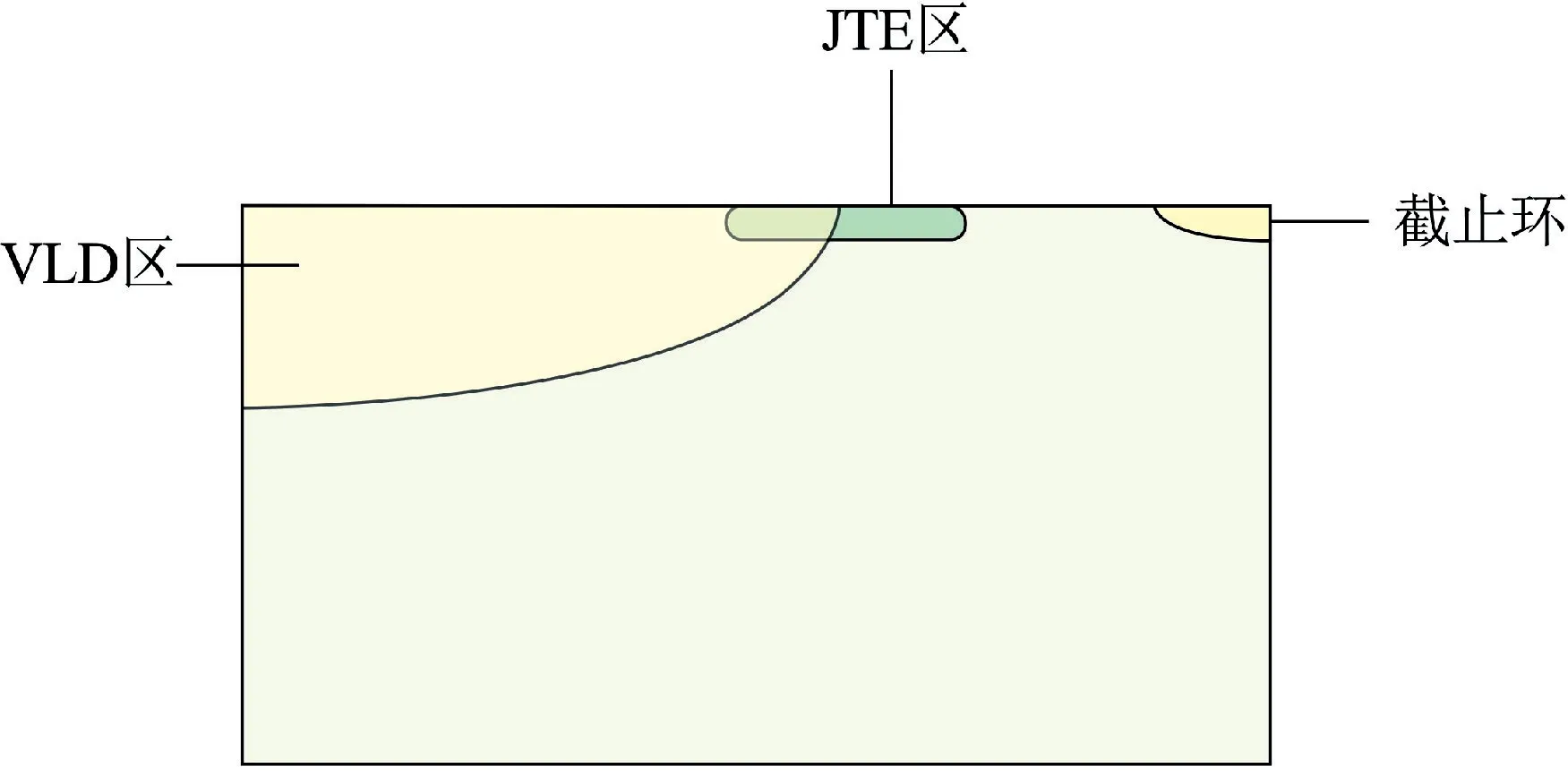

VLD 是通过逐渐减小掩膜窗口令离子一次性注入,再经过高温退火而形成的[10]。VLD 与JTE 复合终端结构为在VLD 区末端加入一个JTE 区,其中部分JTE 区位于VLD 区内部,如图1 所示。在VLD 与JTE复合终端结构中,VLD 区采用铝离子注入并进行长时间的高温退火,形成一个结深和近表面掺杂浓度都渐变的深结P 区。因为铝离子高温退火时在硅衬底中扩散快,会造成在VLD 末端的位置处即使很小的掩膜窗口也会形成很深的结深,导致在VLD 区末端P-N 结曲率过大,电场强度过于集中,由此造成器件耐压效果变差。JTE 区采用硼离子注入,退火时间相对较短,形成一个结深和近表面掺杂浓度都恒定的浅结P 区,可以缓解因VLD 区末端P-N 结曲率过大而造成的电场强度过于集中的问题。

图1 VLD-JTE 结构示意图Fig.1 Schematic figure of VLD-JTE structure

但是,在实际的工艺中,离子注入的退火和硅表面热生长氧化物等过程会引入杂质电荷离子,这些带正电荷的离子会改变衬底内部的电场分布,使耗尽层发生变化。高压深结VLD 结构的末端曲率很大,虽然针对VLD 结构增加了JTE 区域,但是常用的绝缘性氧化膜SiO2无法有效防止器件表面电荷的累积和离子玷污[11],这些电荷在接近硅衬底表面的地方感应出极性相反的电荷,改变了器件的表面电场,造成P-N 结反向击穿电压变小,进而导致在实际的生产工艺中终端结构的耐压能力变差。

1.2 基于SIPOS 结构的VLD 与JTE 复合终端结构

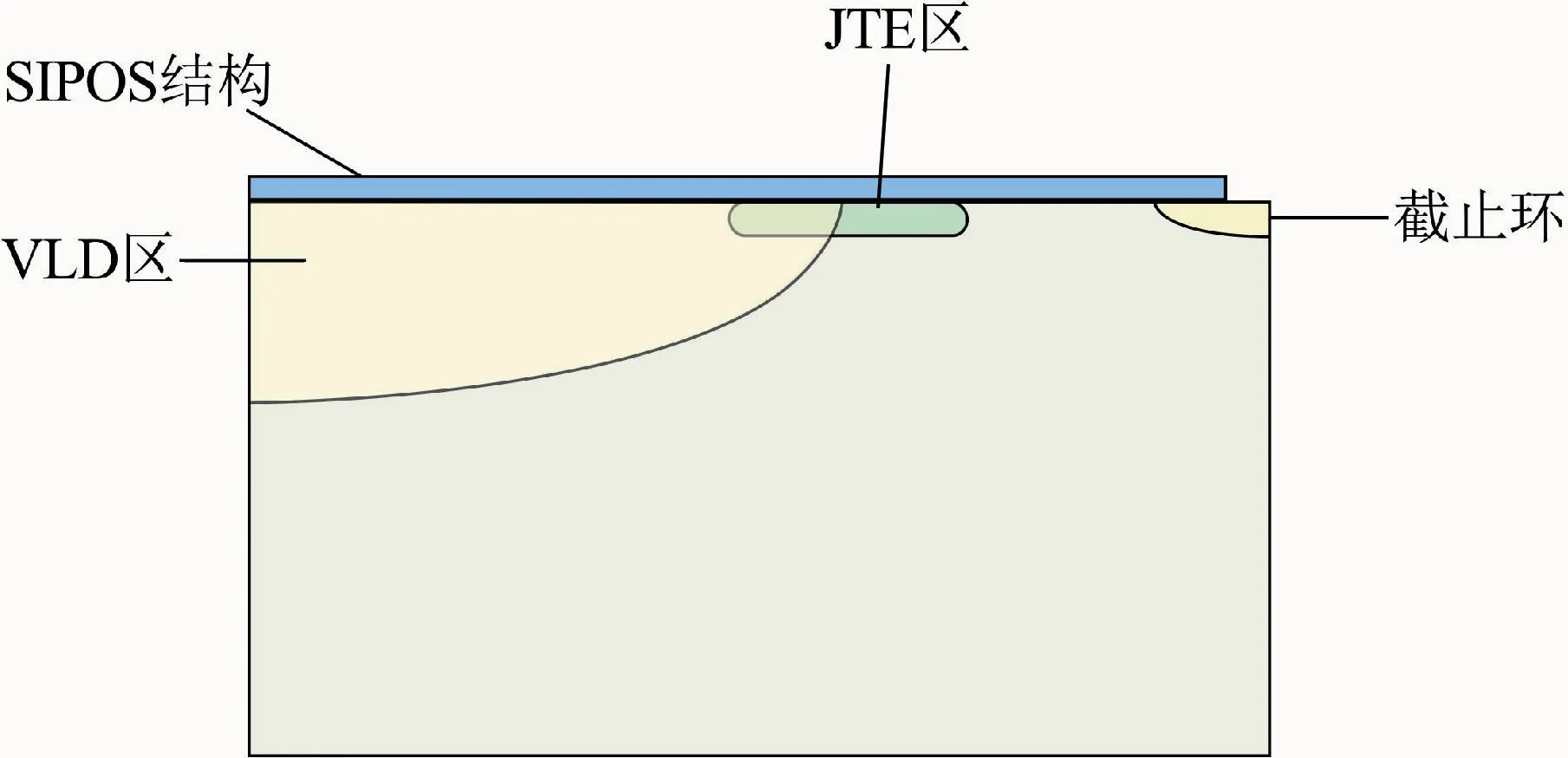

为解决界面电荷对VLD 与JTE 结合终端结构影响较大的问题。本文提出了一种基于SIPOS 结构的VLD与JTE 复合终端结构,具体如图2 所示。

图2 基于SIPOS 的VLD-JTE 结构示意图Fig.2 Schematic figure of VLD-JTE structure based on SIPOS

本文所提的终端结构分为三个部分:VLD 区、JTE 区与覆盖在衬底表面的SIPOS 结构,各部分结构特点如下:(1)VLD 区掺杂浓度与结深自左向右逐渐变小,为整个终端结构的主要部分;(2) JTE 区前段位于VLD 区域内部,受VLD 区掺杂分布的影响,掺杂区域也渐变。JTE 区后端掺杂浓度恒定;(3)衬底上方覆盖的是SIPOS 结构。SIPOS 结构从主结位置开始一直覆盖到截止环的中心位置。

由于SIPOS 结构自身具有的特点:电中性、与硅接触的界面不存在高能势垒、内部存在高密度陷阱,相对于绝缘性氧化膜,在工艺上SIPOS 结构不仅能够防止外界有害杂质离子对衬底的沾污,还可以缓和已经沾污在衬底表面的有害杂质离子对硅表面电场的影响。同时,如果SIPOS 结构被离子沾污后,会在表面附近感应出极性相反的电荷,这些电荷漂移到SIPOS层内将和外表面电荷中和,或被陷阱捕获,从而形成一个小的空间电荷区[12],故本文所提出的结构对外加电场也具有一定的屏蔽作用,对钝化也有帮助。

此外,由于SIPOS 结构具有半绝缘性,可以起到阻性场板的作用[2],对衬底的表面电场也起到调制的作用,从而提升器件反向耐压水平,而界面电荷对器件击穿电压的影响也会显著降低[12]。

2 所提结构耐压特性的仿真分析

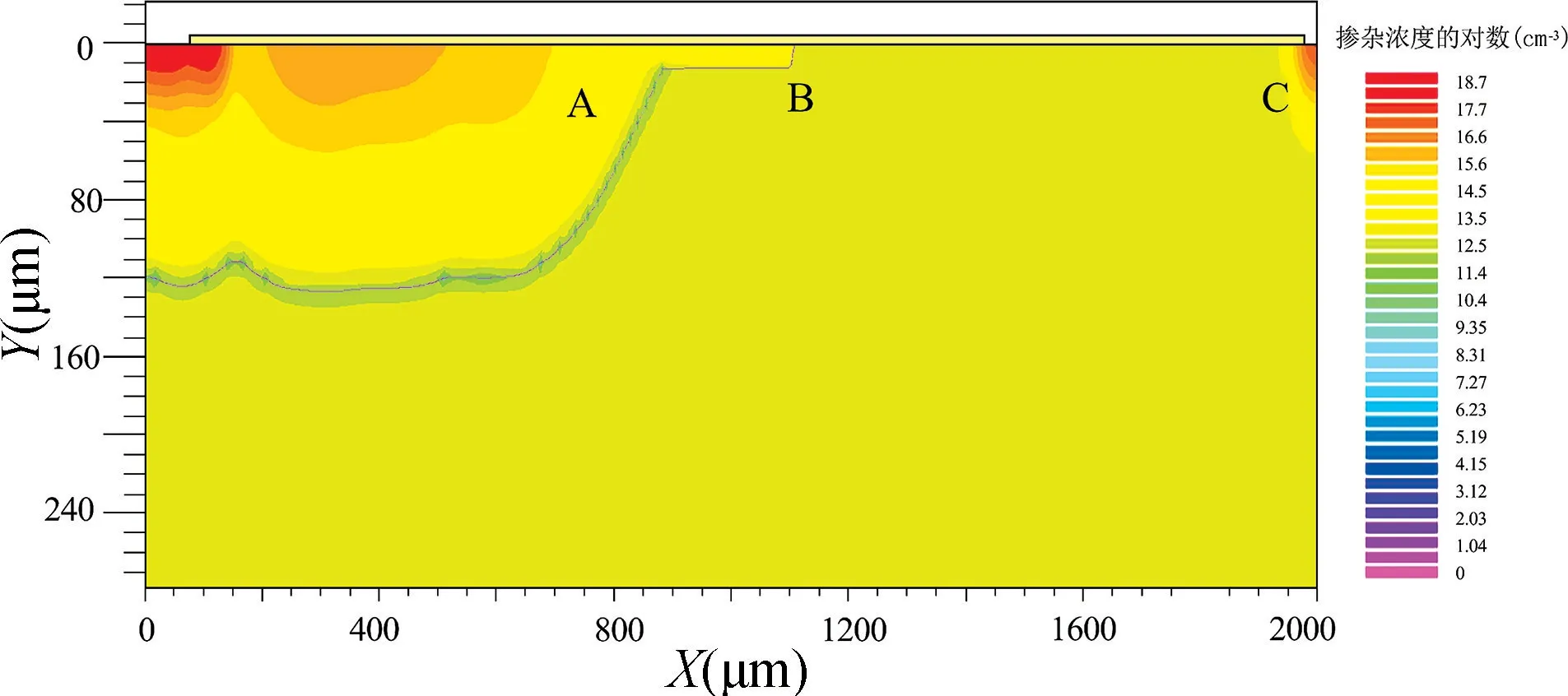

本文以3.3 kV 芯片的终端为例,利用TCAD 仿真分析所提出的VLD-JTE-SIPOS 结构的耐压特性,如图3 所示选定整个衬底厚度为700 μm,宽度为2000 μm。

图3 掩膜示意图Fig.3 Schematic figure of the mask

VLD 区域扩散窗口的开始位置为200 μm 处(左侧是主结),最后一个扩散窗口的末端位置为700 μm 处,具体所采用的掩膜方案为:每一段遮掩加右侧相邻的扩散窗口长度之和固定为85 μm,扩散窗口依次为:L1=80 μm,L2=70 μm,L3=60 μm,L4=50 μm,L5=40 μm,L6=30 μm,L7=10 μm,如图3 所示。铝离子高温扩散后,在140~860 μm 处形成VLD 区域,总长度为720 μm(不包含主结),结深最大处为127 μm。

JTE 区采用硼离子注入并高温扩散的方案形成一个结深为13 μm 的JTE 区域。该区域位于720~1100 μm 处,总长度为380 μm,其中有140 μm 位于VLD区域中。而SIPOS 结构在仿真中的具体参数[13]如表1所示。

表1 SIPOS 结构的仿真参数Tab.1 Simulation parameters of SIPOS structure

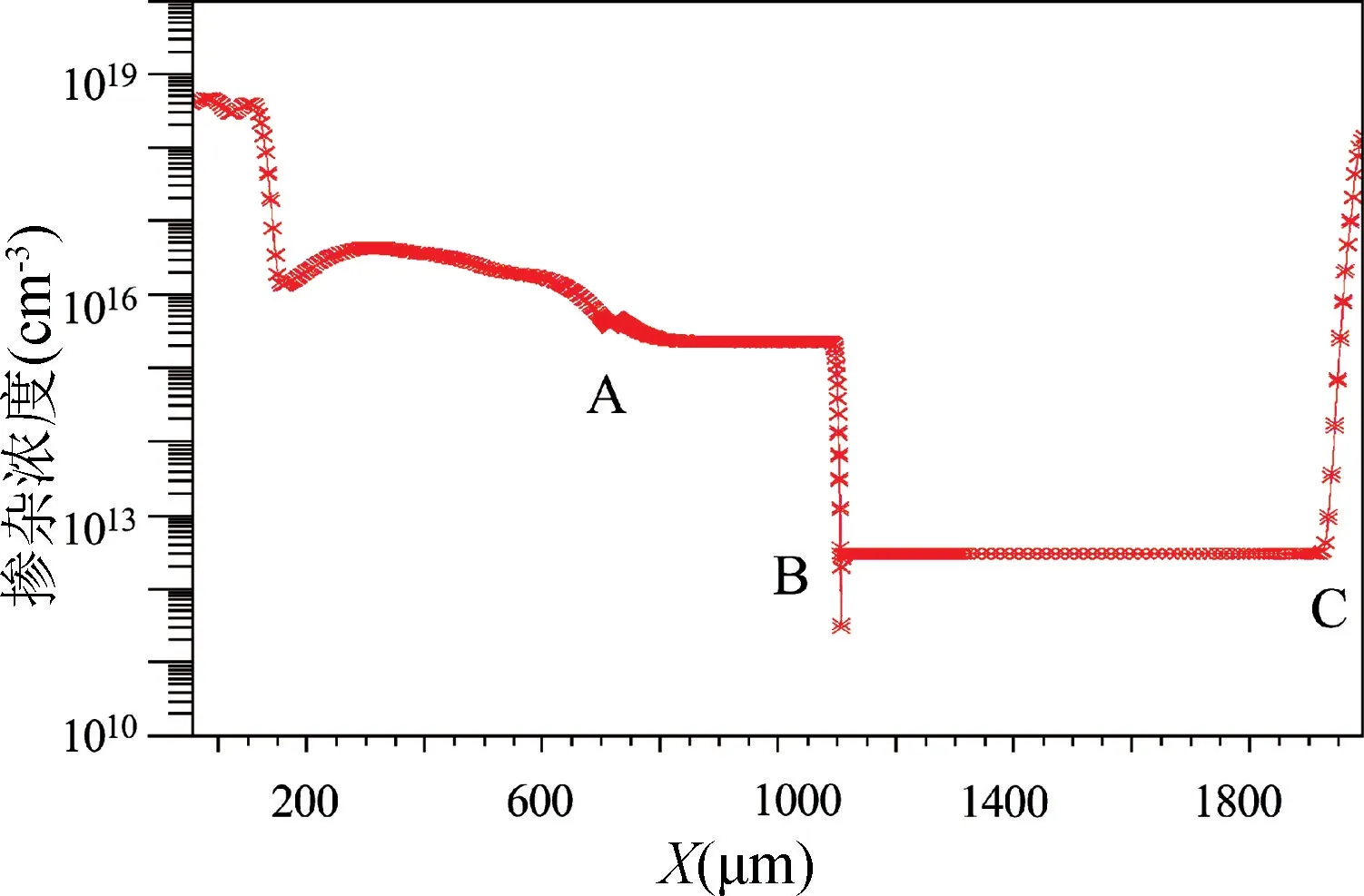

仿真得到的结构和近表面掺杂浓度变化情况分别如图4 和图5 所示。

图4 仿真中结构的掺杂分布图Fig.4 The doping distribution of the structure in simulation

图5 结构的掺杂浓度变化曲线图Fig.5 The doping concentration curve of the structure

由图4 和图5 可见,在仿真中,整个终端区域的近表面掺杂浓度和结深在300 μm 的位置达到最大值,之后逐渐变小。在JTE 区的起始位置720 μm 处(如图4 与图5 中A 点所示),近表面掺杂浓度出现轻微增加,之后继续递减。在860 μm 处VLD 区结束(如图4 与图5 中的B 点所示),之后的近表面掺杂浓度和结深恒定直至JTE 区结束。曲线最末端为截止环的掺杂浓度变化情况(如图4 和图5 中的C 点所示)。

在无界面电荷的情况下,VLD-JTE-SIPOS 结构的击穿电压达到了8300 V,击穿位置位于JTE 区末端处,如图6 所示。由图6 可见,电场强度最大点位于JTE 区域的末端位置(如图6 中A 点所示)。击穿时的最大场强为1.96×105V·cm-1,低于工业上判断器件击穿场强的标准(2.5×105V·cm-1)[14]。

图6 仿真中结构的击穿位置图Fig.6 The breakdown position of the structure in simulation

在实际生产工艺中,SIPOS 结构由于自身的特性,比绝缘性氧化膜SiO2产生的界面电荷更少。本文仅在相同界面电荷浓度下对VLD-JTE-SIPOS 结构与VLD-JTE-SiO2结构的击穿电压进行仿真对比。在仿真时,两种结构的VLD 区域与JTE 区域完全一样。

选取界面电荷浓度为0,1×1011以及6×1011cm-2,对两种结构的耐压情况进行仿真分析,结果如图7 所示。由图7 可见,当界面电荷存在时,新结构的击穿电压始终高于VLD-JTE-SiO2结构的击穿电压。不同界面电荷浓度对应的具体击穿电压如表2所示。

表2 两种结构的击穿电压对比表Tab.2 The breakdown voltages of the two structures at different concentrations of interfacial charges

图7 击穿电压对比图Fig.7 Breakdown voltage comparison

在实际生产中SIPOS 结构相对于SiO2还具有良好的抗污染性,且SIPOS 结构与硅衬底之间复合中心密度很低。所以实际生产中,所提结构的击穿电压会比VLD-JTE-SiO2结构的击穿电压高得多。

3 新结构关键影响因素分析

3.1 温度对击穿电压的影响

在实际工况下,芯片的温度会逐渐升高至125 ℃。温度会对本征载流子浓度产生影响,进而影响到器件的击穿电压。因此,需要研究温度对器件击穿电压的影响。

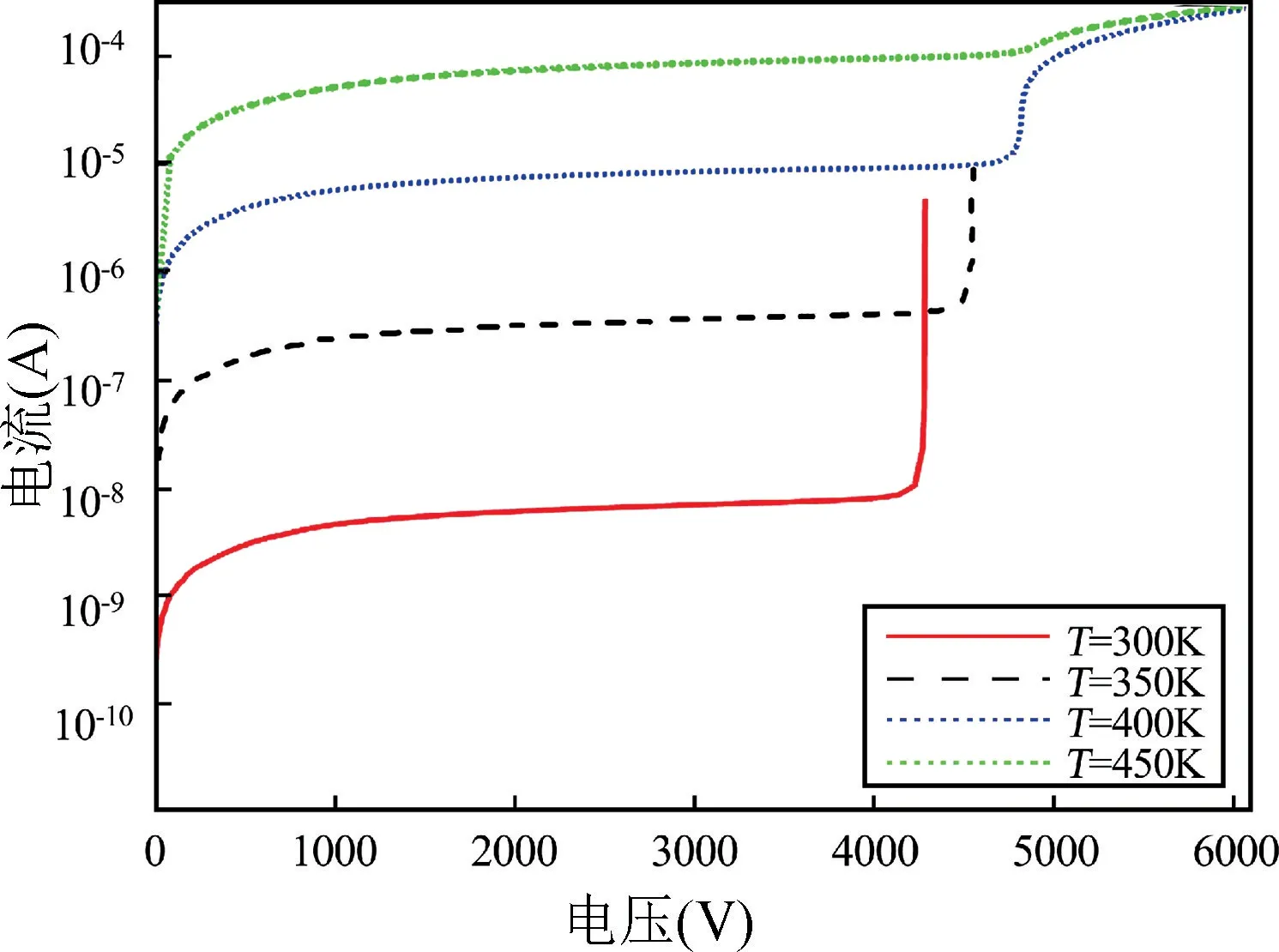

设定界面电荷浓度为4×1011cm-2,选取温度为300,350,400,450 K,对新结构的耐压情况进行仿真分析,结果如图8 所示。

图8 不同温度下的击穿电压曲线图Fig.8 Breakdown voltage curves at different temperatures

由图8 可以看出随着温度的提高,新结构的漏电流与击穿电压都不断提高。漏电流的大小在450 K 时比室温下高出三个数量级。

对于硅衬底来说,其击穿电压可以表示为[15]:

式中:Eg表示禁带宽度;NB表示掺杂浓度。由于硅衬底材料具有正温度系数,随着温度的升高击穿电压不断变大。其原因为随着温度升高,载流子平均自由程减小,两次碰撞之间获得的能量减小,要达到原来击穿能量所需要的电场强度增大,所以P-N 结临界击穿电场强度Ec增大,进而使P-N 结反向击穿电压随温度升高而增大。

而对于漏电流来说,漏电流随温度的变化主要是由本征载流子的温度特性造成[16],而本征载流子的浓度与温度的关系可以表示为[17]:

式中:NC和NV分别表示导带能级和价带能级。当材料一定的情况下,本征载流子浓度ni会随着温度上升而升高,进而导致图8 所示的漏电流随温度上升而增大。

3.2 界面电荷对击穿电压的影响

在目前工艺中,可以将界面电荷的浓度控制在一定范围内,但始终无法避免界面电荷的存在,所以必须考虑界面电荷对击穿电压的影响。

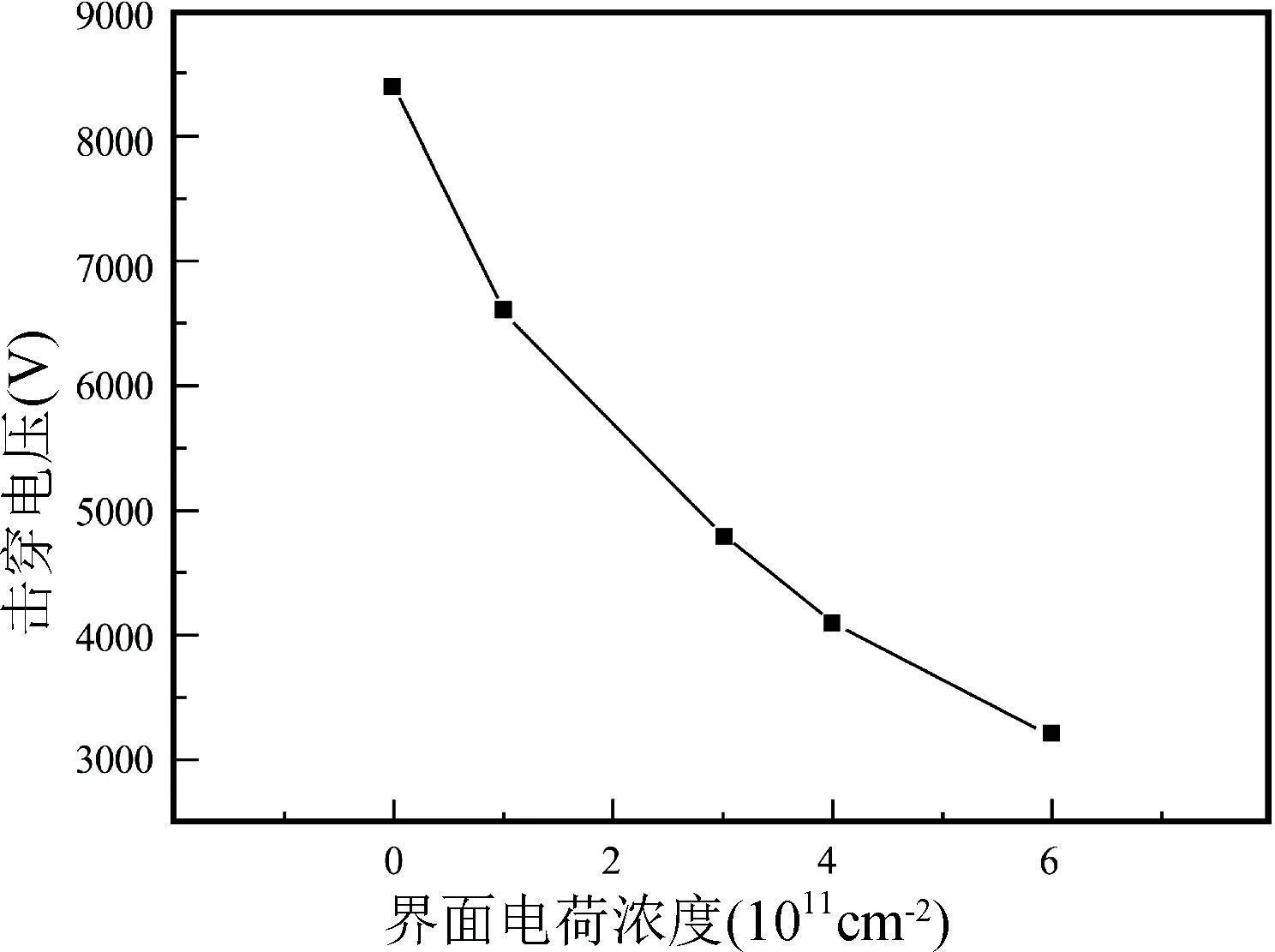

虽然VLD-JTE-SIPOS 结构的击穿电压受界面电荷的影响较小,但是仍需考虑界面电荷对结构击穿电压的影响。选取界面电荷浓度为0,1×1011,3×1011,4×1011及6×1011cm-2,对新结构的耐压情况进行仿真分析,结果如图9 所示。由图9 可以看出,随着界面电荷浓度的增加,终端的击穿电压不断下降。目前,在工业生产过程中,界面电荷浓度可以控制在4×1011cm-2以下。此外,所提结构在界面电荷浓度为4×1011cm-2时,击穿电压仍能达到4000 V 以上(保留20%以上的裕量),在击穿时最大击穿场强为1.96×105V·cm-1。满足了3.3 kV 等级的深结芯片的耐压需求。

图9 不同浓度的界面电荷下的击穿电压图Fig.9 Breakdown voltage at different concentrations of interface charges

3.3 JTE 区长度对击穿电压的影响

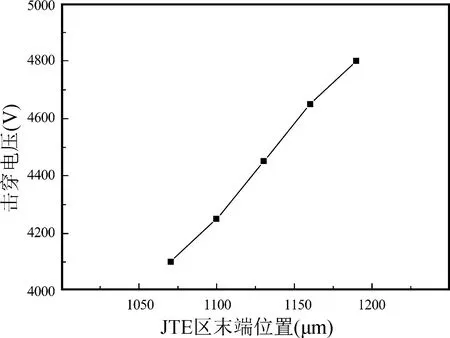

为了充分发挥JTE 区的作用,JTE 的长度不能过短。JTE 区的起始位置为720 μm 处,JTE 区末端位置的变化对击穿电压的影响如图10 所示。JTE 长度的不断增加,会使空间电荷区不断地展宽,进而使击穿电压不断提高。

图10 JTE 末端不同位置时的击穿电压图Fig.10 Breakdown voltage diagram at different positions of JTE terminal

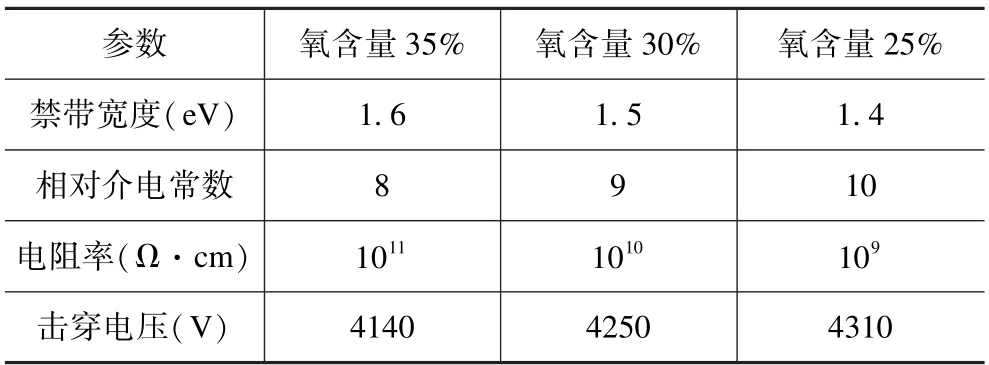

3.4 SIPOS 氧含量对击穿电压的影响

SIPOS 结构是在多晶硅Poly 的工艺基础上制作的。在气相淀积SIPOS 结构的过程中要引入一定比例的N2O 气流,产生的具体反应可以表示为:

式中:x大于0 而小于等于2,它标志着掺氧多晶硅的氧含量,决定了SIPOS 的各种物理化学性质、生长速率、腐蚀速率等。

SIPOS 的电学性质介于二氧化硅与多晶硅之间,二氧化硅与多晶硅电学特性如表3 所示。SIPOS 的氧含量越高其性质就越接近二氧化硅,氧含量越低其性质就越接近多晶硅场板。

表3 多晶硅与二氧化硅部分电学特性对比表Tab.3 Comparison of electrical properties between polysilicon and silicon

文献[18]中给出了SIPOS 在氧含量占整体质量的15%~35%范围内变化时,各种电学特性的对应变化情况,而对应不同氧含量时的介电常数也随之变化[18-20]。结合以上文献给出的具体参数和变化规律,确定在仿真中不同氧含量的SIPOS 对应的电学特性如表4 所示。但是SIPOS 的各种电学特性还受到制备过程中的具体工艺的影响,因此,本仿真仅反映击穿电压随着氧含量的变化而变化的一般规律。

表4 仿真中不同电学特性对应的击穿电压表Tab.4 The breakdown voltages of the two structures at different concentrations of interfacial charges

由表4 可见,随着SIPOS 结构氧含量的减少,SIPOS 覆盖的器件的击穿电压也不断提高。氧含量过高的SIPOS 结构性质接近二氧化硅,对衬底的电场调制效果会削弱。氧含量过低则SIPOS 结构接近于多晶硅,会产生较大的漏电流和欧姆电流,另对界面电荷的捕获效果也会削弱[13]。因此,在实际生产工艺中通常根据需要选用氧含量合适的SIPOS 结构。

4 结论

本文提出了一种VLD-JTE-SIPOS 的复合终端结构,并对VLD-JTE-SIPOS 的复合终端结构关键参数进行了仿真分析研究。结论如下:

(1)本文所提出的VLD-JTE-SIPOS 的复合终端结构,能有效改善界面电荷对VLD-JTE 的复合终端结构击穿电压的影响。

(2)采用VLD、JTE 及SIPOS 技术设计了一款3.3 kV 的高压深结终端,并对其关键参数进行了仿真分析,可以看出随着SIPOS 结构氧含量的减少,新结构的击穿电压不断提高。而随着温度与界面电荷浓度的增加,新结构的击穿电压会不断下降。在界面电荷浓度为4×1011cm-2的时候,实现了4000 V 以上的耐压。本文提出的结构提高了终端的击穿电压且减少了界面电荷的影响,从而提高了器件的稳定性和可靠性。希望能对以后的复合终端结构设计提供思路。