基于ADRV9009的小型化DRFM系统设计与实现

摘要:DRFM作为一种相干干扰技术,具有干扰功率利用率高、干扰反应快等特点,是干扰现代相干体制雷达的重要工作工作方式。针对雷达对抗装备小型化、网络化发展趋势,本文提出一种基于ADRV9009 SoC芯片的小型化DRFM系统设计方案。相比传统DRFM系统设计方案,本方案明显减少了设备树立并提高了系统可靠性。经过测试验证,该方案具有重要的工程应用价值。

关键词:DRFM;小型化;密集假目标。

引言

现代雷达广泛应用多波形设计、重频参差、调频、相控阵波束扫描以及灵活的信号处理与数据处理等技术,雷达越来越复杂,综合抗干扰能力不断提高。DRFM干扰技术是对雷达信号进行数字存储,经过干扰调制后转发出去,其干扰信号保留了相参性,是实施相参干扰的关键技术之一,在雷达对抗设备中广泛应用。

随着无人机技术的快速发展,适用于无人机平台的小型化、网络化雷达对抗设备是雷达对抗技术的一个重要发展方向。本文以ADI公司的ADRV9009 SoC芯片为核心,设计了一款具备DRFM功能的小型化雷达干扰系统,并对原理样机进行了指标测试,验证了系统的功能、性能。

1、干扰信号模型

基于DRFM技术产生的假目标干扰信号,数学模型如下:

其中U(t)为幅度调制,τ为时延参数,fd为多普勒调制参数。

将雷达信号样本和噪声卷积,利用噪声卷积调制可以产生相干灵巧噪声干扰,数学模型如下:

其中,U(t)为幅度调制,τ为时延参数,Jm(t)为噪声信号,S(t)为样本信号。

2、小型化DRFM系统设计

DRFM系统组成一般包括侦察天线、接收变频通道、数字接收模块、信号处理模块、波形产生模块、发射变频通道、干扰天线等,硬件组成如下图所示。

侦察天线与接收变频通道完成空间射频信号的接收、滤波、放大、变频等处理,将1路中频信号送至数字接收模块;数字接收模块完成数字采集、DDC及滤波处理,将基带信号送信号处理模块;信号处理模块进行参数测量、信号分选、重频跟踪、干扰信号产生等处理,并将基带干扰信号送波形产生模块;波形产生模块对基带干扰信号进行DAC处理产生中频干扰信号送发射变频通道;发射变频通道将中频干扰信号进行上变频、滤波、放大形成射频干扰信号,并通过发射天线发射出去。传统的DRFM系统,接收/发射变频模块、数字采集/波形产生模块、信号处理模块一般单独设计,硬件模块多,很难实现设备的进一步小型化。

ADRV9009是一款高集成度射频(RF)、捷变收发器,提供双通道接收器和发射器、集成频率合成器以及数字信号处理功能。接收路径由两个独立的宽动态、直接变频接收器组成,具有一定的动态范围。芯片内部还集成多种辅助功能,比如模数转换器(ADC)、数模转换器(DAC)、用于功率放大器的通用输入/输出(GPIO)以及RF前端控制。其主要参数如下:

适应信号频率:75MHz~6GHz;

最大接收带宽:200MHz;

最大发射带宽:450MHz;

全集成的时钟合成器;

JESD204B数据路径接口;

简要来讲,ADRV9009芯片内部集成了接收/发射变频、AGC控制、ADC、DAC等功能模块,通过一片ADRV9009就可以完成75MHz~6GHz射频信号的数字采集,输出基带信号波形给信号处理;以及接收基带干扰信号,产生射频干扰信号。通过将ADRV9009芯片与信号处理电路、设备监控电路进行集成设计,可以在一块数字处理板卡上实现传统的DRFM功能。

3、硬件设计与验证

根据该方案,采用Xilinx公司的XCZU11EG-2FFVF1761I SoC芯片、ADI公司的ADRV9009、JetsonTX2GPU作为核心处理器设计了一块高集成数字处理板,实现DRFM系统信号采集、参数测量、干扰产生、射频发射等功能。

该数字处理板采用模块化的设计方式,将主要的一些扩展功能进行标准模块化,比如GPU、NVMe、FMC+等。其余的各个功能接口,采用专用芯片实现,引出系统所需要的各项必要功能接口。

板卡中采用了PS侧外接DDR4内存,采用QSPI的启动方式,同时提供了32GB的eMMC存储空间,满足基本的系统、配置数据等存储需要。同时通过USB3320引出USB2.0接口,通过88E1512芯片实现千兆以太网的引出,满足通讯与控制接口的需要。PS侧的高速GTR接口,设计为X4的PCIE2.0,用于与GPU进行互联,实现与GPU的数据互发。PL侧主要是通过IO端口实现各个专用接口,通过MAX3491实现所需要的IRIG-BRS-422\485接口;通过TXS0108电平转换芯片实现GPIO的隔离输出,用于控制外部的射频模块;通过实现SPI接口,用于控制433通信模块;通过IObank的合理分配实现FMC+所需要的80组LVDS接口信号。

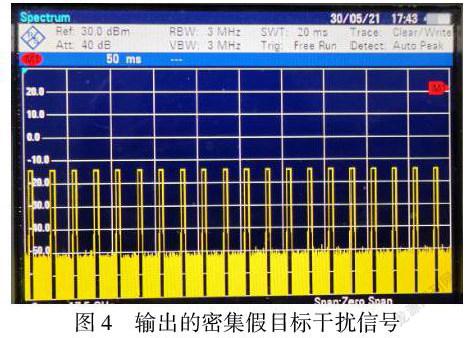

该数字处理板完成加工、调试后,对实现的DRFM功能性能进行了测试。经过测试,该模块产生的密集假目标干扰信号波形如下图所示,与预期效果一致。

4 结论

数字射频存储器(DRFM)可以对雷达信号进行长时间的相干存储,转发的干扰信号可以获得雷达的脉冲处理得益,从而大大降低了干扰设备的功率需求,为干扰现代相干体制雷达提供了有力的技术手段。本文在DRFM干扰的原理基础上,提出一种基于ADRV9009 SoC芯片的小型化DRFM系统实现方案。通过对研制的原理样机的测试,验证了该DRFM系统的功能、性能。实测结果证明,本文中的基于ADRV9009 SoC芯片的DRFM系統设计方案具有很好的工程应用价值。

参考文献

[1]丁鹭飞.雷达原理[M].西安:西北电讯工程学院出版社 1984.

[2]吴顺君,梅晓春.雷达信号处理与数据处理技术[M].北京:电子工业出版社 2008.

[3]赵国庆.雷达对抗原理[M].西安:西安电子科技大学出版社 2003.

[4]刘忠. 基于DRFM的线性调频脉冲压缩雷达干扰新技术[D]. 博士学位论文,2006.10.

[5]韩俊宁,王晓燕,赵国庆. 准数字示样DRFM干扰的研究[J]. 电子信息对抗技术,2006.3.

[6]张养瑞,李云杰,李曼玲. 间歇采样非均匀重复转发实现多假目标压制干扰[J]. 电子学报,2016.3.

作者简介:李彦栓男,1987年生,工程师,硕士毕业于西安电子科技大学。现主要研究方向:雷达对抗系统设计。