低电压低功耗音频Σ-Δ ADC调制器设计

张涛 何鹏 刘劲

摘 要:针对应用于音频设备中的Σ-Δ ADC,提出一款改进的Σ-Δ ADC调制器. 该调制器结构改进传统调制器的结构并对调制器系数进行优化,克服传统Σ-Δ ADC调制器结构的缺点,同时对调制器中的两个关键电路即OTA放大器和比较器也进行优化,极大改善了OTA放大器和比较器性能. 改进后的调制器具有低电压、低功耗、高精度和较好的鲁棒性的特点. 该调制器采用1.2 V低电压供电,过采样比(OSR)为128,采样频率为6.144 MHz,信号带宽为20 kHz. 基于SMIC0.11 μm的工艺下,完成了Σ-Δ ADC调制器的版图设计,并最终流片成功. 芯片流片后的成测结果表明,调制器的信噪比达到102.4 dB,有效位达到16.7 bit,调制器的整体功耗仅1.17 mW左右,整个调制器的版图的面积仅为0.122 mm2左右. 调制器的成测性能指标表明,该调制器是音频芯片中Σ-Δ ADC电路的良好选择.

关键词:模数转换器;Σ-Δ调制器;低功耗;低电压

中图分类号:TN432 文献标志码:A

Design of Low Voltage Low Power Audio Σ-Δ ADC Modulator

ZHANG Tao,HE Peng,LIU Jing

(School of Information Science and Engineering,Wuhan University of Science and Technology,Wuhan 400080,China )

Abstract:A Σ-Δ ADC modulator with low voltage and low power consumption is proposed for the application of Σ-Δ ADC in audio equipment. The modulator structure improves the traditional modulator structure and optimizes the modulator coefficients,thus overcoming the shortcomings of the traditional Σ-Δ ADC modulator structure. At the same time,OTA amplifier and comparator,two key circuits in the modulator,are optimized,which greatly improves the performance of OTA amplifier and comparator. The improved modulator has the characteristics of low voltage,low power consumption,high precision and good robustness. The modulator is powered by a 1.2 V low voltage,and it has an over-sampling ratio (OSR) of 128,a sampling frequency of 6.144 MHz,and a signal bandwidth of 20 kHz. Based on SMIC0.11 μm process,the layout design of Σ-Δ ADC modulator was completed,and the streaming chip was finally successful. The measurement results after chip streaming show that the signal-to-noise ratio of the modulator reaches 102.4 dB,the effective bit reaches 16.7 bit,the overall power consumption of the modulator is only about 1.17 mW,and the whole layout area of the modulator is only about 0.122 mm2. The measured performance of the modulator shows that it is a good choice for Σ-Δ ADC circuit in audio chip.

Key words:analog to digtial conversion;Σ-Δ modulator;low power;low voltage

隨着数字多媒体技术的迅猛发展,现代数字技术被广泛应用于大量的音频设备中. 现代数字电路的时钟越来越高且供电电压越来越低,这就给与之对应的模拟电路的设计提出了更高要求. 低电压下,虽然电路功耗会降低,但是许多传统的电路结构在低电压下无法工作,因此必须要设计在低电压下能较好工作的电路[1]. 音频设备中核心电路就是ADC电路,高品质的音频设备对ADC的精度和功耗要求较高. 在主流的ADC拓扑结构中,Σ-Δ ADC的精度最高. Σ-Δ ADC利用过采样和噪声整形技术将信号的处理转移到数字域上,极大降低了模拟电路的复杂度,减少了Σ-Δ ADC的功耗. 因此Σ-Δ ADC相较于其他ADC结构有更高的精度、更好的功耗特性和鲁棒性[2]. Σ-Δ ADC主要由模拟调制器和数字滤波器组成,模拟调制器是Σ-Δ ADC的核心电路[3]. 因此针对Σ-Δ ADC中调制器的设计,提出了一款低电压、低功耗、高精度的Σ-Δ ADC调制器. 本文通过改进调制器结构和系数来优化环路滤波器的传递函数,解决了传统调制器中输入信号范围限制问题,提高了电路的稳定性. 同时对调制器中的放大器和比较器电路进行优化设计,降低了调制器电路设计的复杂性和功耗. 在1.2 V低电压和SMIC0.11 μm工艺下,该调制器的有效位达到16位以上,电路功耗仅1.17 mW左右,版图面积为0.122 mm2左右.

1 调制器系统设计

1.1 结构设计

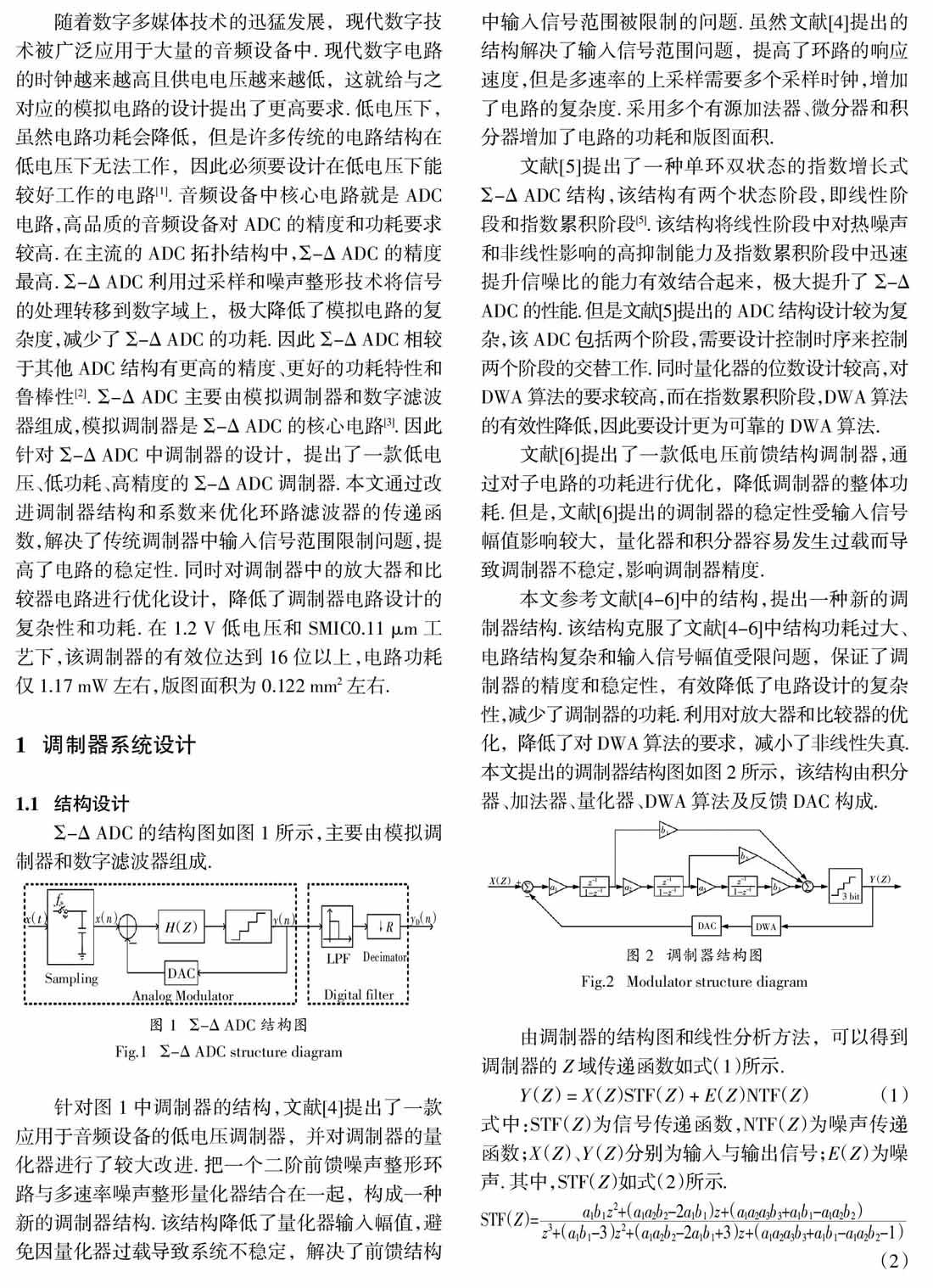

Σ-Δ ADC的结构图如图1所示,主要由模拟调制器和数字滤波器组成.

针对图1中调制器的结构,文献[4]提出了一款应用于音频设备的低电压调制器,并对调制器的量化器进行了较大改进. 把一个二阶前馈噪声整形環路与多速率噪声整形量化器结合在一起,构成一种新的调制器结构. 该结构降低了量化器输入幅值,避免因量化器过载导致系统不稳定,解决了前馈结构中输入信号范围被限制的问题. 虽然文献[4]提出的结构解决了输入信号范围问题,提高了环路的响应速度,但是多速率的上采样需要多个采样时钟,增加了电路的复杂度. 采用多个有源加法器、微分器和积分器增加了电路的功耗和版图面积.

文献[5]提出了一种单环双状态的指数增长式Σ-Δ ADC结构,该结构有两个状态阶段,即线性阶段和指数累积阶段[5]. 该结构将线性阶段中对热噪声和非线性影响的高抑制能力及指数累积阶段中迅速提升信噪比的能力有效结合起来,极大提升了Σ-Δ ADC的性能. 但是文献[5]提出的ADC结构设计较为复杂,该ADC包括两个阶段,需要设计控制时序来控制两个阶段的交替工作. 同时量化器的位数设计较高,对DWA算法的要求较高,而在指数累积阶段,DWA算法的有效性降低,因此要设计更为可靠的DWA算法.

文献[6]提出了一款低电压前馈结构调制器,通过对子电路的功耗进行优化,降低调制器的整体功耗. 但是,文献[6]提出的调制器的稳定性受输入信号幅值影响较大,量化器和积分器容易发生过载而导致调制器不稳定,影响调制器精度.

本文参考文献[4-6]中的结构,提出一种新的调制器结构. 该结构克服了文献[4-6]中结构功耗过大、电路结构复杂和输入信号幅值受限问题,保证了调制器的精度和稳定性,有效降低了电路设计的复杂性,减少了调制器的功耗. 利用对放大器和比较器的优化,降低了对DWA算法的要求,减小了非线性失真. 本文提出的调制器结构图如图2所示,该结构由积分器、加法器、量化器、DWA算法及反馈DAC构成.

由调制器的结构图和线性分析方法,可以得到调制器的Z域传递函数如式(1)所示.

Y(Z) = X(Z)STF(Z) + E(Z)NTF(Z) (1)

式中:STF(Z)为信号传递函数,NTF(Z)为噪声传递函数;X(Z)、Y(Z)分别为输入与输出信号;E(Z)为噪声. 其中,STF(Z)如式(2)所示.

式中:a1、a2、a3为调制器中积分器的级间增益系数;b1、b2、b3为调制器的前馈系数.

由式(2)可知,本文通过对调制器结构进行改进,使STF(Z)呈现低通特性. 相对传统的全通特性来说,对输入信号进行低通滤波,对输入信号中耦合的输入噪声进行了一定程度的抑制. 同时该结构减少了输入到加法器的前馈支路,降低了加法器输出信号的幅值,使得量化器不会因输入信号幅值过大而发生过载,既解决了输入信号范围限制的问题,也优化了调制器的整体功耗.

NTF(Z)为噪声传递函数,对调制器噪声进行处理,其式如(3)所示:

对于噪声传递函数,本文利用MATLAB设计式(3)噪声传递函数中的系数,保证噪声传递函数呈高通特性,实现调制器的噪声整形功能.

1.2 MATLAB建模设计

衡量调制器噪声性能的常用参数为信噪比,调制器信噪比大小由式(4)表示:

式中:n为量化位数;L为调制器阶数;OSR为过采样比.

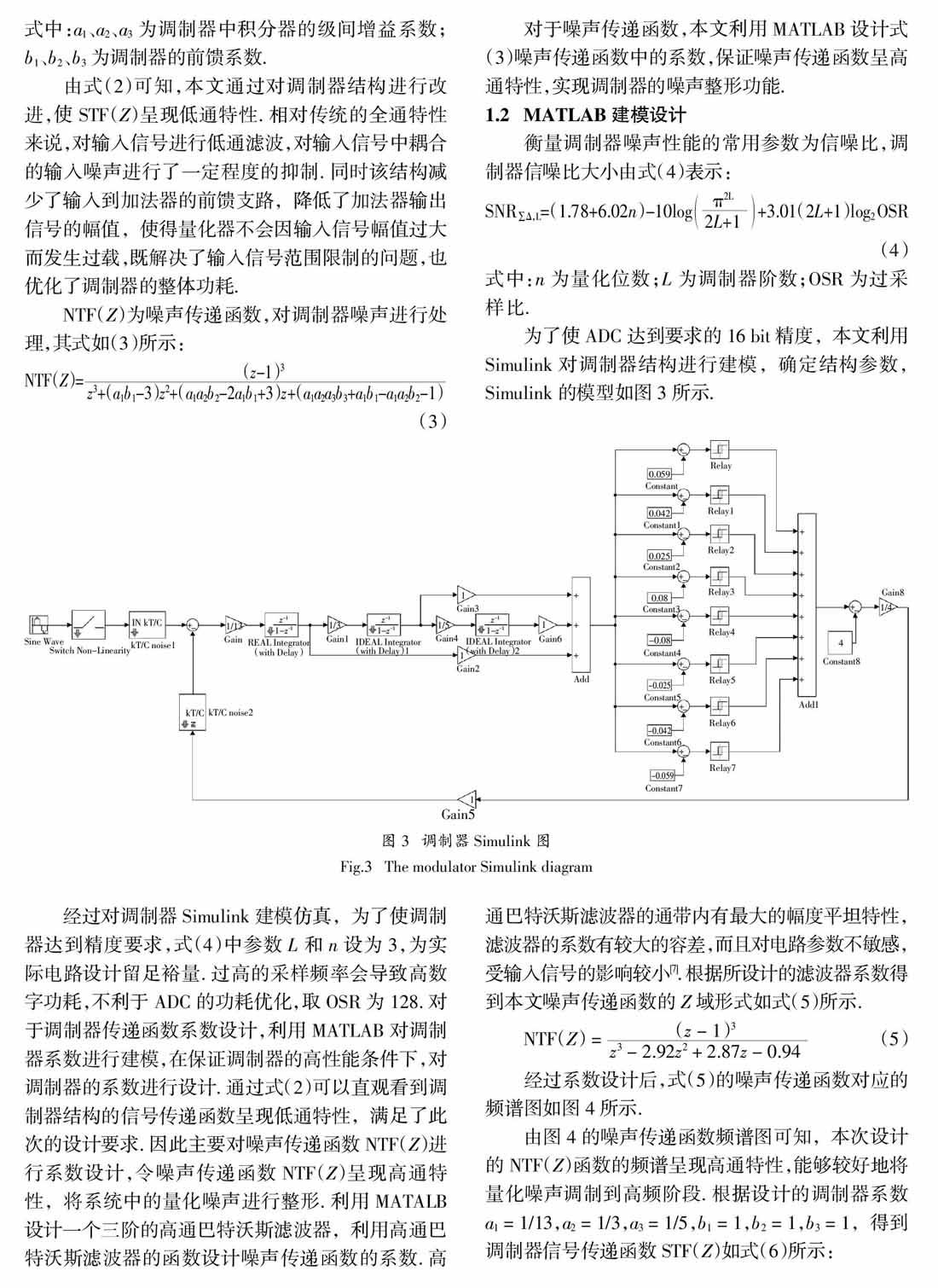

为了使ADC达到要求的16 bit精度,本文利用Simulink对调制器结构进行建模,确定结构参数,Simulink的模型如图3所示.

经过对调制器Simulink建模仿真,为了使调制器达到精度要求,式(4)中参数L和n设为3,为实际电路设计留足裕量. 过高的采样频率会导致高数字功耗,不利于ADC的功耗优化,取OSR 为128. 对于调制器传递函数系数设计,利用MATLAB对调制器系数进行建模,在保证调制器的高性能条件下,对调制器的系数进行设计. 通过式(2)可以直观看到调制器结构的信号传递函数呈现低通特性,满足了此次的设计要求. 因此主要对噪声传递函数NTF(Z)进行系数设计,令噪声传递函数NTF(Z)呈现高通特性,将系统中的量化噪声进行整形. 利用MATALB设计一个三阶的高通巴特沃斯滤波器,利用高通巴特沃斯滤波器的函数设计噪声传递函数的系数. 高通巴特沃斯滤波器的通带内有最大的幅度平坦特性,滤波器的系数有较大的容差,而且对电路参数不敏感,受输入信号的影响较小[7]. 根据所设计的滤波器系数得到本文噪声传递函数的Z域形式如式(5)所示.

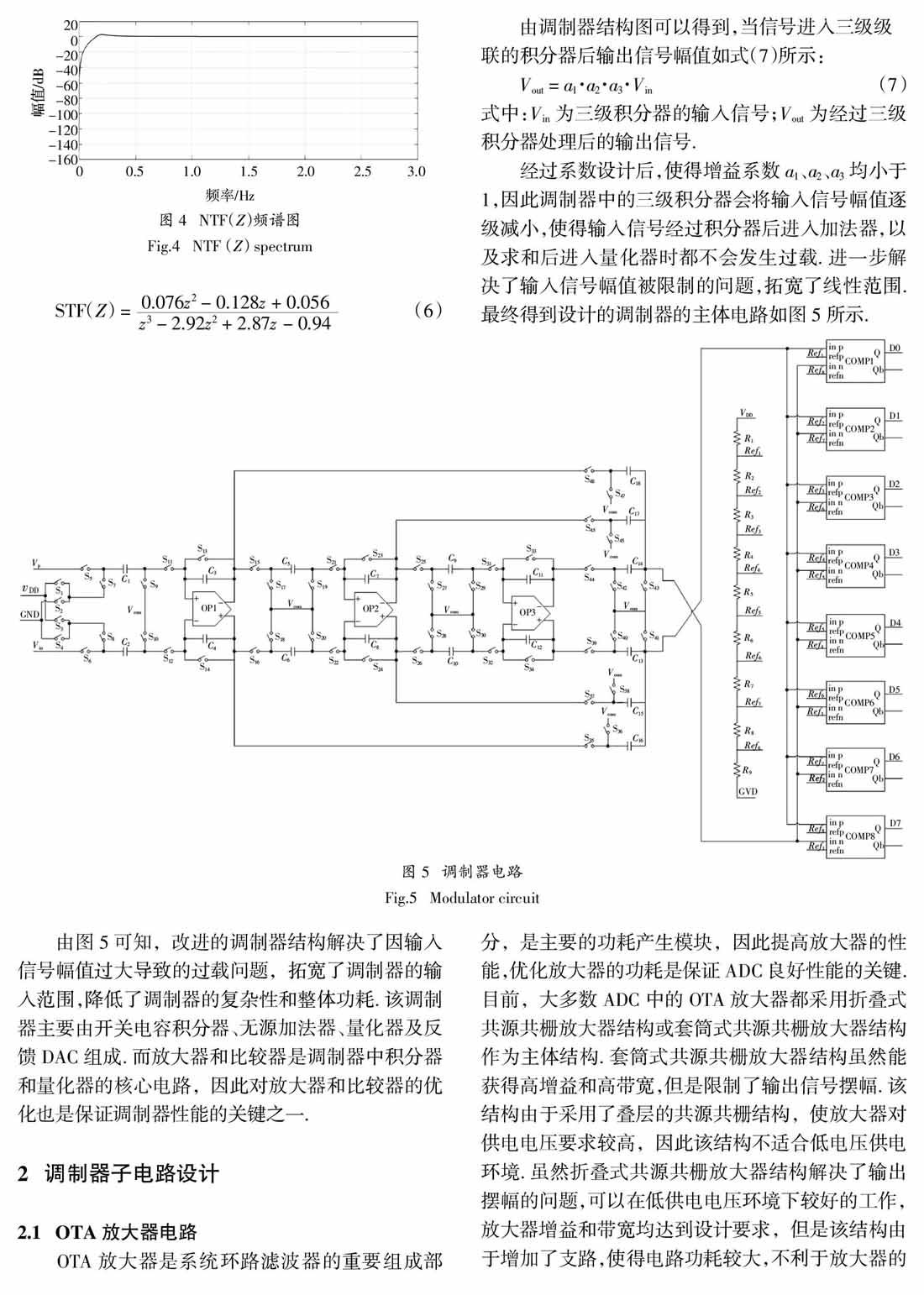

经过系数设计后,式(5)的噪声传递函数对应的频谱图如图4所示.

由图4的噪声传递函数频谱图可知,本次设计的NTF(Z)函数的频谱呈现高通特性,能够较好地将量化噪声调制到高频阶段. 根据设计的调制器系数a1 = 1/13,a2 = 1/3,a3 = 1/5,b1 = 1,b2 = 1,b3 = 1,得到调制器信号传递函数STF(Z)如式(6)所示:

由调制器结构图可以得到,当信号进入三级级联的积分器后输出信号幅值如式(7)所示:

Vout = a1·a2·a3·Vin (7)

式中:Vin为三级积分器的输入信号;Vout为经过三级积分器处理后的输出信号.

经过系数设计后,使得增益系数a1、a2、a3均小于1,因此调制器中的三级积分器会将输入信号幅值逐级减小,使得输入信号经过积分器后进入加法器,以及求和后进入量化器时都不会发生过载. 进一步解决了输入信号幅值被限制的问题,拓宽了线性范围. 最终得到设计的调制器的主体电路如图5所示.

由图5可知,改进的调制器结构解决了因输入信号幅值过大导致的过载问题,拓宽了调制器的输入范围,降低了调制器的复杂性和整体功耗. 该调制器主要由开关电容积分器、无源加法器、量化器及反馈DAC组成. 而放大器和比较器是调制器中积分器和量化器的核心电路,因此对放大器和比较器的优化也是保证调制器性能的关键之一.

2 調制器子电路设计

2.1 OTA放大器电路

OTA放大器是系统环路滤波器的重要组成部分,是主要的功耗产生模块,因此提高放大器的性能,优化放大器的功耗是保证ADC良好性能的关键. 目前,大多数ADC中的OTA放大器都采用折叠式共源共栅放大器结构或套筒式共源共栅放大器结构作为主体结构. 套筒式共源共栅放大器结构虽然能获得高增益和高带宽,但是限制了输出信号摆幅. 该结构由于采用了叠层的共源共栅结构,使放大器对供电电压要求较高,因此该结构不适合低电压供电环境. 虽然折叠式共源共栅放大器结构解决了输出摆幅的问题,可以在低供电电压环境下较好的工作,放大器增益和带宽均达到设计要求,但是该结构由于增加了支路,使得电路功耗较大,不利于放大器的低功耗设计[8-9].

综上所述,本文提出了一款低电压、低功耗的OTA放大器,在保证高增益和高带宽的条件下,既解决了输出摆幅的问题,又降低了放大器的功耗. 采用全差分的结构抑制输入1/f噪声,减少调制器的噪声成分. 本文设计的OTA放大器的电路结构如图6所示,图中VDD为电源电压,GND为电源接地端.

由图6所可知,在输入级中加入了M4、M5、M6管,此时OTA放大器的跨导如式(8)所示:

Gm = gm2 + gm4 (8)

式中:gm2和gm4分别为M2管和M4管的跨导.

OTA放大器的输出阻抗如式(9)所示:

Rout = [ gm2 ro9 ro7 ]//[ gm11 ro11 (ro13 // ro2 //ro4)] (9)

式中:gm9和gm11分别为M9管和M11管的跨导;ro2、ro4、ro7、ro9、ro11、ro13分别为对应编码MOS管的等效阻抗.

联立式(8)(9),得到OTA放大器的增益Av如式(10)所示:

Av = [ gm2+gm4 ][ gm9 ro9 ro7 //gm11 ro11 (ro13 // ro2 //ro4)] (10)

根据式(8)(9)(10)可知,当IM4、IM5的电流增加,IM13、IM14的电流减少时,放大器的整体跨导和输出阻抗都迅速增大,因此放大器的增益得到极大提高. 可以通过对M13和M5管所在支路电流的分配,来控制OTA放大器的增益和带宽. 该结构在保证高增益和带宽的条件下,既解决了输出电压摆幅的问题,也减小了流入M13和M14管所在支路的电流,降低了OTA放大器的功耗.

设计开关电容共模负反馈作为放大器的共模稳定电路,共模输出如式(11)所示:

式中:Voutp和Voutn均为放大器的差分输出信号;Vref为参考电压;Vbias为偏置电压. 若电容C1 = C4,则式(11)可用式(12)表示

由式(12)可知,开关电容共模负反馈实现了放大器对共模负反馈的全部要求. 相较于传统开关电容共模负反馈来说,简化了电路结构,电容数量减少了一半,减少了版图面积,动态开关电容功耗极小,对放大器的功耗进行了优化. 本文设计的放大器与文献中放大器指标对比如表1所示.

从表1可以看出,本文改进后的放大器在增益和带宽满足设计要求的情况下,相较其他文献的比较器来说,功耗有较大优化.

2.2 比较器电路

目前,在大多数调制器中采用全动态比较器,文献[10]提出了对全动态比较器改进的电荷分享型动态比较器. 虽然这些比较器的响应速度较快,功耗较低,但是纯动态比较器没有明确的工作点,该比较器的噪声比较复杂,且对工艺和寄生效应都较为敏感[11-12].

本文提出了一种改进的比较器结构,在比较器中加入中间级,既克服了纯动态比较器中噪声和寄生效应的影响,又保证了比较器的响应速度和低功耗特性. 比较器电路如图7所示.

从图7可以看出,比较器电路主要由预放大级、比较级和输出缓冲级构成. 同时考虑比较器前级积分器为全差分输出,因此动态比较器采用4路的输入结构. 其中时钟track、latchb、latch来控制比较器的工作模式,时钟图如图8所示.

由图7和图8可知,比较器的工作包括两个阶段,即跟随阶段和锁存比较阶段. 当比较器处于跟随阶段即时钟中的Tracking mode段时,预放大级中的M10、M11截止且M14、M15导通,比较级中M27、M28截止. 比较级的输出恒定为高电平,比较器跟随预放大级输出. 预放大级开始对输入信号进行放大,将输入信号(Vinp-Vinn)-(Vrefp-Vrefn)放大至比较级能识别的大小. 当比较器处于锁存比较阶段即时钟中的latching mode段时,预放大级的M10、M11导通且M14、M15截止,比较级的M27、M28导通. 比较级形成正反馈将预放大级的输出迅速拉至逻辑电平对应的电压大小,完成对输入信号的比较. 同时由于M14和M15截止,使得比较级中的回踢噪声无法传回预放大级,减少了比较器中的回踢噪声. 由于该比较器只在预放大期间即Tracking mode段消耗功耗,因此整个比较器的功耗极低. 该比较器指标与其他文献对比如表2所示.

由表2可知,本文设计的比较器相较于文献[10]和文献[11],在功耗和精度上有很大程度的改善,尤其在功耗上有较大优化.

3 调制器的测试结果

调制器设计是基于SMIC0.11 μm的器件工艺,在调制器电路完成后,对调制器电路进行版图设计. 并在版图完成后对版图进行设计规则验证(Design Rules Check,DRC)和版图与电路匹配性验证(Layout Versus Schematic,LVS),保证版图的准确性和可靠性. 在DRC和LVS验证完成后,得到调制器电路的最终版图如图9所示,版图面积为0.122 mm2左右.

在完成版图设计和后端设计后,对芯片进行流片. 在电源电压为1.2 V,采样频率为6.144 MHz,过采样比为128,输入信号幅值为1 V,频率为1 kHz的正弦信号的测试条件下,对芯片中的Σ-Δ ADC调制器进行测试. 经过测试得到调制器的功耗仅为1.17 mW左右. 将调制器的输出结果导入MATLAB进行FFT分析,计算调制器的信噪比. 经过FFT分析后,可以得到调制器的功率谱图如图10所示.

由图10可知,调制器中产生的量化噪声成功地被调制到了高频段,达到了噪声整形和过采样对噪声的处理效果. 被调制到高频段的量化噪声最终将被Σ-Δ ADC后级的数字滤波器滤除,极大地提高了ADC的噪声性能. 经过计算得到调制器的信噪比达到102.4 dB,有效位达到16.7位,满足了音频应用领域对调制器精度的设计要求. 该调制器与其他文献中调制器的性能指标的对比如表3所示.

其中,表3中品质因数(FOMs)如式(13)所示:

式中:SNDR为信噪失真比;BW为信号带宽;power为功耗.

由表3可知,本文提出的调制器指标相比其他文献中的调制器指标来说,在信噪比和FOMs值接近的情况下,功耗和版图都有较大优化,在1.2 V的低电压下能较好的工作.

4 结 论

本文基于SMIC0.11 μm工艺,设计了一款改进的单环三阶三位量化的Σ-Δ ADC调制器,能够较好地应用于音频领域. 通过对调制器结构和系数的优化,解决了大多数调制器结构中因过载导致的系统不稳定问题,拓宽了输入信号的范围,进一步提高了调制器的噪声性能. 同时改进了比较器和OTA放大器,极大程度降低了调制器的功耗,提高了调制器的响应速度. 芯片的成测结果表明,该调制器在电源电压为1.2 V,采样频率为6.144 MHz,过采样比为128的条件下,调制器的信噪比达到102.4 dB,有效位達到16位以上,而调制器的功耗仅为1.17 mW左右,版图面积为0.122 mm2,实现了高精度、低功耗和低电压的设计目标.

参考文献

[1] KOZLOV S A,PILIPKO M M. A second-order sigma-delta modulator with a hybrid topology in 180nm CMOS[C]//2020 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus). Petersburg and Moscow:IEEE,2020:144—146.

[2] 杨岱. 音频编解码芯片中的Sigma-Delta ADC的设计[D]. 成都:电子科技大学,2018:6—8.

YANG D. Design of Sigma-Delta ADC in audio codec chip[D]. Chengdu:University of Electronic Science and Technology of China,2018:6—8. (In Chinese)

[3] 周志兴,来强涛,姜宇,等. 一种应用于角度传感器的Sigma Delta ADC设计[J]. 微电子学与计算机,2019,36(8):25—29.

ZHOU Z X,LAI Q T,JIANG Y,et al. Design of Sigma Delta ADC for angle sensor[J]. Microelectronics & Computer,2019,36(8):25—29. (In Chinese)

[4] CHO J S,RHEE C,KIM S,et al. A 1.2-V 108.9-dB A-weighted DR 101.4-dB SNDR audio Sigma-Delta ADC using a multi-rate noise-shaping quantizer[J]. IEEE Transactions on Circuits and Systems II:Express Briefs,2018,65(10):1315—1319.

[5] WANG B,SIN S W,U S P,et al. A 550 μW 20-kHz BW 100.8-dB SNDR linear- exponential multi-bit incremental Sigma-Delta ADC with 256 clock cycles in 65-nm CMOS[J]. IEEE Journal of Solid-State Circuits,2019,54(4):1161—1172.

[6] SU P H,CHIUEH H. The design of low-power CIFF structure second-order sigma-delta modulator[C]//2009 52nd IEEE International Midwest Symposium on Circuits and Systems. Cancun,Mexico:IEEE,2009:377—380.

[7] 刘志明. 16比特低功耗音频应用Sigma-DeltaADC研究[D]. 合肥:中国科学技术大学,2010:17—26.

LIU Z M. Research on 16-bit low-power audio application Sigma-DeltaADC[D]. Hefei:University of Science and Technology of China,2010:17—26. (In Chinese)

[8] 王江涛,李海启,宋焱,等. 2.2 MHz,8.3 mW多位量化连续时间Sigma-Delta 调制器设计[J]. 微电子学与计算机,2014,31(8):10—14.

WANG J T,LI H Q,SONG Y,et al. A 2.2 MHz,8.3 mW multi-bit continuous-time Sigma-Delta modulator[J]. Microelectronics & Computer,2014,31(8):10—14. (In Chinese)

[9] TRAN B,HUYNH C. A 12-bit 33-mW and 96-MHz discrete-time sigma delta ADC in 130 nm CMOS technology[C]//2019 International Symposium on Electrical and Electronics Engineering (ISEE). Ho Chi Minh City,Vietnam:IEEE,2019:1—6.

[10] AZIZI N I M,RUSLAN S H. Design of a low power 0.25 μm CMOS comparator for Sigma-Delta analog-to-digital converter[C]//2015 IEEE Student Conference on Research and Development (SCOReD). Kuala Lumpur,Malaysia:IEEE,2015:638—642.

[11] SANDHYA L. High speed latched comparator in 0.35 μm CMOS process[C]//2015 Global Conference on Communication Technologies (GCCT).Thuckalay,India:IEEE,2015:150—154.

[12] 殷湛,郭立,楊吉庆. 一种用于流水线ADC的高速电压比较器[J]. 微电子学与计算机,2006,23(2):182—184.

YIN Z,GUO L,YANG J Q. A high-speed voltage comparator for pipeline ADC[J]. Microelectronics & Computer,2006,23(2):182—184. (In Chinese)

收稿日期:2020-10-19

基金项目:国家自然科学基金资助项目(61873196),National Natural Science Foundation of China(61873196)

作者简介:张涛(1967—),男,湖北武汉人,武汉科技大学教授,博士

通信联系人,E-mail:2326996855@qq.com