一种基于Aurora协议的多通道数据传输系统设计

中电科思仪科技股份有限公司 焦志超

本文针对在数字类产品测试中对高速多通道并行信号处理的要求,设计了一种基于PCIe和Aurora协议的串行数据传输系统。该系统采用FPGA芯片作为控制中心和信号处理中心,利用高速串行接口来传输数据,FPGA内各IP模块间的通信基于AXI总线实现。该技术在数字通道板卡设计中得到了成功应用。

数字类产品的功能验证是其设计、生产、故障检测过程的重要组成部分。随着被测产品工作速率的提高和测试接口的增多,在其测试验证中需要能够产生高速多通道激励,并接收高速多通道响应的数据传输系统,由上位机软件控制测试过程和显示测试结果。本文针对以上需求,基于FPGA芯片和PCIe 、Aurora协议设计了一种多通道数据传输系统,重点针对FPGA中高速串行收发器(GTH)的应用方案进行了分析,解决了多通道高速数字信号传输问题,对芯片或板卡间多通道高速传输技术的研究和数字系统相关测试设备的设计具有一定的理论和实践意义。

1 系统方案设计

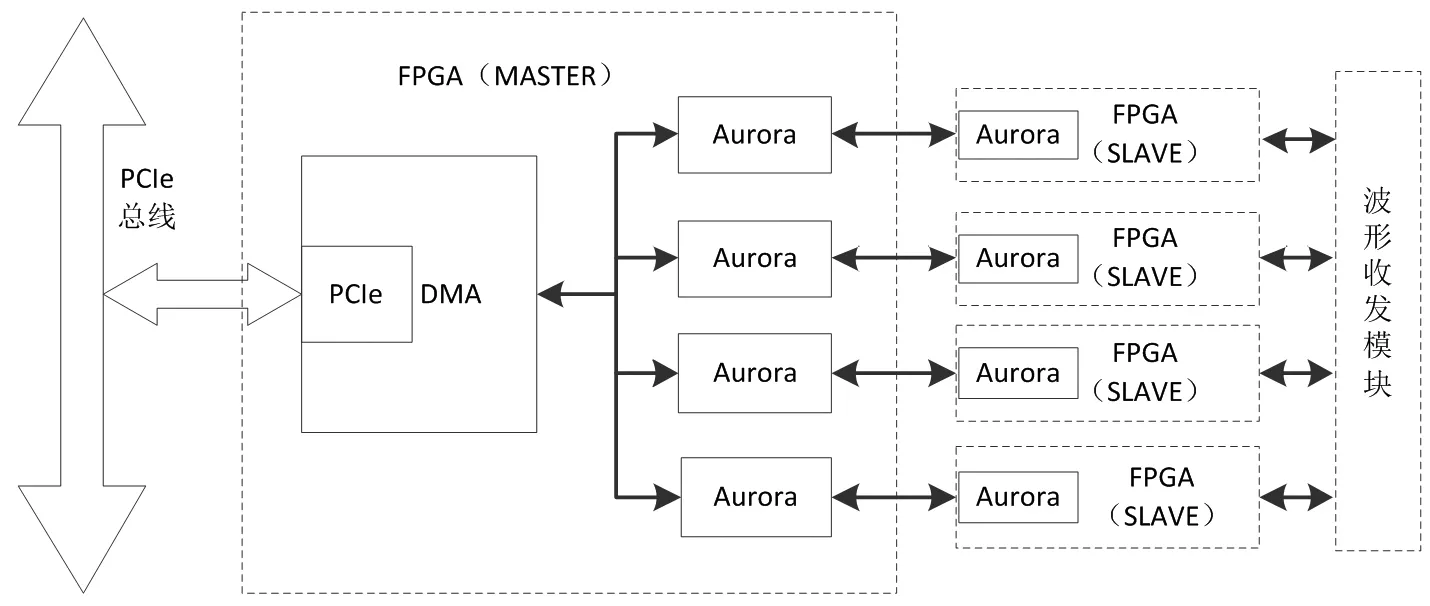

本系统利用Xilinx公司的FPGA作为主控芯片,利用FPGA实现高速多通道信号的激励发送和响应采集功能,系统的总体框图如图1所示。FPGA分为主控芯片和多通道数据处理芯片,其中,主控芯片作为主设备称为MASTER芯片,多通道数据处理芯片称为SLAVE芯片。主控芯片负责与上位机间通过PCIe接口在DMA模式下进行测试数据的传输,并负责控制命令的传输,主控芯片和数据处理芯片间通过Aurora进行数据交互。受FPGA芯片资源的限制,单片FPGA无法实现多通道的测试和数据存储需求,这里采用四个数据处理芯片共实现64个通道数据的发送和采集,每片FPGA负责16通道的数据发生、采集和存储操作等功能。数据处理芯片通过64路高速HP IO发送激励信号,可实现测试系统对单通道数据率800Mbps的指标要求。数据处理芯片经过数字波形收发电路模块与被测系统相连,对被测系统施加激励并对被测系统的响应信号进行采集。

图1 多通道数据传输系统结构图

2 主控FPGA的设计

主控FPGA与上位机间通过PCIe总线进行数据传输,PCIe2.0下单通道传输速率可达500MB/s,多通道数据率为单通道数据率乘以通道数,如×8通道的数据率可达4GB/s。FPGA间采用Aurora协议进行通信,Aurora协议是由Xilinx公司提供的一个开放、免费的链路层协议,可以用来进行点到点的串行数据传输,在实现高性能数据传输系统设计中具有高效率和简单易用的特点。本文采用Xilinx提供的IP核,该核用Aurora64B/66B协议将物理层高速串行收发器的操作进行封装,方便用户进行上层设计,Kintex UltraScale系列的xcku060 FPGA可支持单通道传输速率最大为16.375Gbps。PCIe的接口采用的是AXI4的总线模式,该总线广泛适用于数据高速传输场合,设计中各模块数据接口都采用AXI4作为通信接口,为此选用Chip2Chip核,实现PCIe与Aurora间的AXI通信。在主控FPGA中Chip2Chip核配置为主模式。

3 数据处理FPGA的设计

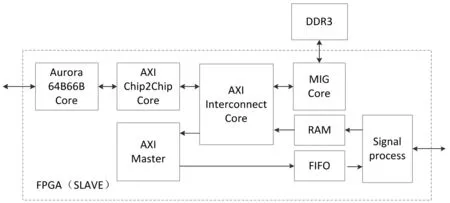

数据处理FPGA通过Aurora64B/66B核与主控FPGA相互连接,同样采用Chip2Chip核为Aurora64B/66B核和后端数据存储单元提供桥接作用,此处Chip2Chip核配置为从模式。Chip2Chip通过AXI4总线经过AXI Interconnect Core与MIG核相连,对DDR3存储器进行读写。其中,AXI Interconnect Core实现数据宽度和时钟速率的转换,实现信号跨时钟域的设计,DDR3实现对原始激励信号的存储,此处选用的DDR3内存条可存储4GB的测试数据。数据发生时,需要主机模式的AXI接口读数据模块AXI Master对DDR3进行数据读取。数据经过FIFO缓存后,以测试中所要求的数据发生速率进入信号处理模块,经过编码等处理后得到最终发送的激励波形数据。被测系统在激励信号的作用下产生的响应信号经过HP IO进入数据处理FPGA,信号处理单元对响应信号进行比对分析,得出发生故障的通道和故障数据对应的激励数据等最终的测试结果。测试结果经过Chip2Chip核和Aurora64B/66B传回主控FPGA,并通过PCIe接口上传到上位机,生成测试结果文件,并在上位机软件中进行显示。数据处理FPGA设计框图如图2所示。

图2 数据处理FPGA设计框图

4 Aurora的主从核设计

本设计中为达到64个通道的数据传输,共采用了4片数据处理FPGA,每片数据处理FPGA负责16个通道的数据处理。与4片数据处理FPGA的连接需要占用主控FPGA的GTH接口, PCIe接口也要占用主控FPGA的GTH接口。FPGA每个串行高速收发Quad中包含四个串行高速收发器Channel和一个Common模块,Common模块能够为高速收发器提供数据率较高的高性能时钟支持。为合理使用主控FPGA有限的GTH接口资源和其中的Common模块资源,保证主控FPGA与数据处理FPGA间的高速率传输,本文的Aurora采用了主从核的设计方案。设计框图中每个Quad采用了一个Aurora主核和一个Aurora从核,主从核共享一个Common模块,每个核占用两个高速收发器Channel,主控FPGA的两个高速收发器Quad资源实现了与后端4片FPGA的高速稳定传输。

5 IBERT在系统设计中的应用

IBERT(Bit Error Ratio Tester)是Xilinx为调试FPGA芯片内高速串行接口比特误码率性能所提供的工具,通过IBERT IP核我们可以对FPGA高速收发器硬件接口进行误码率测试、调整收发器参数配置,并能方便准确地进行眼图扫描,验证硬件PCB信号完整性和硬件数据传输的可靠性和稳定性,可应用于设计的故障定位。

在IBERT配置界面中可选择合适的传输协议、速率、参考时钟、回环模式,并能快速完成摆幅、预加重等参数的设置,发送器发送伪随机码,接收器接收并将信号进行解析后检查数据的正确性,并观察信号眼图是否满足设计要求。从信号完整性角度来看,眼睛睁的越大,表明PCB板信号完整性越好,信道质量越好。通过测试,链路处于正常状态,且得到了清晰的眼图,眼图张开率为77.78%,没有出现接收数据错误。

结语:本文基于FPGA芯片,采用PCIe、Aurora协议设计了一种高速多通道数据传输系统。分析了主控FPGA和数据处理FPGA的具体设计方案,该技术方案可应用于多路高速信号传输和相关数字系统测试的应用领域,其中,基于AXI4的IP核互联方法具备较高的传输效率和可靠性,并极大提高了设计开发效率,Aurora协议和IBERT工具可广泛应用于FPGA在高速数据传输的应用场合。该设计提升了传输效率,扩展了测试通道数,可满足大数据存储深度和多管脚测试需求,进而提高了数字系统产品测试、故障分析的效率。