基于cascode结构的Ka频段CMOS功率放大器设计

甄建宇 陈娜

摘 要:文章通过分析共源共栅功率放大器的基本原理,提出了一种新颖的基于cascode级间电路结构,通过优化电路级间的阻抗匹配的设计思路。同时采用55 nm RF CMOS硅基工艺设计并制作出一款工作于Ka频段的功率放大器。与传统的CMOS功率放大器相比,具有高增益、低功耗、高功率等特点。经过实物加工及裸片测试,结果表明设计的功率放大器在工作频率为27~32 GHz时,小信号增益为19~20 dB,输出1 dB压缩点为12 dBm,最大饱和输出功率为15 dBm,最大功率附加效率为21.5%,该放大器芯片尺寸为780 μm×710 μm。

关键词:功率放大器;共源共栅;CMOS

中图分类号:TN722 文献标识码:A 文章编号:2096-4706(2021)05-0060-04

Design of Ka Frequency Band CMOS Power Amplifier Based on cascode Structure

ZHEN Jianyu1,CHEN Na2

(1.The 13th Research Institute of China Electronics Technology Group Corporation,Shijiazhuang 050051,China;

2.CEIEC,Beijing 100036,China)

Abstract:By analyzing the basic principle of cascode power amplifier,this paper proposes a novel design idea based on cascode interstage circuit structure,which optimizes the impedance matching between circuit stages. At the same time,a power amplifier working in Ka frequency band is designed and manufactured by using 55 nm RF CMOS silicon based process. Compared with the traditional CMOS power amplifier,it has the characteristics of high gain,low power consumption and high power. After physical processing and wafer testing,the results show that the power amplifier designed in this paper has a small signal gain of 19~20 dB,an output compression point of 1 dB of 12 dBm,a maximum saturated output power of 15 dBm,a maximum power additional efficiency of 21.5%,and a chip size of 780 μm×710 μm when the operating frequency is 27~32 GHz.

Keywords:power amplifier;cascode;CMOS

0 引 言

由于采用硅基CMOS工藝生产的器件具有低成本、高集成度的特点,对于使用该类器件研发的通信设备来说,体积得以大幅缩小,生产成本也得以大大降低,因此硅基CMOS器件的研发越来越受重视。随着我国无线通信技术及相控阵雷达的高速发展,总体针对设备小型化、轻量化以及多功能化的需求越来越迫切,要求也越来越高。硅基电路以其性能和集成度的优势备受青睐,在很多无线设备应用中发挥着不可替代的作用。其中作为关键器件的CMOS射频功率放大器,特别是在Ka频段的应用前景变得更加地广阔,市场对该频段的功率放大器性能的要求也愈加严苛。

共源共栅(cascode)结构是一种设计功率放大器常用的电路结构。该结构可以有效地提升功率放大器的耐受电压,从而达到提高功率放大器输出功率的效果。cascode结构是采用共源放大器与共栅放大器直接级联的方式,使得最终设计出的功率放大器具有较高的反向隔离度以及更高的稳定性。但是由于功率放大器的反向隔离度以及稳定性受器件本身寄生参数的影响,因此在采用cascode结构设计功率放大器时,电路级间的阻抗匹配问题需要特殊考虑。部分文献[1]中也提出了各种优化cascode电路级间匹配的思路,从而达到提高功率放大器的增益、效率以及扩展工作带宽的目的。

本文通过对cascode功率放大器结构的基本原理进行研究,提出了一种新颖的级间匹配电路结构。具体的方法是采用电感-电容并联到地的方式,与器件的寄生参量共同形成一个阻抗匹配网络,从而达到提高功率放大器在工作频带内带内平坦度的目的,最终使得采用了上述结构的功率放大器在相对较宽的工作频带内实现了高增益、高功率的设计指标。与传统结构的功率放大器相比,采用上述方法所设计出来的功率放大器性能更优,具有更加广阔的应用前景。

1 Ka频段CMOS功率放大器的设计

1.1 cascode放大器的基本原理

cascode放大器结构由于采用了两层晶体管堆叠级联的形式,使其具有一个重要特性,即该结构的输出电阻很高。在忽略掉共栅晶体管的背栅效应的影响下,cascode放大器结构的小信号等效电路如图1所示。

cascode放大器除了具有输出阻抗高的固有特性,其电压增益也相对较高,因此可以通过提高放大器的耐受电压,达到提高放大器输出功率的目的。

1.2 电路拓扑设计

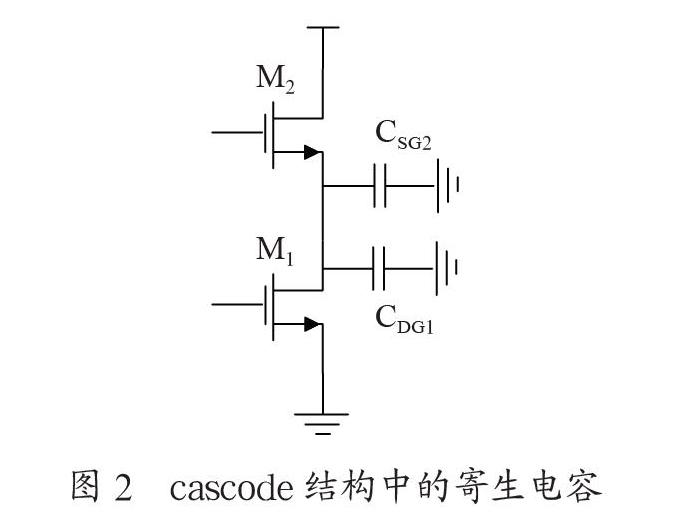

采用cascode结构放大器的电路中,共源级晶体管M1的漏极和共栅级晶体管M2的源极与地之间各有一个旁路寄生电容,如图2所示。CSG1为晶体管M1漏极对地寄生电容,CSG2为晶体管M2源极对地寄生电容,它们的存在给放大器带来额外的失配损耗,寄生参数的存在,很大程度上恶化了功率放大器的增益以及放大器输出功率[5]。因此,采用传统cascode结构的功率放大器为了提高其输出功率,往往解决方法是进一步增加该放大器的功耗,但是这样却带来了放大器效率降低的问题。

从图1中可以看出,cascode放大器的输出阻抗主要是由两部分构成,一部分为共栅级晶体管本身的输出阻抗,另一部分为其源端的共源级晶体管的负反馈阻抗[2,3]。通过理论分析,可以得出该结构的输出阻抗为:

Rout=[1+gm2ro2]ro1+ro2 (1)

当gm2ro2?1时,从式(1)中可以近似得到Rout≈gm2ro2ro1。从而可以看出,通过共栅级晶体管的作用,cascode放大器结构的输出阻抗相比于共源级放大器结构的输出阻抗扩大了gm2ro2倍[4],由于共栅级晶体管的源极到漏极电流增益不变,所以整体结构的跨导为gm1,那么cascode放大器的电压增益可以表示为:

Av=-gm1Rout=-gm1gm2ro1ro2 (2)

针对本文设计的Ka频段cascode结构功率放大器,由于该功率放大器的工作频率相对较高,器件的寄生参数对功率放大器本身的影响会更加的严重。因此,为了得到功率放大器的高增益、高功率以及低功耗性能,改进的方法是通过在两个晶体管级联处增加一个“电感-电容”并联到地的支节电路,与器件的寄生电容共同形成了一个匹配网络,通过对器件参数的调整,实现优良的级联匹配。改进后的cascode结构如图3所示。采用了如图3所示的“电感-电容”支节电路的功率放大器,其电路指标与传统结构的功率放大器相比较,具有较高增益、较高功率、较低的功耗以及更优的带内平坦度。

在毫米波CMOS功率放大器的设计中,由于提供给器件使用的电压较低,如果采用多通道功率合成的方式增大功率,则需要很大的电流,从而会导致器件的寄生参数对放大器性能的影响更为严重。考虑到上述因素,本文设计采用两级各两层堆叠的cascode结构,并加入改进的级间匹配网络,在保证前后晶体管的正常工作电压的同时,降低由阻抗变换带来的影响,最终设计的放大器电路原理图如图4所示。为了实现增加放大器工作频带带宽,同时提高带内增益平坦度的目的,在不影响整个放大器输出功率的前提下,位于前级的cascode结构引入电容-电阻负反馈结构。该结构也有利于提升整个电路的稳定性。在设计中综合考虑放大器功率及增益等因素,对末级晶体管栅宽大小进行了优化,最终确定的末级NMOS的总栅宽为176 μm,饱和电流可以达到40 mA,可以提供相应的功率能力。

1.3 版图设计及电路制作

本文设计采用cascode结构运用到Ka频段CMOS功率放大器的电路设计,通过国内某专用仿真软件进行放大器的原理图设计及版图验证工作,无源器件版图的EM仿真采用某三维电磁场软件进行,本文中芯片所用55 nm RF CMOS工艺共有8层金属可供走线,上面两层金属较厚,方阻较小,比较适合用作低损耗的射频走线[6-8],射频信号的传输采用共面波导及微带线结构,直流偏置电路采用了电阻线性分压的方式提供,放大器电路电源电压为2.5 V。通过合理的改进传统cascode电路拓扑,并对输入、输出以及级间匹配网络进行深入优化,最终达到了高增益、高功率、低功耗的设计指标。电路仿真结果表明,上述结构的功率放大器在工作频率为27~32 GHz内,小信号增益为21.5~22.5 dB,输出1 dB压缩点为12.5 dBm,最大饱和输出功率为15.5 dBm,最大功率附加效率为22%,动态工作電流为56 mA。达到了预期的设计目标值。最终将其加工成芯片,实物照片如图5所示,整个芯片面积为780 μm×710 μm。

2 实验结果

本文采用了Cascade Microtech探针台和矢量网络分析仪组成的微波测试系统对放大器实物进行裸芯片测试,最终的测试结果为:在工作频带27~32 GHz内,电路小信号增益为19~20 dB,最大饱和输出功率为15 dBm,最大功率附加效率为21.5%,输入、输出端口回波损耗均小于-15 dB。动态工作电流测试结果为59 mA。芯片最终的测试曲线如图8所示。

通过对功率放大器芯片的实测数据与电路仿真数据进行比对分析,得出的结论是本文设计的功率放大器在小信号下增益的实测值与仿真值偏离2~3 dB,功率相差0.5 dB,实测效率比仿真效率低1~2个百分点,端口驻波良好。整体的测试数据与仿真数据相近,增益偏差略大,分析造成这一问题的主要原因可能是由于加工实物中的电感及射频走线的损耗相比于仿真电路中电感及射频走线的损耗较大所导致的。

3 结 论

本文针对无线通信对高集成度、低成本、高性能的功率放大器的应用需求,成功研制了一款工作频段为27~32 GHz的CMOS功率放大器,与传统的CMOS功率放大器相比,实现了高增益、低功耗以及高功率的性能指标。本文设计中采用了两级各两层堆叠的cascode结构,前级引入了负反馈技术提高了放大器的带内平坦度,增强了电路稳定性。电路的测试结果与仿真结果符合较好,反映出本文所使用的新型结构及电路设计方法的正确性。该款硅基功率放大器对以后工作频段为Ka频段的电路设计起到了指导性的作用,为后期该频段的硅基高频、宽带多功能芯片的集成开发奠定了基础。本文设计的放大器在宽带设计上仍有一定的提升空间,下一步的工作主要是将其频段拓展到整个Ka频段带宽中,并在模型的仿真准确度上做进一步工作。

参考文献:

[1] 池保勇,余志平,石秉学.CMOS射频集成电路分析与设计 [M].北京:清华大学出版社,2006.

[2] CHEN T,SUN X,WU J,et al. A 2.4 GHz GaAs HBT stacked power amplifier with inductance compensation [J].IEICE Electronics Express,2013,10(16):2-5.

[3] JEONG G H,JOO T,HONG S C. A Highly Linear and Efficient CMOS Power Amplifier With Cascode–Cascade Configuration [J].IEEE Microwave and Wireless Components Letters,2017,27(6):596-598.

[4] CHANG M,REREIZ G M. A 26 to 40GHz Wideband SiGe Balanced Power Amplifier IC [C]//2007 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium.Honolulu:IEEE,2007:729-732.

[5] XIA J J,CHUNG A,BOUMAIZA. 25% PAE in 45nm SOI CMOS [C]//2017 IEEE MTT-S International Microwave Symposium (IMS).Honolulu:IEEE,2017:1691-1694.

[6] PIERCO R,TORFS G,KEULENAER T D,et al. A Ka-band SiGe BICMOS power amplifier with 24 dBm output power [J].Microwave and Optical Technology Letters,2015,57(3):718–722.

[7] 王尊峰,楊保国,马景芳.基于TRL校准的夹具测试技术浅析 [J].国外电子测量技术,2017,36(7):110-113.

[8] LIANG Y,LI N,WEI F,et al. A 60GHz digitally-assisted power amplifier with 17.2dBm Psat,11.3% PAE in 65nm CMOS [J].2015 IEEE MTT-S International Microwave Symposium.Phoenix:IEEE,2015:1-4.

作者简介:甄建宇(1987—),男,汉族,河北张家口人,工程师,硕士研究生,研究方向:微波毫米波集成电路设计。