UHF RFID 芯片内置低误差低调制深度ASK 解调器

李青龙,徐 勇,李 峤,彭 堃,张 显

(陆军工程大学通信工程学院,江苏 南京 210007)

射频识别(Radio Frequency Identification,RFID)技术依靠无线电波在读写器与标签芯片间实现非接触式数据交换和目标识别。超高频段(UHF,300 MHz~3 GHz)射频系统具有识别距离远、传输速度快、安全稳定等特点,广泛应用于交通运输、物品管理和安全控制等各领域[1-2]。目前UHF RFID 系统的国际主流标准和国家标准分别是ISO/IEC 18000-6C 和GB/T 29768-2013,综合两标准可知系统前向链路信号是经振幅键控(ASK)调制并以30%~100%为调制深度的已调波,其基带信号频率为40~160 kHz[3]。

将接收到的射频信号解调成基带信号是标签芯片的首要工作,因此信号解调的准确与否极其关键。标签芯片ASK 信号解调的一般步骤是先提取包络,再进行比较判别。包络检波器可分为无源和有源两种:文献[4-5]中的检波电路为典型的无源检波器,该电路适用于低功耗场景;文献[6-7]采用有源检波结构,通过电压补偿减小了MOS 管阈值对解调的影响。比较参考值的产生也具有多种方式:文献[5]通过RC 低通滤波来获得参考电压;文献[8]将RC 低通滤波器中的电阻改由二极管连接的MOS 管来实现;文献[9]提出了一种无二极管无电阻的参考电平产生电路;文献[6]提出的峰值检测器克服了传统低通滤波器的局限,产生的参考值可准确跟踪射频信号电平。

针对UHF RFID 标签芯片无源且接收的信号能量变化的特点,本文设计的解调器采用了不接入工作电源,即不消耗电源功率的无源包络检波和限幅电路,同时采用了基于峰值和谷值检测的参考电压产生器,能处理幅值大范围变化和多种调制深度、多种信号速率的射频信号,其性能满足ISO/IEC 18000-6C 和GB/T 29768-2013 协议要求。

1 UHF RFID 信号解调器设计

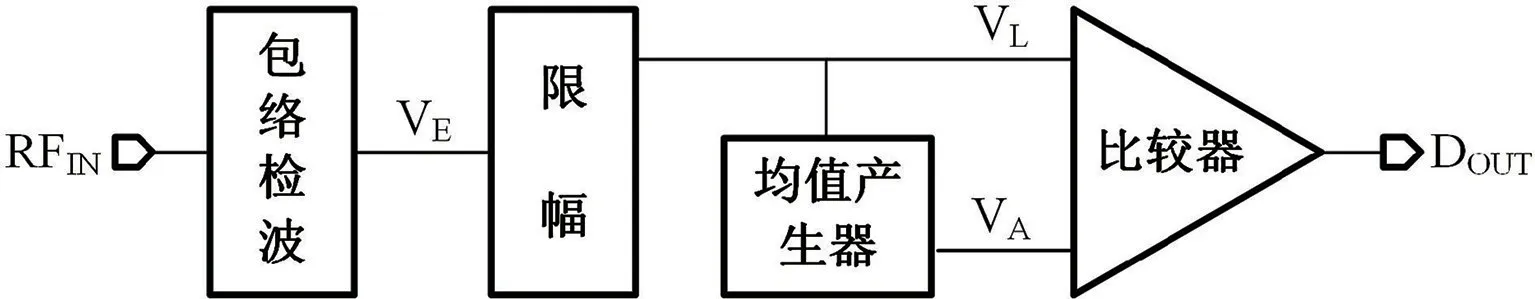

本文设计的UHF RFID 信号解调器原理如图1 所示。经振幅键控(ASK)调制过的射频信号RFIN经天线端接收之后,被送入包络检波电路提取出已调信号的包络VE;限幅电路避免大包络信号造成电路异常;限幅电压VL一路接至迟滞比较器,另一路送至均值产生器以生成比较参考值VA;比较器对VL与VA进行比较以确定出数字信号

图1 UHF RFID 信号解调器原理Fig.1 Principle of UHF RFID signal demodulator

1.1 包络检波电路

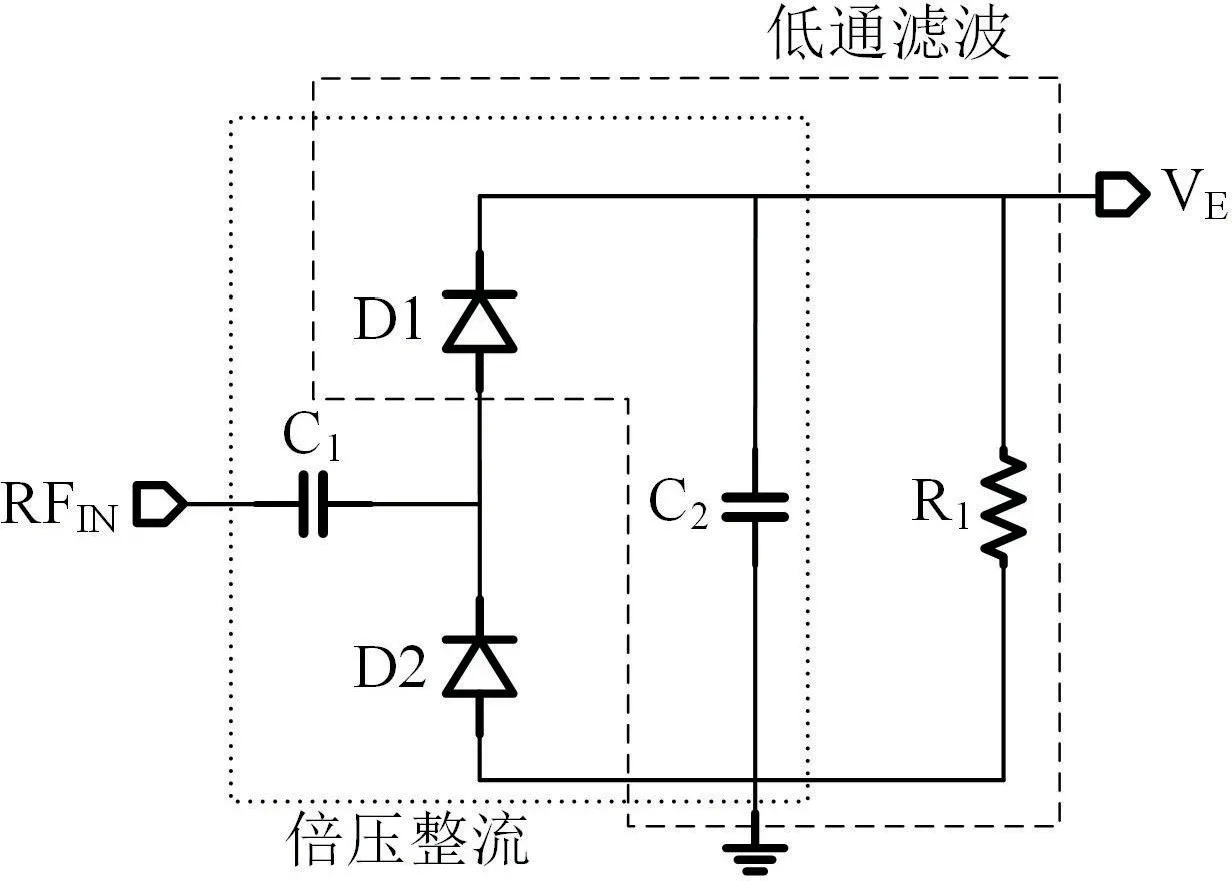

倍压整流加低通滤波电路可提取出ASK 信号的包络,如图2 所示的检波电路不仅结构简单,而且不需要额外提供电源,即不消耗电源功率,适合在无源标签芯片中使用。

图2 倍压整流加低通滤波电路Fig.2 Voltage doubler rectifier plus low-pass filter circuit

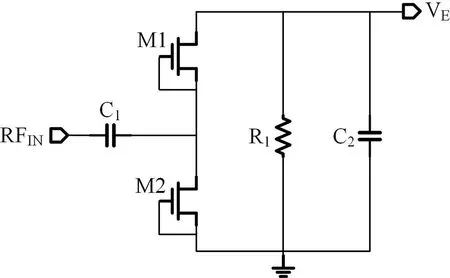

图2 中D1 和D2 一般采用肖特基二极管,由于现有CMOS 工艺实现肖特基二极管较难,将MOS 管的漏源极短接是一种极佳的二极管替换方式,本文采用的改进型包络检波电路如图3 所示[4,9]。

图3 包络检波电路Fig.3 Envelope detection circuit

图3 中,电容C1、C2和MOS 管M1、M2 构成一级倍压整流电路[11]。当输入电压RFIN位于负半周且小于MOS 管的阈值电压VTH,即RFIN<-VTH时,电荷由地经导通的M2 为C1充电,电容电压在RFIN的负峰值-VM处将达到VC1=-VM+VTH;RFIN>-VTH时,M2 截止,同时尚未导通的M1 使得C1上的电荷守恒,VC1维持不变;当RFIN>VTH时,电荷经导通的M1 开始对C2充电,在RFIN达到正峰值VM时,C2的理想电压值为:

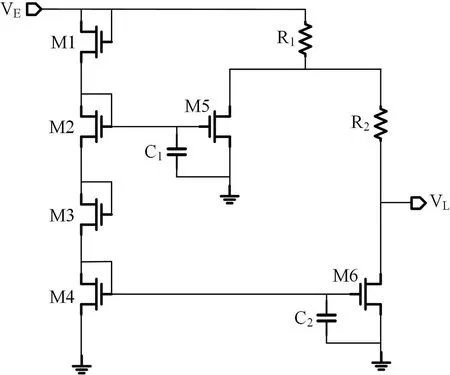

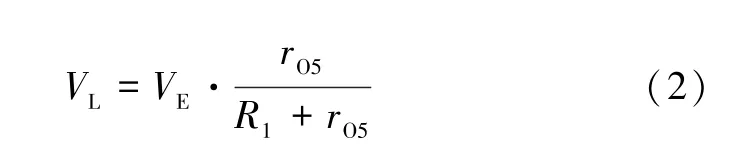

RFIN从正峰值下降至RFIN 图4 给出了包络检波电路的仿真输出VE。由图4可知,无源无功耗的倍压整流加低通滤波结构成功地提取出了射频信号的外包络。 图4 检波电路仿真结果Fig.4 Simulation results of detector 近场时标签接收的能量较大,限幅电路可避免大幅值VE造成后级电路异常。如图5 所示,整个限幅电路没有接入工作电源,无能源消耗。二极管连接的NMOS 管M1~M4 串联组成电压检测通道,电阻R1、R2和NMOS 管M5、M6 形成电荷泄流通路,电容C1和C2分别稳定M5 和M6 的栅电位[10]。 图5 限幅电路Fig.5 Limiter circuit 较低的VE经M1 分压后可使M5 的栅源电压VGS5小于其阈值电压VTH5,从而VGS6必然小于VTH6,M5 和M6 均截止,输出电压VL等于输入电压VE。 当VGS5>VTH5且VGS6 VE上升使VGS6>VTH6后,M5 与M6 均导通,输出为: 图6 给出了限幅电路的仿真结果。在0~1.5 V 输入范围内,输出电压VOUT基本等于输入电压VIN;在1.5~8 V 输入范围内,输出电压VOUT限制在1.8 V。 图6 限幅电路仿真结果Fig.6 Simulation results of limiter 标签接收能量的大小使得VL具有不同的高电平,而信号的多种调制深度导致VL具有不同的低电平,某种情况下的低电平可能会超过另一种情况的高电平。参考电压应根据VL的高低电平动态确定,基于峰值VPEAK和谷值VVALL检测的均值产生器很好地满足了该要求,其电路结构如图7 所示[12]。 图7 均值产生器电路Fig.7 Average generator circuit 运算放大器OPA1 和OPA2 可由深度负反馈环路形成电压跟随器,运算放大器电路结构可参考文献[13-14],本文不再详述。OPA1、PMOS 管M1 和电容C1共同构成包络峰值VPEAK检测通道,而NMOS管M3 可调节通路电流量;OPA2、NMOS 管M2 和电容C2一起组成包络谷值VVALL检测通道;等值电阻R1和R2对峰值和谷值分压,以确定出平均值电压VA,于是有: 假定电容C1、C2和C3在初始时刻均为零电压。输入端VL为高电平时,由反相端电压大于同相端可知OPA1 和OPA2 都输出低电平,M1 导通而M2 截止,VDD经过M1、M3 为C1、C2和C3充电。电压跟随器OPA1 使得C1的电压VPEAK约等于输入电压VL,截止的M2 断开了OPA2 的负反馈环路,C2的电压VVALL不会随VL变化。大阻值的等电阻R1、R2使得C2的充电时常数大,VVALL上升平缓。由KVL 定理可知,此时C3的电压VA符合式(4)。 当VL由高电平转换为低电平后,VPEAK大于VL,运放OPA1 输出高电平使M1 截止,断开的负反馈环使VPEAK不再随VL变化。此时VVALL同样大于VL,OPA2 输出高电平使M2 导通,C1、C2和C3经过M2放电,远大于信号周期的放电时常数使得VPEAK和VA下降较缓,而较小的C2放电时常数使得VVALL快速回归至低电平,且电压跟随器OPA2 使VVALL保持在低电平。同样由R1与R2等值可知VA满足式(4)。 均值产生器的仿真结果如图8 所示。实际生成的均值参考电压VA(实线)位于VL(虚线)高低电平之间,为比较器的正确判别提供了较为理想的参考值。 图8 均值产生器仿真结果Fig.8 Simulation results of average generator 含有纹波的电压输入到普通单门限比较器会在输出端产生来回抖动,迟滞比较器具有抑制幅度在回差ΔV范围内的噪声的能力。 图9 所示的迟滞比较器为两级放大器后接两级反相器结构,比较器的迟滞特性是由M5 和M7 的栅漏极所构成的正反馈路径实现[15]。现将VA接地,时使M1、M2 的栅源电压M2 导通,M1 截止。M2 的导通使M7、M8 导通,而M1 的截止使M5、M6 截止并使M7 处于深度线性区,M9、M2和M8 的漏源电流I9、I2和I8形成关系为:I9=I2=I8。此时M3 截止但M4 导通,比较器输出低电平。 图9 迟滞比较器电路Fig.9 Hysteresis comparator circuit 比例电流源M7-M8 的最终作用是使: 式中:(W/L)7、(W/L)8分别为MOS 管M7、M8 的导电沟道宽长比。 VL由低向高上升将使M1 逐渐脱离截止状态,I1逐步增加到比例值I7时,比较器的输出电平由低向高翻转。因此I1=I7时刻的差分输入为正向转折点,即上门限电压V+,于是: 由I1=I7,I2=I8,I9=I1+I2,并结合式(5)有: 由式(6)~(8)并结合PMOS 管饱和区电流公式可得: 式中:μP为PMOS 管的表面电子迁移率;COX为单位面积栅电容[14]。 同理可推得下门限电压为: 电路偏置电流I9由比例电流源M9 提供。由上述分析可知在M1(M2)的宽长比已定的情况下,改变M5、M6、M7 和M8 的宽长比可调节上下门限电压和迟滞回差大小。图10 给出了比较器迟滞响应的仿真结果,本电路设定的回差ΔV为20 mV。 图10 比较器迟滞响应Fig.10 Hysteresis response of comparator 分别将每个子电路、放大器布置成单独的版图单元可有效减小器件间、模块间相互干扰。各单元外围设置两道保护环:内侧P 型保护环接地,外侧N 型环接电源,内P 外N 环形成PN 结墙体以阻止外界噪声的入侵。各单元内部的电容、电阻、PMOS 管和NMOS 管应分区集中设置。电容区、电阻区和NMOS管区外围设置接地的P 型环以保护环内P 衬底中空穴多子不受到环外电子的注入,且NMOS 区的P 环兼做MOS 管的衬底接触。PMOS 管区外围应设置接电源的N 型环,既保护环内N 阱的电子多子不被环外空穴吸收,又为PMOS 管提供了衬底连接。 比例电流源通过改变各MOS 管宽长比来控制各支路电流大小,为获得准确的比例电流,电流源各MOS管的版图应采用叉指结构,如迟滞比较器的M5-M6、M7-M8、M9-M10 和M11-M12。迟滞比较器的差分输入管M1-M2 和M3-M4 对信号极为敏感,需采用二维共质心阵列形式的交叉耦合对版图结构,此种结构更能满足敏感电路版图的一致性、对称性、分散性、紧凑性和方向性要求[16]。 图11 给出了用于流片的解调电路版图,版图尺寸为1021 μm ×117 μm。 图11 解调电路版图Fig.11 Layout of demodulation circuit 使用Cadence Spectre 对整体电路进行前后仿真。工作电源采用1.8 V,以915 MHz 的正弦波为载波,观察测量输出信号并计算最大偏差。图12 给出了三种不同幅值、调制深度和脉冲频率的ASK 信号仿真结果。 图12 三种ASK 信号仿真结果Fig.12 Simulation results of three ASK signals 这三种ASK 信号的仿真数据如表1 所示。计算得出最大的脉宽解调误差仅为0.43%。 表1 三种ASK 信号仿真数据Tab.1 Simulation data of three ASK signals ISO/IEC 18000-6C 和GB/T 29768-2013 协议分别使用PIE 和TPP 对基带数据进行编码,两种编码都可以转换成非归零(NRZ)码。任意给定三组8 位NRZ码基带数据,用不同深度去调制载波以生成ASK 信号,以此对电路施加激励,图13 给出了解调器的输出响应。 图13 中的仿真数据如表2 所示。由表2 可知电路准确完整地解调出基带信号。 表2 8 位随机NRZ 码仿真数据Tab.2 Simulation data of 8-bit random NRZ 图13 8 位随机NRZ 码仿真结果Fig.13 Simulation results of 8-bit random NRZ code 基于良好的动态性能和极低的解调误差,本文设计的解调电路应用在了已流片的一款超低功耗标签芯片中,图14 所示的显微照片中标示出了解调模块在芯片中的位置。图15 为搭建的芯片测试环境,图16 给出了无源检波限幅电路的测试输出,结果表明电路运行正常、性能良好。 图14 芯片显微照片Fig.14 Micrographs of chips 图15 芯片测试环境Fig.15 Test environment of chip 图16 限幅电路测试输出Fig.16 Test output of limiting circuit 本文设计了一种适应多种调制深度和速率且幅值大幅变化的ASK 射频信号解调器,已应用于无源标签芯片中并成功流片。采用的倍压和低通技术以简单结构实现了无源检波限幅,采用的均值检测技术和正反馈技术有效提高了解调准确度。电路采用TSMC 0.18 μm 标准CMOS 工艺实现,仿真显示最大的脉宽解调误差仅为0.43%,对ISO/IEC 18000-6C 和GB/T 29768-2013 协议的PIE 和TPP 编码都能准确完整地处理。

1.2 限幅电路

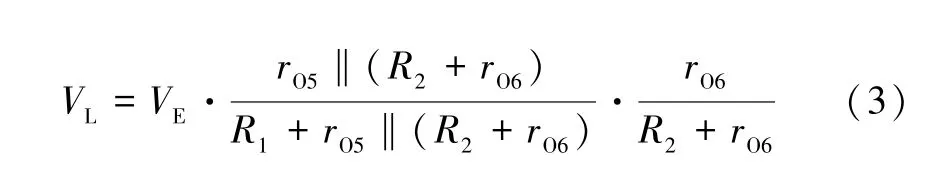

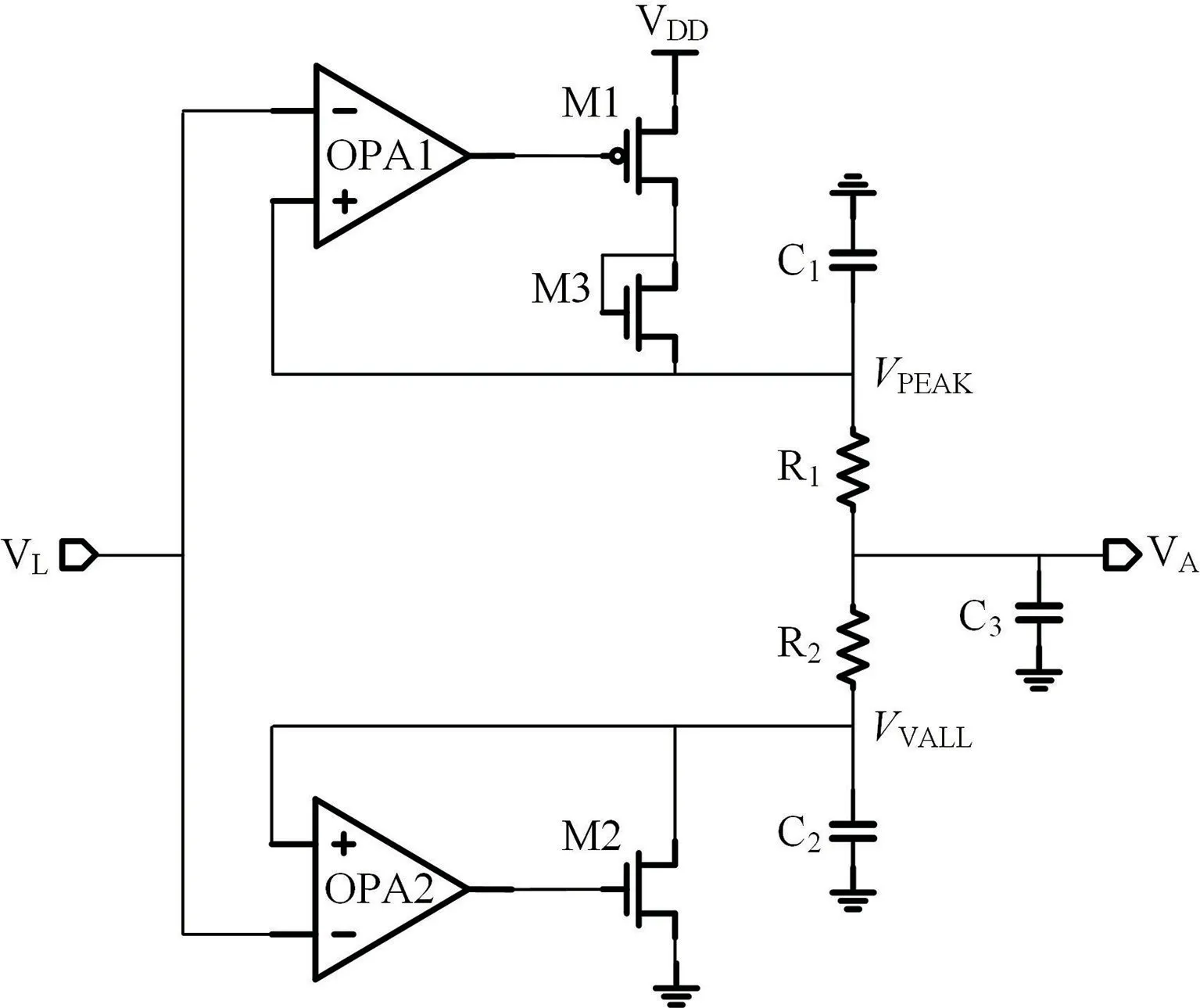

1.3 均值产生器

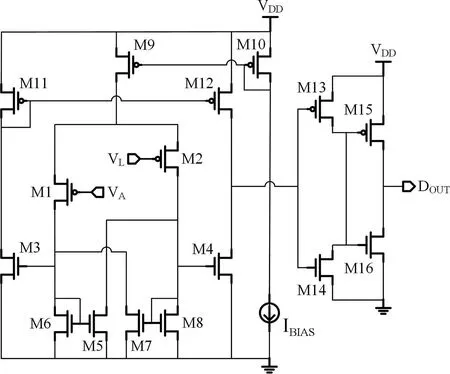

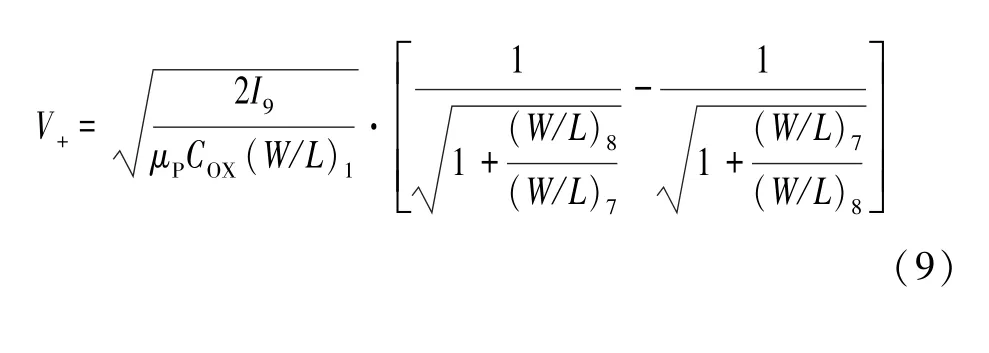

1.4 迟滞比较器

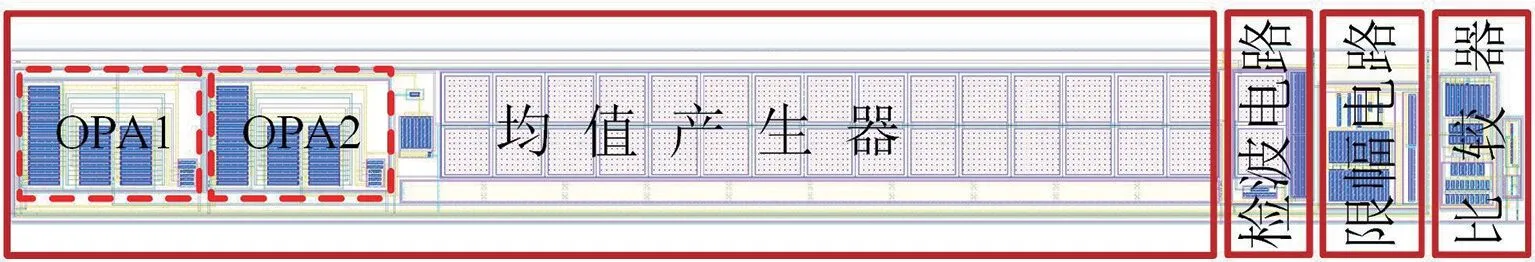

2 版图绘制

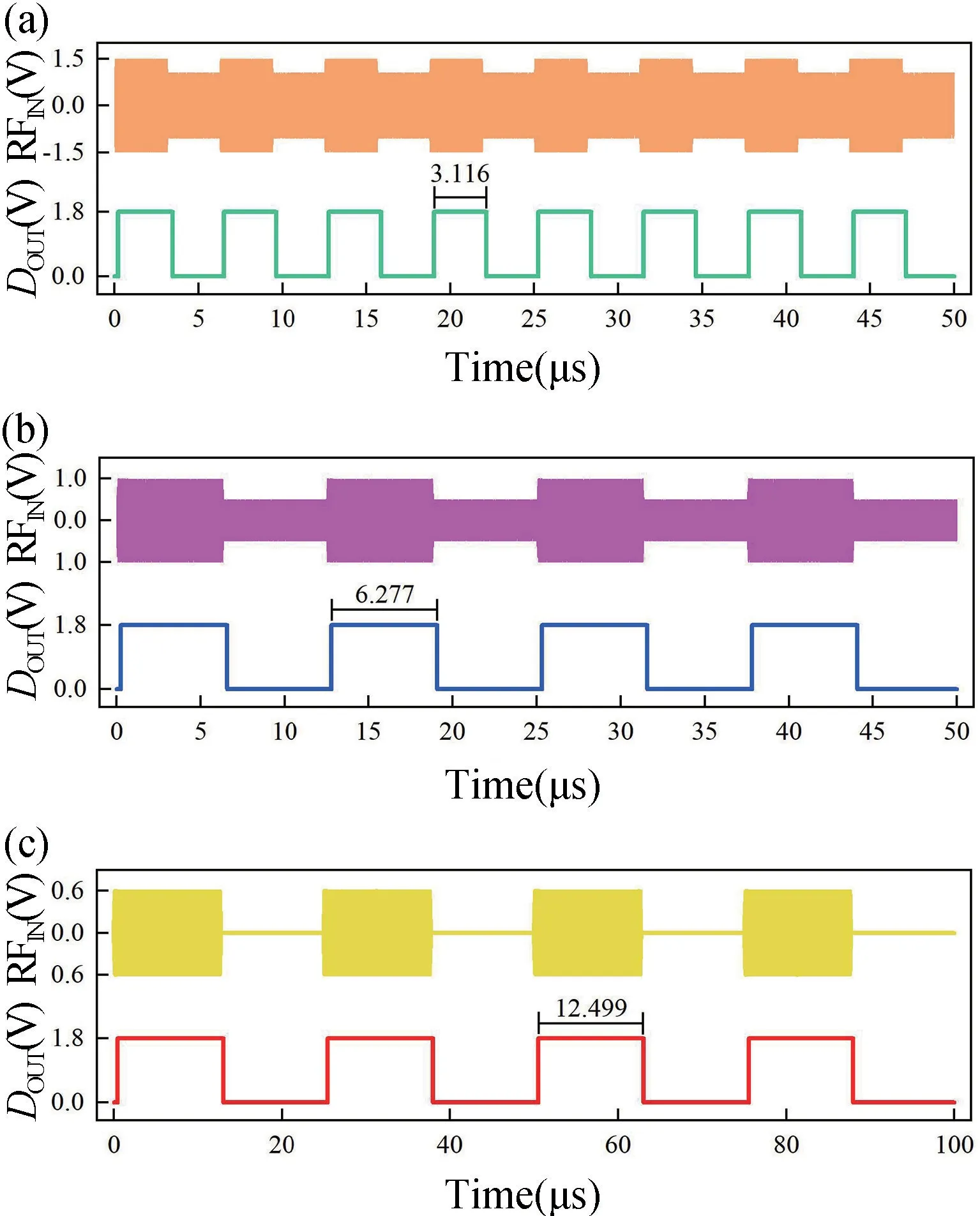

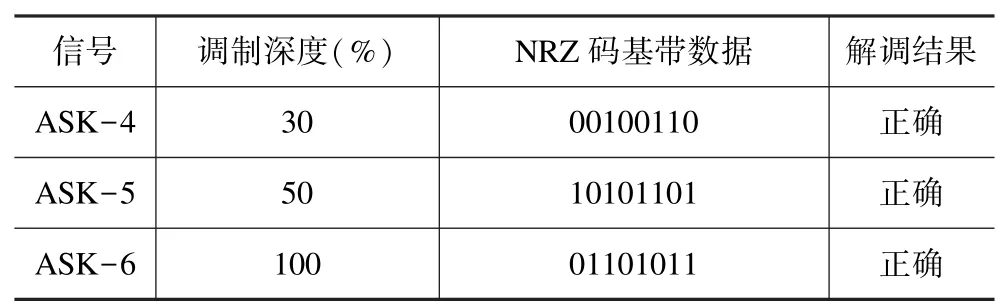

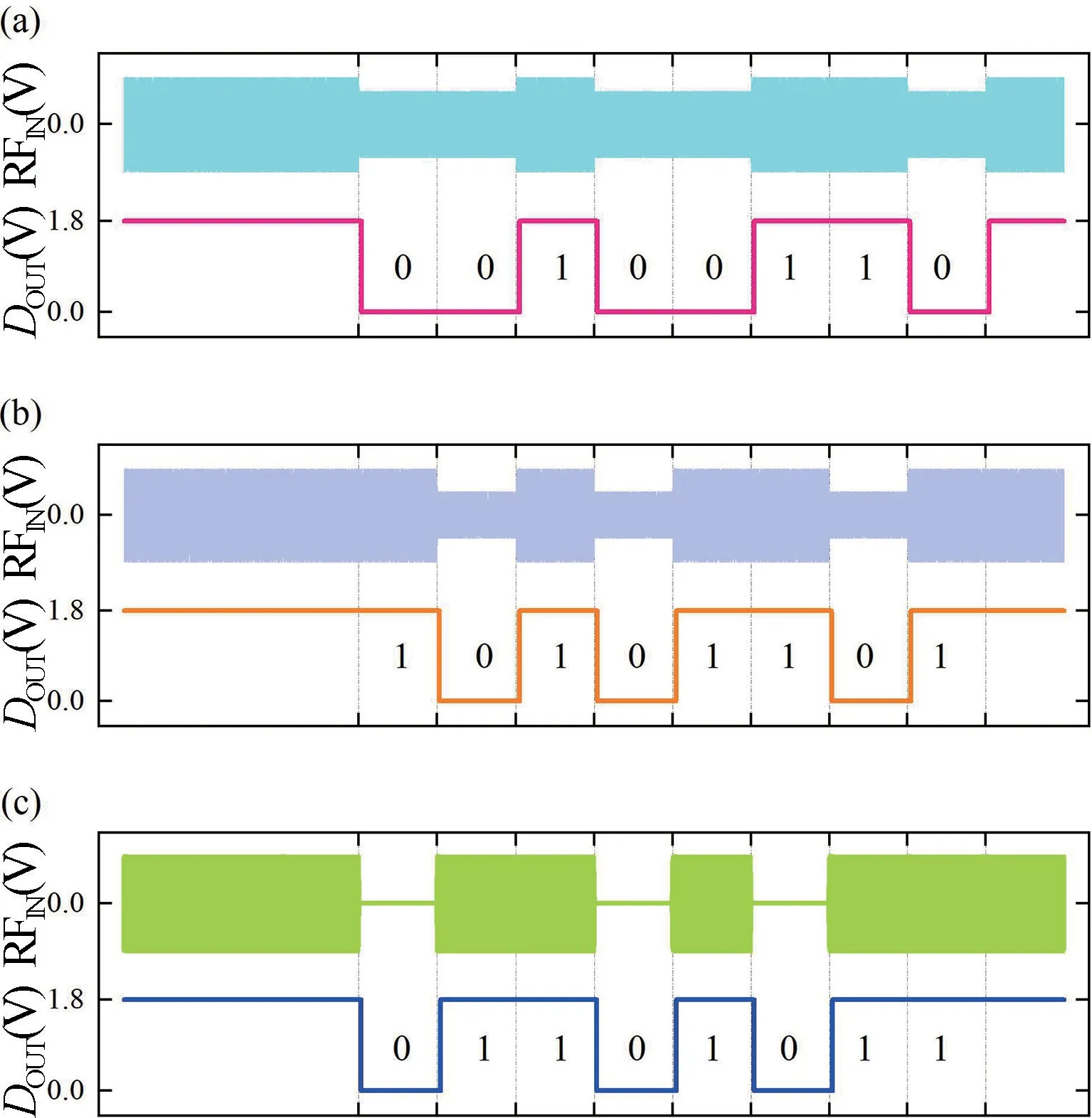

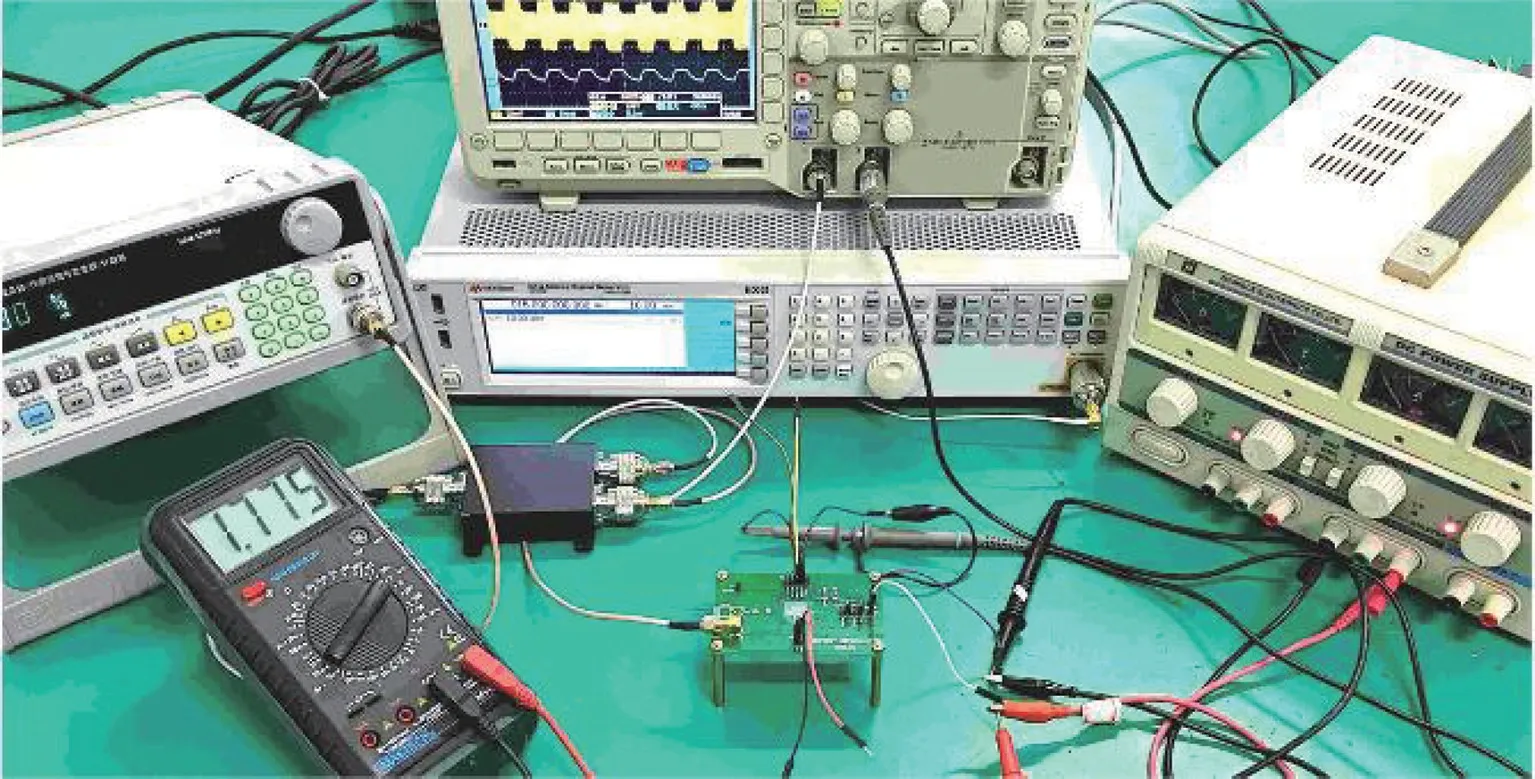

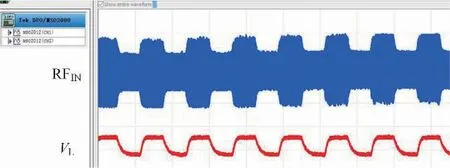

3 电路系统仿真和芯片测试

4 结论