DDR3堆叠键合组件的信号完整性优化研究

赵勇

摘要:现代多种行业的发展和运行过程,对于芯片质量的要求越来越高,因此需要通过对各类芯片运行中相关信号的完整性充分研究,从中找到相关系统的设计问题并对其优化。本文分析了DDR3堆叠键合组件的具体设计方案,之后分析了在实际的运行中相关信号的完整性,并提出了针对性和完整性的优化方法,此外在实际的工作阶段,主要是分析针对DDR3堆叠键合组件的封装与基板设计工作、仿真和优化方法参数,之后通过对具体运行效果图的跟进,实现对相关参数的使用,并研究取得的测试模拟分析优化成果是否达到标准。在专项分析中,优化的参数为各个通道中的延时参数和阻抗参数,采用拓扑模型进行优化操作。

关键词:DDR3堆叠键合组件;信号完整性;信号分析

引言:DDR3堆叠键合组件的设计过程,需要通过封装和设计工作,建立该组件的连接线,采取拓扑结构对控制器以及其他的走线做出合适的调节以设置主干通道,并在其中设置分支通道,实现对通道走线的合理协调。

一、DDR3堆叠键合组件的处理方案

(一)封装与基板设计工作

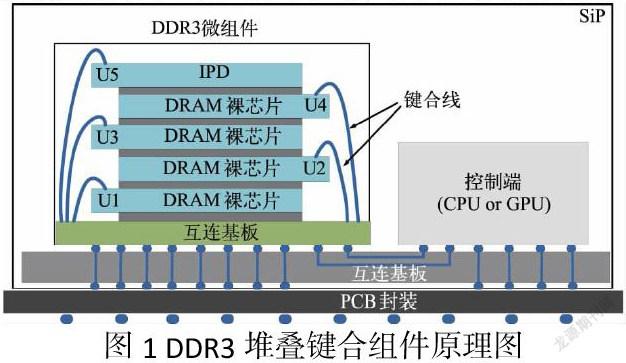

DDR3堆叠键合组件为5层堆叠结构,整体结构如下图所示:

其中有四颗DDR3芯片,每个芯片容量为8Gb,运行速率为1.6Gbps,采用16位数据模式,则该组价为64位,数据结构容量为4GB,带宽为12.8GBps,形成了点对点的互联通道结构,之后根据该设计结构,采用Fly-by拓扑结构,将控制器和第一个DRAM颗粒连接走线,并且该走线为主干通道,DRAM颗粒之间的走线为分支通道,通道到DRAM的走线为键合线。

(二)仿真和优化内容

仿真处理过程,由于整个系统中的16个地址信号和其中的5个控制信号采用同种设计方法,因此取得的实际仿真结果也基本相似,在具体仿真处理过程,只需选择其中一个地址信号处理即可,并且根据该系统的等效电路图对整体的设计模型进行搭建,完成参数的扫描以及计划结果分析工作[1]。

二、DDR3堆叠键合组件的信号完整性优化方法

(一)电路搭建工作

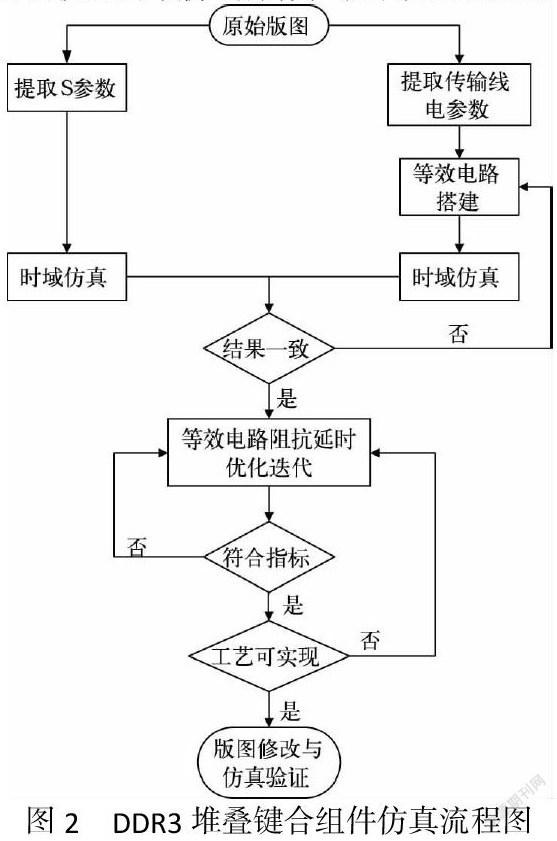

電路搭建过程,采用仿真软件得到DDR3堆叠键合组件,提取其中的器件阻抗、延时参数等,并对各类参数进行处理。同时在模型的搭建中,也要采用仿真拓扑模型,实现对于输入的激励信号、互联模型、IBIS模型以及重要的匹配电路综合协调,最终建立了互联模型和等效电路模型,之后对这两类突破后的模型时域仿真操作,该系统的处理流程图如下:

具体的处理中,也需要根据设计的信号波形图,对输入的信息以及输出的信息跟进了解。对于原始版图的信号,通常包括实际取得参数的处理,根据其他的数值可以分析各个芯片之类的参数,从而对该互连结构进行优化处理。对于等效电路模型需要确保准确度,对该等效电路模型变量的参数扫描以及最佳参数的取值处理工作,该处理过程主要设置两个变量,一个是对于主干通道和分支通道的阻抗参数,另一个是主干通道和分支通道的延时参数。此外需要全面保证在所有的各类信息在专业处理过程中,需要全面根据已经建立的模型,实现对于所有信号参数的进一步优化,该过程中需要完全根据已经得到的所有信息进行研究,从而使得最终所得到的所有参数进行协调。

(二)参数取得工作

在相关参数的取得中可以发现,对于各类变量的初始设置值,主干通道阻抗参数和延时参数分别为41.56Ω与0.023ns,分支通道阻抗和延时参数分别为31.47Ω与0.055ns,上拉电阻为50Ω。之后得到阻抗和延时的关系曲线,可以发现,首先其他的各类变量为初始值时,在阻抗范围为10~100Ω,步长为10Ω时,对于眼高的影响相对较小,并且进一步研究发现最佳的参数为30Ω,而保持该阻抗为30Ω,分支通道的阻抗、延时处于初始状态,延时调整为0.01~0.1ns,步长为0.01ns时,可以确定最佳的延时参数为0.02ns。在保持主干通道的延时和阻抗相同的情况下,需要分析分支通道的阻抗和延时参数,其中发现阻抗参数为60Ω,延时参数为0.02ns时处于最佳运行状态。

(三)优化分析工作

进一步的分析发现,对于通道的阻抗方面造成的影响为,由于DDR3堆叠键合组件采用Fly-by比拓扑结构,如果将通道DRAM作为桩线,那么在桩线的处理中,每一段中线都可以看做容性负载,怎么每一过孔都存在一个寄生电容,同时在每个桩线上都含有DRAM颗粒,那么该颗粒会存在封装寄生电容和片内等效电容,出现容性负载效应,因此需要采取适当的措施减小容性负载所带来的反射。此外在进一步的优化分析工作中,还需要对各类优化信息和参数的研究工作,实现对于所有参数的协调与专业性研究,要求必须根据现有的拓扑方案进行全面性地研究,唯有如此方可让最终所得到的所有处理结果处于更好的运行状态。

(四)版图修改工作

版图的修改需要根据已经建立的等效参数对相关的操作进行扫描处理,之后考虑每个芯片的处理质量和实际的运行参数,之后对基础版图中的各个叠层结构以及布线和线宽参数,完成进一步的参数调整工作[2]。通过进一步的模拟分析工作可以发现,优化之后的结果相对于那优化之前的结果,在稳定性以及其他的影响参数上更加可靠,优化结果为主干通道的阻抗和延时为30.464Ω与0.180ns,分支通道为59.8424Ω与0.0597ns,上拉电阻为40Ω。

结论:

综上所述,DDR3堆叠键合组价的信号处理中,需要对各主干通道和分支通道进行调整,并采用专业的模拟分析技术对相关参数进一步的验证,主要需要详细分析阻抗参数和延时参数。

参考文献:

[1]施赛烽,叶润川,林雪,等.基于FPGA和DDR3 SDRAM的高精度脉冲发生器设计与实现[J].合肥工业大学学报(自然科学版),2021,44(02):206-209+283.

[2]曾燕萍,张景辉,王梦雅,等.DDR3堆叠键合组件的信号完整性分析与优化[J].电子与封装,2020,20(12):7-11.

南京中兴软件有限责任公司