多通道定时脉冲光纤传输系统国产化设计

姚君 聂杨 付传宝

摘要:本文介绍了一种基于100%国产化设计的定时脉冲信号传输系统,系统近端机将16路定时脉冲信号同步采样,然后复用成1路高速数字信号,通过一根光纤传输到远端机,远端机可以实现多路数据的低抖动输出,并保持延时一致性。该系统以光纤作为传输介质,传输距离远,抗干扰能力强,可广泛用于不同体制雷达系统,实现多路定时脉冲信号远传。

关键词:国产化;光纤传输;低抖动;延时一致性

1引言

雷达系统的基本构成包括发射机、接收机、本振激励源、信号处理、定时同步装置这五部分[1],其中定时同步装置主要负责产生定时脉冲信号,完成雷达系统时序控制,协调各分机正常工作,在整个系统中发挥着重要作用。由于雷达系统信号接收天线与控制设备一般都分开布设,中间通过光纤/电缆连接,因此系统发射机、接收机、定时同步装置通常处于不同的地点,需要使用专用设备对定时脉冲进行传输。

目前许多传输设备的关键器件及设计软件都是来自于国外进口,容易受制于人,通过近期美国对中国科技公司的多轮制裁事件可以得知,一旦西方国家实施技术封锁,将会对设备研发、生产及维护造成严重的影响。为提高自主可控能力,杜绝对国外核心器件及软件的依赖所导致的信息安全隐患,本文提出一种软硬件国产化率达到100%的传输系统设计方法,采用光纤作为传输介质,定时脉冲信号经过采样后,可以通过光缆远距离传输至雷达发射机、接收机,经过传输后的信号其关键指标信号前沿抖动≤1ns,延时一致性≤5ns,满足雷达系统使用要求,同时具有保密性能好、可靠性高等特点。

2系统方案

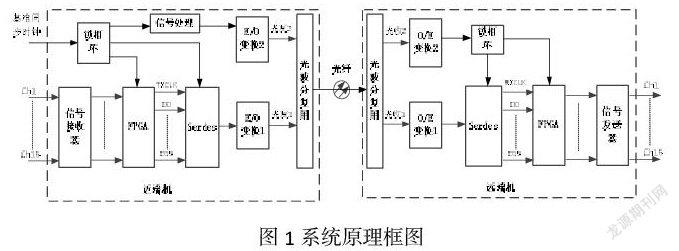

多通道定时脉冲光纤传输系统采用远端机和近端机模式,远端机放置于天线转台,用于光电变换和信号低抖动输出;近端机放置于控制舱内,负责对16路定时脉冲信号进行采样和电光变换,端机之间用一根光纤进行连接。

传统模式下,可以通过FPGA对定时脉冲信号进行异步采样后直接上光,传输到对端后恢复出脉冲信号,由于数字信号的离散特性,采样点最少偏离最佳采样点一个周期,采样位置左右偏移[2],因此利用该方案恢复出来的信号前沿抖动为2T(T为采样时钟周期),以采样时钟100MHz为例,经过采样后引入的抖动为20ns(T=1/100MHz=10ns)左右,若想达到1ns以内的前沿抖动,系统所需采样时钟频率需要达到2GMHz,将远超过FPGA的工作时钟,大大提高了设计难度;同时使用FPGA进行信号复用/解复用、编码/解码,开关机后信号延时会发生较大变化,无法保证信号的延时一致性。本方案采用同步传输的方式,将雷达系统提供的基准时钟锁定相位后作为传输系统工作时钟,对信号同步采样,可获得低抖动值,在复用/解复用部分使用外置高速Serdes(串行收发器),可减小通道延时的变化。

3硬件设计

3.1系统原理

系统原理框图如图1所示。在近端机,基准同步时钟输入到PLL(锁相环)锁定相位后得到稳定的时钟信号,将该时钟信号分为三路,第一路输入到FPGA对输入的脉冲信号进行处理,第二路作为Serdes的工作时钟,第三路经信号处理后转换为光信号2输出;输入的16路定时脉冲信号经数据整形、电平转换后变为LVTTL电平的电信号,进入到FPGA中,FPGA用同步时钟进行同步时分处理,然后传输给Serdes,Serdes利用同步时钟来进行时分复用和8B/10B编码,经电光变换变成光信号1,光信号1和光信号2通过波分复用器复用成1路光信号传输到远端机。在远端机,收到的光信号2经过光电处理后,转换为时钟信号,该时钟信号经锁相环锁定后一路输入到FPGA用于信号处理,另一路作为Serdes的参考信号;收到的光信号1经过光电转换后变成1路高速的数字信号,然后通过CDR时钟恢复提取,进入到高速Serdes,经8B/10B解码和时分解复用,变为多路低速数据信号输入到FPGA中,FPGA对各低速信号进行处理后将数据输出,经过电平转换及驱动后恢复为初始状态的16路定时脉冲信号。

3.2国产化实现

系统包含信号接收器、FPGA芯片、PLL芯片、高速Serdes、E/O变换器、O/E变换器、信号发送器等主要器件,信号接收器和信号发送器采用的是SM3096和SM3030,接收器传输时延≤120ns,发送器传输时延≤16ns,最大数据传输率均为10Mbps;FPGA采用的是FMK50T4,最大时钟频率为400MHz;PLL芯片采用的是GM307A,最大工作频率为200MHz;E/O变换和O/E变换采用的是NTR-8812DL和NTR-8813LI,发送光功率-5~0dBm,接收灵敏度≤-16dBm,最大传输速率3Gbps;高速Serdes采用的是GM8312,工作频率125MHz~156.25MHz,主要實现3.125Gbps高速串行总线数据与16位并行数据之间高速转换。上述型号器件为国内器件厂家所设计,拥有完全知识产权,其余电阻、电容、电感等器件均有国产厂家供货,整个设备硬件的使用实现了全国产化。

4主要实现技术

4.1时钟低抖动传输

信号传输过程中采用了同步采样,理论上不存在采样误差,因而定时脉冲信号的边沿相位和抖动得到了合理的控制,信号抖动性主要由同步时钟的抖动性能决定。由于近端机和远端机都使用了同步时钟,在保证近端机输入基准时钟高质量的同时,需要用低抖动的方式将时钟从近端机传输至远端机,为此在时钟传输的过程中采用了两项措施:(1)选用抖动量小的光模块[3]。所有光发射模块单元包括激光器、参考时钟源、以及与发送器有关的集成电路都会产生抖动,通过选用低抖动器件,降低发送器各部分器件的噪声,可以有效地减少抖动以获得一个干净的眼图;(2)针对接收部分采用暗电流小、电容低、响应度高的PIN光电探测器作为实现光电变换功能的器件,并通过对PIN光电探测器的S参数进行测试,根据S参数的测试结果对阻抗匹配电路进行设计,将高阻抗的PIN光电探测器匹配为50Ω,从而使PIN光电探测器得到高的光电转换效率,低的反射损耗,使时钟信号从光信号中高效的解调出来,并减少时钟的失真,改善时钟的噪声。

4.2外置高速Serdes

FPGA内部自带高速收发器UHST,最高速率为6.25Gb/s,使用同步时钟作为参考时钟,通过调用IP核能实现数据复用/解复用、编解码等功能,用该方法传输后的信号抖动能满足≤1ns,但系统在每次开关机时,脉冲信号的延时差会变化超过一个采样周期(如采用频率100MHz,延时变化将≥10ns),不满足通道延时变化≤5ns。为此我们选择外置高速Serdes,GM8312能够实现16:1串化及1:16解串数据全双工收发,内建DC平衡8B/10B编解码,能保证每次上电时信号的延时偏差≤2ns。输入的并行数据与参考时钟为同步关系,选择用上升沿采样,如图2所示,建立时间:Tsu≥2.5ns,保持时间:Th≥0ns,在数据的稳定时间进行采样,确保数据可靠性。

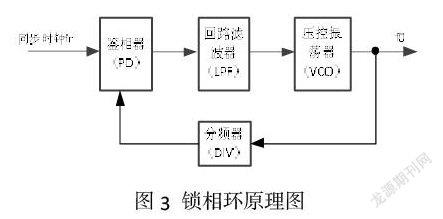

4.3外置PLL

高速Serdes的工作时钟TXCLK需要与输入同步时钟同源,同时TXCLK要求满足低延时,低抖动的特点,以降低数据转换过程中的误码,为此使用PLL将同步时钟锁相倍频到Serdes的工作频率。由于FPGA自身例化PLL所生成时钟毛刺较多,且抖动较大,会影响GM8312的正常使用,因此,使用外置PLL对输入时钟进行管理和频率综合。系统选用的锁相环芯片,最大输出抖动±150ps,锁相环的原理框图如图3所示[4],VCO输出的频率f0经N分频后与同步时钟fr相位比较得到误差电压,回路滤波LPF滤除误差电压中所带来的高频成分和噪声,达到改善性能的目的,鉴相器通过误差电压控制VCO的输出f0,实现对输入频率的捕获、跟踪与测量。

5系统时序

为保证定时脉冲信号传输满足前沿抖动≤1ns的技术要求,定时脉冲信号必须和同步时钟保持严格同步,如图4所示,脉冲信号在发送端经过同步时钟读取后,由同步时钟进行复用。接收端Serdes输出的信号每次开关机时延会有一定的偏差,偏差值≤2ns,小于采样时钟周期,经过同步时钟读取一遍后,可消除延时偏差,最后输出的脉冲信号上升沿的抖动取决于同步时钟的稳定性,而同步时钟传输抖动≤300ps,利用这个时钟去读取串行收发器输出的定时脉冲,其上升沿抖动能满足1ns的技术指标要求。

6软件设计

该系统包含FPGA方面的软件设计,采用自主研发设计的软件开发工具Procise,基于Verilog编译语言,可以完成逻辑优化、布局布线、时序分析、在线调试等功能。

软件工程主要包括数据模块,复用驱动模块,锁定判断模块,解复用驱动模块。数据模块完成定时脉冲的时序调整、输出驱动;锁定判断模块控制系统复位信号以及输出静噪;复用、解复用驱动模块在整个软件中起关键作用,主要完成对高速Serdes的管理,其逻辑代码例化调用配置如下:

tx tx_u( .rstn(rstn),

.clk(clk),

.tx_serdes(tx_serdes),

.txclk_serdes(txclk_serdes_o),

.tx_en_serdes(tx_en_serdes),

.tx_er_serdes(tx_er_serdes),

.lckrefn_serdes(lckrefn_serdes),

.prbsen_serdes(prbsen_serdes),

.enable_serdes(enable_serdes)

);

rx rx_u( .rstn(rstn),

.clk(clk),

.rxclk_serdes(rxclk_serdes),

.rx_serdes(rx_serdes),

.rx_er_serdes(rx_er_serdes),

.rx_dv_serdes(rx_dv_serdes),

.rxclk(rxclk),

.rxdata(rxdata)

);

7测试及性能分析

通过信号源产生20MHz的同步时钟,同时产生脉宽900ns,重复频率1000Hz定时脉冲信号,近端机与远端机之间用长度为1m光纤连接,将脉冲信号输入到近端机的传输通道1,经过采样传输后从远端机输出。用示波器的通道1测量信号源输出的脉冲信号,并将该通道设置为触发源,用通道2测量远端机输出的该路信号,如图5所示,选择示波器的无限余辉功能,并保持30s,可以测得抖动值≤600ps,传输延时183ns,开关机延时差≤5ns,按同样的方法可以测得其余15通道的传输抖动及延时。测试结果表明系统满足信号前沿抖动≤1ns,延时一致性≤5ns的要求。

8结束语

本设计全国产化实现,外置锁相环,外置高速串行收发器,完成了对16通道定时脉冲信号的同步采样,通過光纤传输到远端,实际测试可知传输后信号抖动低,通道的延时变化小,该方案能够满足多种雷达系统中对定时脉冲信号传输的要求。

参考文献

[1]丁鹭飞,耿福录,陈建春.雷达原理[M].北京:电子工业出版社,2014.

[2]朱海江,王洪磊,陈雁.一种定时脉冲低抖动传输方案设计[J].无线电通信技术,2014(2):44-46.

[3]张家会.脉冲信号同步及低抖动光传输技术[J].大众科技,2017,19(209):7-8.

[4]陈永东. 基于FPGA的数字锁相环的设计[J]. 遥测遥控,2007,28[5]:49-51.

作者简介:

姓名:姚君 性别:男 年龄:35岁 出生年月:1986.1 籍贯:湖南邵阳 职称:工程师 学历:大学本科 研究方向:主要从事光纤通信技术研究