AES-CCM通用协处理器的优化设计实现*

崔 超,赵 云,肖 勇,林伟斌,曾勇刚

南方电网科学研究院有限责任公司,广州 510663

1 引言

AES-CCM(advanced encryption standard-cipher block chaining and counter mode)加密协议作为无线局域网安全标准,由IEEE无线标准小组于2004年公布[1],同时具备验证无线通信中链路层数据完整性、真实性和保障数据安全性的功能,目前已广泛被802.11、802.15、802.16、Bluetooth、Zigbee等无线通讯协议采用.

基于AES-CCM加密协议在智能家居、可穿戴设备、智能驾驶等无线终端设备的广泛应用需求,AESCCM加密协议的实现方式逐渐成为研究热点.目前在工业领域,AES-CCM加密协议普遍采用CCM分组模式软件实现、AES加密核硬件实现的方式,该方式实现简单灵活,但是运算时产生的取指令、指令译码等操作占用本来就有限的CPU内存资源,从而影响数据处理速度和系统功耗.在研究领域Nguyen等人将CBC(cipher block chaining mode)和CTR(counter mode)并行计算,提出了双AES加密核的硬件高吞吐率实现方式,在269 MHz的最高频率下,吞吐率能达到2.69 Gbps[2];Pammu等人提出9-core并行方案[3],在数据加密时多路并行计算,在校验值生成时,利用有限域GF(28)上的乘法将每16×128比特转换为128比特再送进CBC模块计算校验值,将数据处理速率提高至8.32 Gbps.以上研究大多是为了提高了数据吞吐率,而在实际应用中如BLE产品、Zigbee产品等,有时候不需要太高的数据吞吐率,更关注产品的面积和功耗指标.因此,有必要对AES-CCM加密协议的低代价实现进行研究.

本文给出AES-CCM通用协处理器的低功耗实现方案,该方案将传统方法中粗粒度的双AES并行或双AES串行实现[4,5]细化为共享轮密钥的双轮并行或双轮乒乓方式,如此能够在保证吞吐率一致的前提下,减少冗余电路的实现和计算,从而降低面积和功耗的开销.

本文结构如下:第2节介绍了AES-CCM加密协议;第3节对AES-CCM通用协处理器的CCM控制模块以及AES加密模块的双轮并行和双轮乒乓实现方案进行阐述;第4节介绍仿真综合结果;第5节对方案进行总结.

2 AES-CCM加密协议

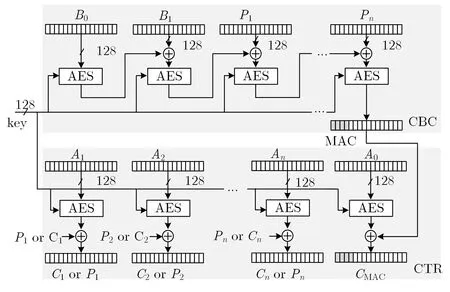

AES-CCM协议的核心加密模块主要由AES算法构成,外围控制模块由经典的密文块连接CBC分组模式和计数器CTR分组模式构成,其结构如图1所示.

图1 AES-CCM结构图Figure 1 Structure diagram of AES-CCM

CBC分组模式主要用于压缩数据生成消息完整性校验值(message authentication code,MAC),数据发送前,发送方对明文数据压缩,生成消息验证码MAC值附于明文后,发送给接收方.接收方收到数据后用同样的CBC分组模式压缩明文得到另一个MAC值,并将两个MAC值比较,若一致,则接收数据无误,以此来验证数据的完整性和真实性.CBC分组模式中AES的输入为包含数据包头、数据长度、数据明文等信息的特定分组与前一组AES密文输出Y i−1的异或值.其计算过程如下,其中B0、B1为包含数据包头和数据长度的128比特数据,P i为128比特的明文分组.

Y0=Enkey(B0)

Y1=Enkey(Y0⊕B1)

Y2=Enkey(Y1⊕P1)

...

Y n+2=Enkey(Y n+1⊕P n+1)

MAC=MSB(Y n+2)

CTR分组模式主要用于对传输数据加解密.发送方将明文数据和MAC值拼接起来并分成等长度的数据组,每组与计数器加密结果进行异或操作得到该组密文,接收方接到密文数据后用同样的方法将密文分组分别与计数器的加密结果异或得到明文分组以及传输的MAC值.该分组模式的加密流程和解密流程完全一样.AES的输入为包含数据组计数值信息的数据A i,AES的密钥key同生成校验值使用的密钥key相同,其计算过程如下:

C1=Enkey(A1)⊕P1orP1=Enkey(A1)⊕C1

C2=Enkey(A2)⊕P2orP2=Enkey(A2)⊕C2

...

C n=Enkey(A n)⊕P norP n=Enkey(A n)⊕C n

CMAC=MSB(Enkey(A n))⊕MAC)

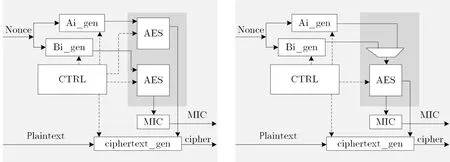

传统的AES-CCM加密协议的全硬件实现技术有两种:两个AES加密核并行实现方案和一个AES加密核串行实现方案,分别如图2中左右所示.AES-CCM加密协议并行实行实现方案采用两个AES加密核并行分别实现CBC分组模式和CTR分组模式.CTR、CBC加密模式中被加密的明文互不相同,都由几块数据组成,所以需要Ai_gen和Bi_gen模块按不同的阶段产生CTR所需的A i和CBC所需的B i,分别输入到两个AES加密核中.

图2 传统AES并行实现AES-CCM方案(左)传统AES串行实现AES-CCM方案(右)Figure 2 Traditional parallel implementation(left)and traditional serial implementation of AES-CCM(right)

AES-CCM加密协议串行实现方案采用一个AES加密核串行实现,以时分复用的方式分别完成CBC和CTR分组模式的计算.A i和B i在CTRL模块的控制下,交替输入到AES加密核中.

3 AES-CCM通用协处理器的优化设计

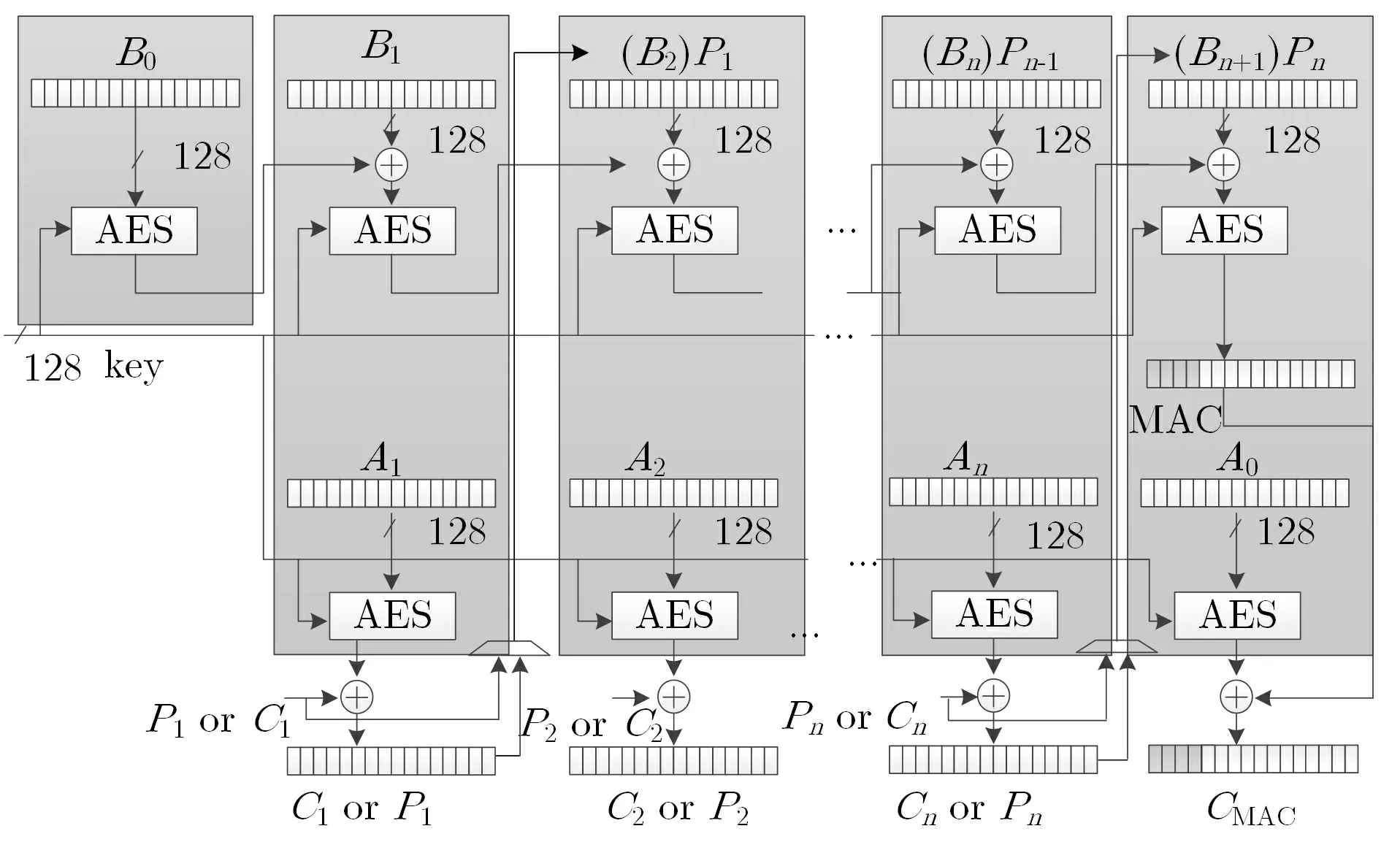

对AES-CCM加密协议进行分析,如图3所示,当设备作为数据发送方时:

图3 AES-CCM数据处理结构图Figure 3 AES-CCM data processing structure diagram

(1)CBC模式比CTR模式多计算一组数据B0;

(2)B1⊕Y0与A1的数据加密可以同步执行;

(3)当获取到128比特明文数据P1且AES加密完成后,P1可以与A1的加密结果异或得到密文C1,继而P1⊕Y1和A2数据加密可以同步执行;

(4)当获取到明文P2且AES加密完成后,P2可以与A2的加密结果异或得到密文C2,继而P2⊕Y2和A3数据加密仍然可以同步执行;(

5)以此类推,直到处理完所有明文数据.

因此除了B0的AES加密运算可以单独执行外,其他所有数据分组CBC和CTR的AES加密运算都可以同步执行.

当设备作为数据接收方时,

(1)同样CBC模式比CTR模式多计算一组数据B0;

(2)B1⊕Y0与A1的数据加密可以同步执行;

(3)当接收到128比特密文数据C1且AES加密完成后,C1可以与A1的加密结果异或得到明文P1,继而P1⊕Y1和A2数据加密可以同步执行;

(4)当接收到密文C2且AES加密完成后,C2可以与A2的加密结果异或得到明文P2,继而P2⊕Y2

和A3数据加密仍然可以同步执行;

(5)以此类推,直到处理完所有密文数据.

因此除了B0的AES加密运算可以单独执行外,其他所有数据分组CBC和CTR的AES加密运算也都可以同步执行.

由以上分析,归纳出AES-CCM加密协议的3个特点如下:

(1)无论设备作为数据的发送方或者数据的接收方,AES-CCM加密协议中仅用到AES的加密模式,因此硬件实现中为减小设备的功耗和面积可以省去AES解密模式的实现.

(2)AES-CCM加密协议中除了CBC模式第一组数据,其他分组CBC模式和CTR模式的AES加密运算可以同步执行.

(3)AES在CBC模式和CTR模式中所用到的密钥相同,因此为减小功耗,两个同步执行的AES计算可以在共享一个密钥扩展模块的方式下以两个轮函数并行实现的方式计算,或以一个轮函数乒乓处理CBC模式和CTR模式数据的方式计算,3.2节与3.3节将给出并行实现和乒乓处理方式的具体过程.

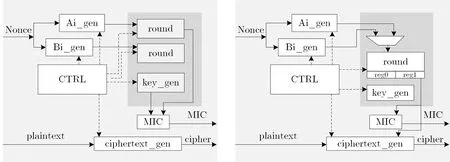

根据以上AES-CCM加密协议的特点,我们设计实现了AES-CCM通用协处理器,外围控制模块与传统双AES并行和单AES串行实现方案一致,AES加密模块根据具体的应用场景可以选择性实现.在高吞吐率要求的应用场景选择AES加密模块双轮并行实现,在低电路面积要求的应用场景选择AES加密模块双轮乒乓实现,其电路结构如图4所示.

图4 AES双轮并行实现AES-CCM方案(左)AES双轮乒乓实现AES-CCM方案(右)Figure 4 Double wheel parallel(left)and double wheel ping-pang(right)implementation of AES-CCM

3.1 CCM控制模块的实现

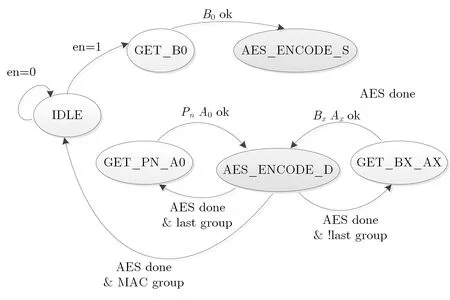

CCM模块主要由状态机构成,其状态跳转如图5所示.CCM的控制过程如下:

图5 CCM控制模块的状态机Figure 5 Finite state machine of CCM control module

(1)在IDLE状态下AES-CCM模块的使能信号有效后,执行第(2)步,状态由IDLE状态跳转到GET_B0状态.

(2)在 GET_B0 状态下,获取数据B0,数据准备好后,执行第 (3)步,状态跳转到AES_ENCODE_S状态.

(3)在AES_ENCODE_S状态下,使能AES加密模块,AES的加密模式配置为单数据组加密模式,只执行128比特数据加密.AES加密完成后,执行第(4)步,状态跳转到GET_BX_AX状态.

(4)在GET_BX_AX状态下,获取数据B x(P x−1)、A x,数据准备好后,执行第(5)步,状态跳转到AES_ENCODE_D状态.

(5)在AES_ENCODE_D状态下,使能AES加密模块,AES的加密模式配置为双数据组加密模式,执行2×128比特数据加密.AES加密完成后,若当前数据组不是最后一组数据,则执行第(4)步,状态跳转回GET_BX_AX状态,获取下一组数据;若当前数据组是最后一组数据,则执行第(6)步,状态跳转到GET_PN_A0状态,进行P n和A0数据获取;若当前数据组为MAC标志的数据组,表示所有待加密数据组均完成加密,CBC模式的加密输出生成MAC值,CTR模式的加密输出异或MAC值,以完成对MAC值的加密,至此AES-CCM的所有数据处理完成,状态跳转回IDLE状态,等待下一次AES-CCM的使能.

(6)在GET_PN_A0状态下,获取数据P n和A0,当P n和A0数据准备好后,则执行第(5)步,状态跳转回AES_ENCODE_D状态.

3.2 AES加密模块双轮并行实现

CCM状态机执行数据加密的状态只有AES_ENCODE_S状态和AES_ENCODE_D状态,AES_ENCODE_S状态完成128比特数据加密,每次启动AES-CCM加密协议,该状态只执行一次.AES_ENCODE_D状态完成2×128比特数据加密,每次启动AES-CCM加密协议,该状态根据数据包的长度多次重复执行,因此AES_ENCODE_D状态下的加密操作可以设计成两个AES并行执行或串行执行的方式,同时,由于CBC模式和CTR模式所使用的密钥相同,为了减少功耗和电路面积,可以共享密钥扩展模块,以轮并行和轮乒乓串行的方式替代两个AES并行执行或串行执行的方式完成2×128比特数据加密.

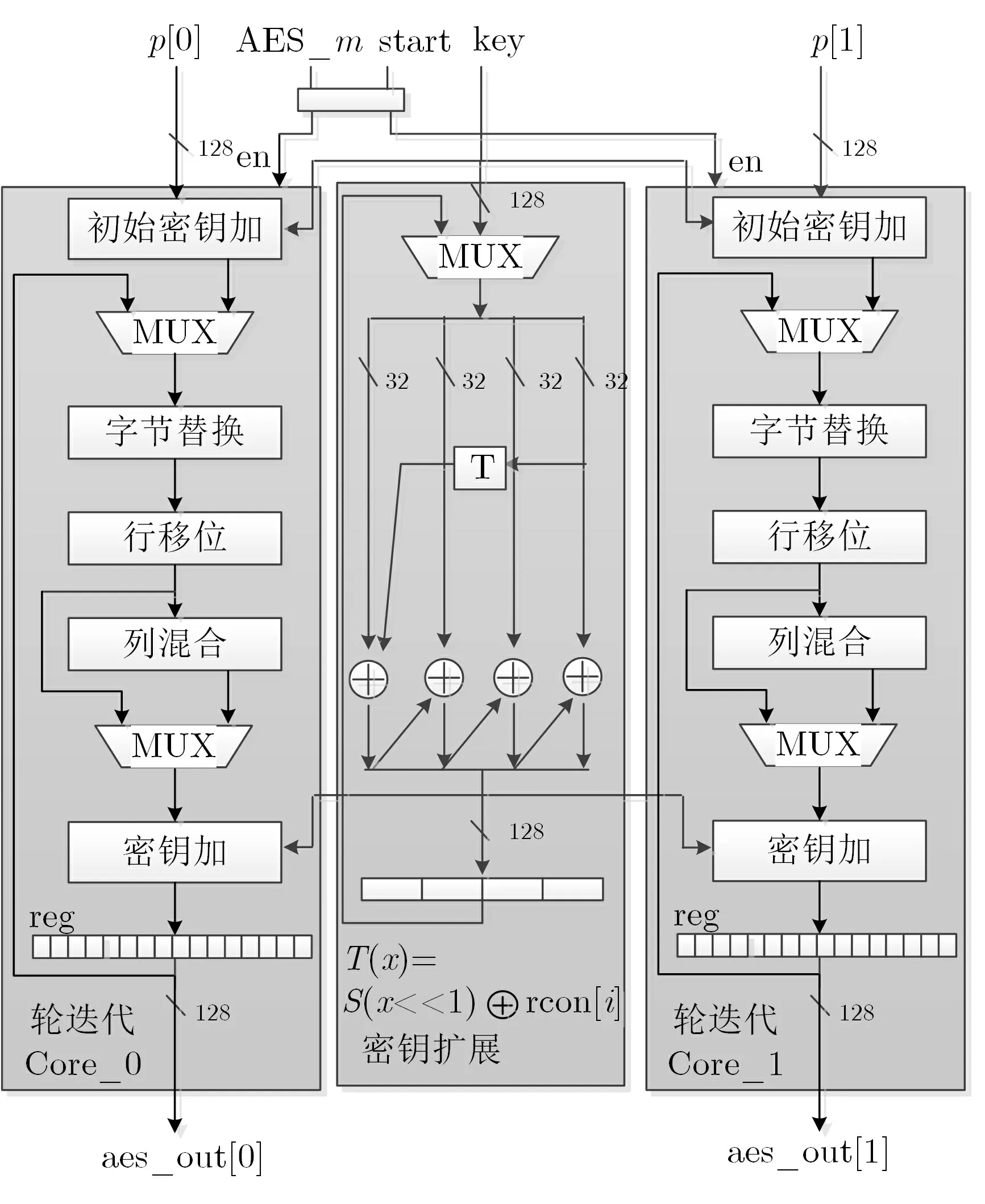

AES加密模块双轮并行实现的电路结构如图6所示,由两个轮迭代模块和一个密钥扩展模块构成.密钥扩展模块完成轮密钥的扩展,并共享给两个轮迭代模块使用,轮迭代Core_0和轮迭代Core_1分别完成两组数据的的轮迭代加密.两个轮迭代模块的使能信号单独控制,当只需要加密128比特数据时,只使能一个轮迭代模块,另一个轮迭代模块停止工作,以减小系统功耗;当并行加密2×128比特数据时,使能信号en[0],en[1]都有效,并行加密两组数据.

图6 AES双轮并行实现电路结构Figure 6 Circuit structure of AES double wheel parallel implementation

将该方案与传统双AES并行方案对比分析,我们发现,该方案减少了一个密钥扩展模块的电路实现和计算,从而减小了整体能耗和电路面积.

3.3 AES加密模块双轮乒乓实现

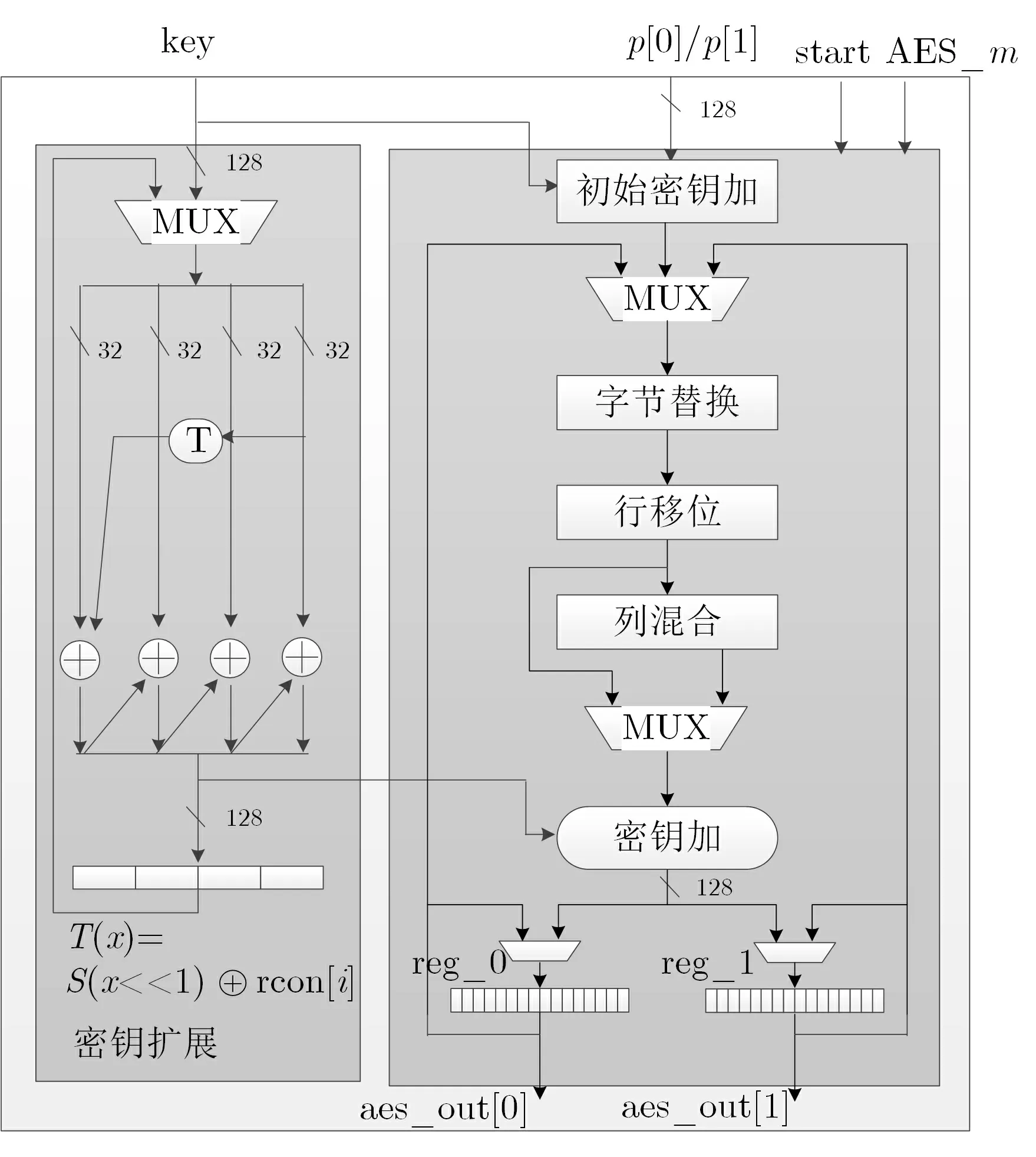

AES加密模块双轮乒乓实现的电路结构如图7所示,由一个轮迭代模块和一个密钥扩展模块构成.当执行128比特数据加密时,AES配置成单数据组加密模式,完成一次128比特数据加密需要10个周期,每个周期完成一次密钥扩展和一次轮迭代计算轮迭代模块的输出寄存器只用到reg_0,reg_1保持不变;当执行2×128比特数据加密时,AES配置成双数据组加密模式,完成2×128比特数据加密需要20个周期,每一轮函数计算由两个周期完成,周期1完成当前轮的密钥扩展和数据组0的轮迭代,并将轮迭代结果寄存至reg_0,周期2不需要执行密钥扩展,只完成数据组1的轮迭代,并将轮迭代结果寄存至reg_1.

图7 AES双轮乒乓实现电路结构Figure 7 Circuit structure of AES double wheel ping-pang implementation

将该方案与传统双AES串行方案对比分析,我们发现,完成2×128比特数据加密,该方案减少了10次密钥扩展的计算,从而减小了整体能耗,但是电路代价为多一组128比特的寄存器.

此外,以上两种AES加密方案在轮迭代模块和密钥扩展模块的S盒实现时利用了同构映射,将复合域GF(28)上的求逆运算映射到GF(((22)2)2)上[6-8],并对GF((22)2)域上的逻辑表达式以及相邻变换的表达式结合化简,进一步降低功耗,缩小关键路径的延时.

4 仿真综合验证

为了对方案的功能进行验证,我们对方案进行RTL代码实现,利用VCS仿真软件结合Testbench验证脚本和测试激励,完成各模块的功能验证.

AES的加密模式配置为单数据组加密模式时,只执行128比特数据加密,此时设置加密密钥为0x 66C6 C227 8E3B 8E05 3E7E A326 521B AD99,明文输入为0x 1387 F41E DD57 F3FB 9B9C 5B10 B514 CAD2,AES加密模块双轮并行例化模块和双轮乒乓例化模块的实验结果密文输出均为0x 60F9 EEDF 7F87 4C92 0AB1 7BFE 827D 9E66.

AES的加密模式配置为双数据组加密模式时,执行2×128比特数据加密,此时设置加密密钥为0x 66C6 C227 8E3B 8E05 3E7E A326 521B AD99,明文输入分别为0x 1387 F41E DD57 F3FB 9B9C 5B10 B514 CAD2和0x 0200 DEAF BABE BADC AB24 8000 0000 0001,AES加密模块双轮并行例化模块和双轮乒乓例化模块的实验结果相同,仿真波形分别如图8、图9所示,两组明文对应的密文输出分别为0x 60F9 EEDF 7F87 4C92 0AB1 7BFE 827D 9E66和0x AF65 6CCD 00CA B319 5E03 F945 F97B 969E.

图8 双数据组AES双轮并行加密实验结果Figure 8 Results of AES double wheel parallel implementation

图9 双数据组AES双轮乒乓加密实验结果Figure 9 Results of AES double wheel ping-pang implementation

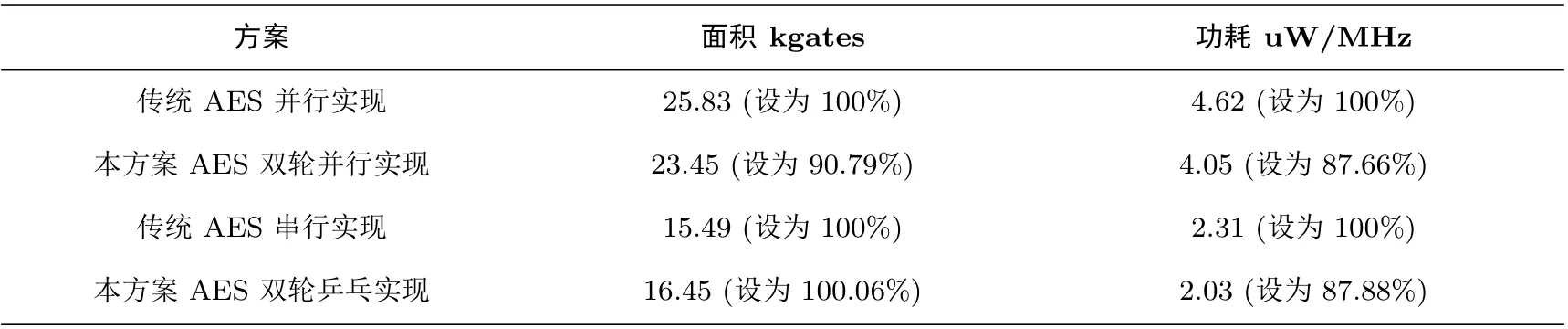

为了验证RTL代码功能正确性,我们对AES算法进行了软件实现,并将RTL仿真结果与软件加密模型对比,经对比密文输出一致,验证了AES两种例化方式的正确性.为了对方案的功耗和面积进行评估,我们在TSMC 65 nm、tt_1p0v_25c的工艺下用Design Compiler软件对不同方案的AES-CCM加密协议进行综合,在200 MHz的时钟约束下,传统双AES并行实现AES-CCM加密协议综合所得电路面积为25.83 kgates,功耗为4.62 mW;本方案所述AES双轮并行实现AES-CCM加密协议综合所得电路面积为23.45 kgates,功耗为4.05 mW;传统AES串行实现AES-CCM加密协议综合所得电路面积为15.49 kgates,功耗为2.31 mW;本方案所述AES双轮乒乓实现AES-CCM加密协议综合所得电路面积为16.45 kgates,功耗为2.03 mW.

表1 本方案与传统方案实现AES-CCM加密协议数据对比Table 1 Comparison of AES-CCM encryption protocol data between proposed scheme and traditional scheme

由以上分析可得与传统双AES并行实现AES-CCM方案相比,AES双轮并行实现AES-CCM方案的面积和功耗分别减小9.21%和12.34%;与传统双AES串行实现AES-CCM方案相比,AES双轮乒乓实现AES-CCM方案的面积增加0.06%,功耗减小12.12%.

5 结论

本文根据AES-CCM链路层数据加密与解密都只用到AES加密模式,且数据校验值生成与数据加解密密钥相同的特点,给出基于AES双轮并行模块、AES双轮乒乓模块的AES-CCM通用协处理器实现方案,用户根据应用需求选择性例化实现.方案中采用轮密钥共享机制,以及AES算法S盒复合域化简实现方法,有效去除冗余电路,减小了电路功耗.