电荷泵锁相环行为级建模研究

谢宁波,高健超

(1.桂林电子科技大学 信息与通信学院,广西 桂林 541004;2.桂林市桂电中学教务处,广西 桂林 541004)

0 引 言

在现代通信系统中,稳定而精准的时钟电路是系统正常工作必不可少的基本模块。其中,传统的压控振荡器(Voltage Controlled Oscillator,VCO)因功耗高、稳定性差、频率范围窄且难以集成等缺点,已不能满足现代高性能电子设备的需求,采用锁相回路构建高稳定性、宽频带输出的频率合成器是当今的主流解决方案[1,2]。

另外,基于锁相环实现的高速频率合成器电路设计复杂,涉及多模块的结构及参数设计优化,如果直接基于传统的晶体管级电路设计流程进行电路搭建、仿真、结果分析、结构调整进而迭代,那么该方法将面临仿真数据量大、耗时长以及误差积累严重等问题。为此,本文从PLL的系统行为级建模出发,基于Verilog-AMS语言对PLL环路进行建模描述。通过EDA仿真实验验证环路参数对系统的影响,并通过参数迭代优化提升系统的性能指标。行为级建模仿真可有效减少仿真耗时和设计的复杂度,对电路级设计具有前瞻性的指导意义。

1 PLL系统结构

典型的基于电荷泵的锁相环由鉴相器(Phase Detector,PD)、电荷泵、环路滤波器、压控振荡器以及分频器5部分构成,其结构如图1所示。

图1 典型PLL结构

锁相环是一种典型的反馈控制电路,其中鉴相器用于比较外部参考信号与反馈信号之间的相位和频率差,将比较出来的相位差转换为电压信号输出给电荷泵。电荷泵受鉴相器输出信号控制,以电流源对后级充放电的方式为压控振荡器提供控制电压。环路滤波器的目的是过滤环路中的噪声和高频毛刺,以增强环路稳定性。压控振荡器作为环路的核心,受电荷泵输出的电压控制,其输出的信号频率受反馈环路的控制逐渐逼近目标频率和相位。而分频器将锁相环的输出信号和输入参考时钟的频率形成一个倍数关系,最终在环路平衡时完成环路锁定。

2 PLL行为级建模

2.1 环路参数计算

PLL的设计涉及到多模块的参数选择,主要包括鉴相器的增益系数KPD、压控振荡器的增益系数KVCO、环路滤波器的器件参数及带宽ωbw以及分频器的分频倍数N。这些参数对系统的稳定性和环路锁定时间起到决定性的作用,对其进行研究和分析是行为级建模的目的和意义。通过分析环路的传输函数,可对上述参量的选择作进一步的分析。

已有大量文献对环路参数的计算作详实的分析,现简单总结如下[3-5]。环路的闭环传输函数表示为:

2.2 模块行为级建模

2.2.1 鉴相器

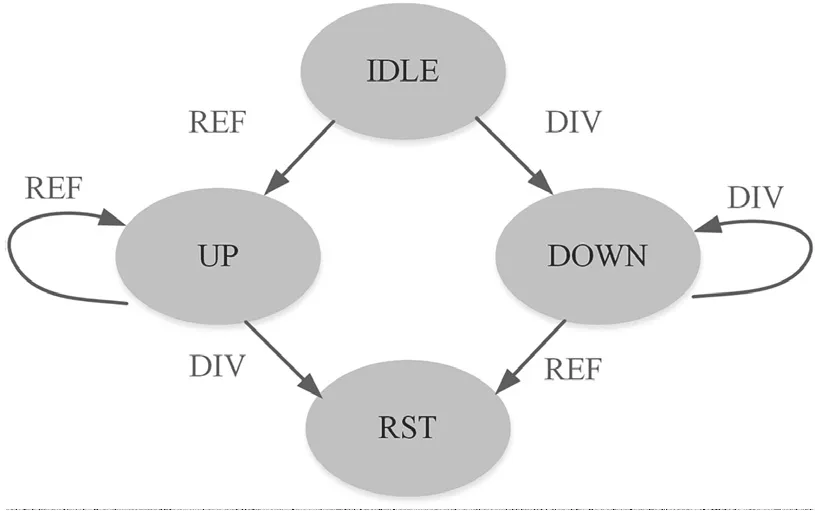

鉴相器的作用是将参考信号与反馈信号之间的相位差转换为电压信号UP和DOWN,以控制电荷泵输出。不同于晶体管级电路设计,在行为级建模上,该模块的工作原理本质上可视为输出状态的转移,其状态转移过程可简化为如图2所示。

图2 鉴相器行为级建模状态转移

其工作过程简单介绍如下,假设参考信号和反馈信号之间存在相位差且初始状态为IDLE,如果鉴相器PD检测到REF信号时钟上沿先于DIV信号到来,则转为UP状态,UP信号输出为高。下一步,如果PD检测到的依然是REF的时钟上升沿,则保持当前状态,如果检测到的是DIV时钟沿,则此时转为RST状态,反之亦然。值得注意的是,鉴相器不存在UP和DOWN同时为“1”的状态。

2.2.2 电荷泵

电荷泵由PD输出的UP和DOWN信号控制,其原理可等效视为一个受UP和DOWN电压信号所控制的为负载电容进行充放电的通路。一般而言,典型的电荷泵通路可等效视为正向充电的电流源和反向放电的电流源构成,行为级建模时以两个理想电流源Ip和In来表示。

2.2.3 环路滤波器

典型的PLL环路滤波器由二阶RC电路构成。其行为级建模可直接调用Verilog-AMS语言的内建原语resistor和capacitor来实现,同时调用及例化时需要注意端口匹配。此外,器件参数初始选择参考环路参数计算,后续仿真验证时会根据仿真结果对其作调整优化。

2.2.4 压控振荡器

压控振荡器的电路模型为:

式中:ωout为VCO的瞬时输出频率;ω0为VCO的中心频率;KVCO为VCO的频率增益系数,理想化模型下是一个常数;Ucont为VCO的控制电压,即电荷泵的输出电压。

上述模型是频域模型,行为级建模时需要对应到时域模型,其本质上是角频率对时间的积分,故对VCO进行行为级建模可利用内建的积分函数idt( )及信号的正弦表示来实现。

2.2.5 整数分频器

为简化系统分析,本设计所使用的分频器采用整数分频,暂不涉及小数分频,故分频器的行为级建模利用简单的计数器来描述。通过设置一个变量count用作计数,使用cross( )函数对VCO输出的时钟沿作统计,当计数到设置的阈值则输出分频信号。

2.3 系统级建模设计

在完成各模块建模的前提下,将各模块按照系统结构顺序连接组合即可得到系统层面的行为级建模。具体来说,先完成分模块的行为级描述并创建独立的文件,进而例化各模块并利用端口映射关系完成系统各模块的连接和信号传递。为简化仿真过程,可以把需要迭代优化的参量全部写在一个参量定义文件中,利用参数传递的方式进行迭代修改。

3 系统仿真验证

仿真和验证的功能是检查设计的正确性,同时也是系统不断修正、改进以及优化的过程。为整个系统设计一套比较完善的验证方案,验证系统的功能正确性并总结分析影响系统稳定性和性能的参数作用机制。

3.1 设计参数指标

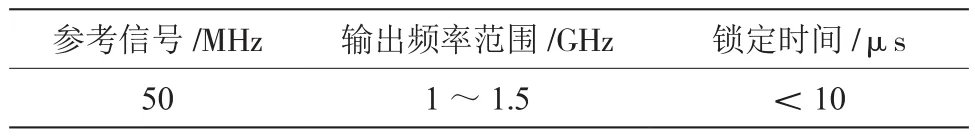

由于行为级建模仅为电路级设计的参考和指导,并不限定于具体的应用需求,故本设计的参数指标设定进行了一定的简化。本设计的参数指标描述如表1所示。

表1 系统参数指标

3.2 功能验证

通过验证环路是否能跟踪参考信号变化并成功锁定来验证设计的正确性。从图3(a)可得REF信号和DIV信号已达到相位锁定,同时VCO输出的信号频率与设计的分频倍数相符合。图3(b)反映了锁相过程中VCO控制电压的变化趋势,相位锁定过程大约需要3.8 μs,符合预期,且信号的纹波在可接受范围。

图3 环路瞬态仿真结果

3.3 环路参数对系统性能的影响

研究环路参数对系统的稳定性和环路锁定时间的影响是行为级建模的目的和意义,对后续电路级设计和迭代优化具有前瞻性的指导作用。这里主要分析电荷泵充放电电流、环路滤波器选择以及VCO增益系数对设计的影响,通过仿真结果分析可总结如下。

一是VCO控制电压的增益与充放电电流成正比,同时充放电电流的不匹配会在一定程度上影响环路的锁定时间。当充放电电流失配时,锁定时间比电流匹配时增加了几百纳秒的时间,故电路级设计时应尽量满足充放电电流的匹配。二是环路滤波器的设计对系统的稳定性和锁定时间有极大的影响,且两者是一对互相牵制的参数指标。三是VCO的增益系数在实际模型中与控制电压不再是线性关系,其非线性关系会使得PLL的锁定时间变长,且会引起抖动或失锁问题,故电路级设计时需考虑从电路结构或者器件特性上尽量避免非线性问题。

4 结 论

本文系统总结了基于Verilog-AMS的电荷泵锁相环行为级建模的方法和相关理论研究,通过仿真实验验证了设计的正确性,并针对环路参数对系统稳定性和性能的影响等相关问题进行较为充分的分析,从而为后续的电路级设计提供重要的理论依据和指导作用。