面向超高速采样数据传输的差分互连结构设计与优化

张紫文,林文涛,王 琳,胡 忞,易朋兴

(华中科技大学机械科学与工程学院,湖北武汉 430074)

0 引言

随着电子技术和集成电路技术的快速发展,传输线上的信号速率达到了GHz领域,而在高速电路系统中,PCB板的设计不仅要实现信号的连通,还要考虑到电路中存在的信号完整性问题,随着信号传输速率增加,PCB上过孔等结构会严重影响信号传输的质量,成为了影响电路性能的重要因素[1]。

在高速信号领域中,差分传输线相比于单端传输线具有更强的抗干扰性、更好的抗电磁干扰能力等特点,因而在高速电路的设计中得到了广泛的应用。目前国内外学者对差分传输线进行了大量的研究,文献[2]分析了传输线耦合引发差分传输线共模噪声的机理,文献[3]研究了孔径、焊盘直径等参数对差分过孔的差分性能和共模性能的影响,文献[4]研究了差分传输线横截面的几何不平衡对信号串扰的影响,文献[5]利用时域有限差分仿真验证非理想回流路径对差分信号完整性的影响,这些研究大多数针对差分传输线的局部进行性能分析,而对差分互连结构的整体设计对信号传输能力的影响关注较少。

针对超高速采样数据传输网络,采用了一种基于分段传输线的差分互连结构,该结构将差分传输线进行分段处理,通过粒子群算法搜索具有良好传输质量的传输线结构参数,并在ADS仿真软件中建立基于分段传输线的差分互连结构模型,结合眼图对其进行分析。

1 超高速采样数据传输网络

超高速采样数据传输网络是指超高速采样系统中的ADC芯片和FPGA之间的差分信号传输路径,经过ADC芯片模数转换后的数据以LVDS差分信号的形式向FPGA进行传输,采用差分线的结构设计可以有效降低高速信号传输时的电磁干扰,提高数据的传输能力。

但是理想的差分传输线是难以实现的,过孔、互连拓扑结构、互连线跨分割等因素都会导致互连传输线的阻抗发生变化,而阻抗的改变又会引起传输信号在该处发生反射,影响高速信号的传输质量,传输线间互容耦合、互感耦合引起的串扰问题,会影响信号的边沿和幅度,降低信号的质量,反射和串扰这2个因素都会影响采样系统的信号完整性,而从ADC芯片输出的差分信号的传输速率可达到1.6 Gbit/s,此时,反射和串扰问题会极大影响数字信号传输的质量,从而降低了整个超高速采样系统的性能。

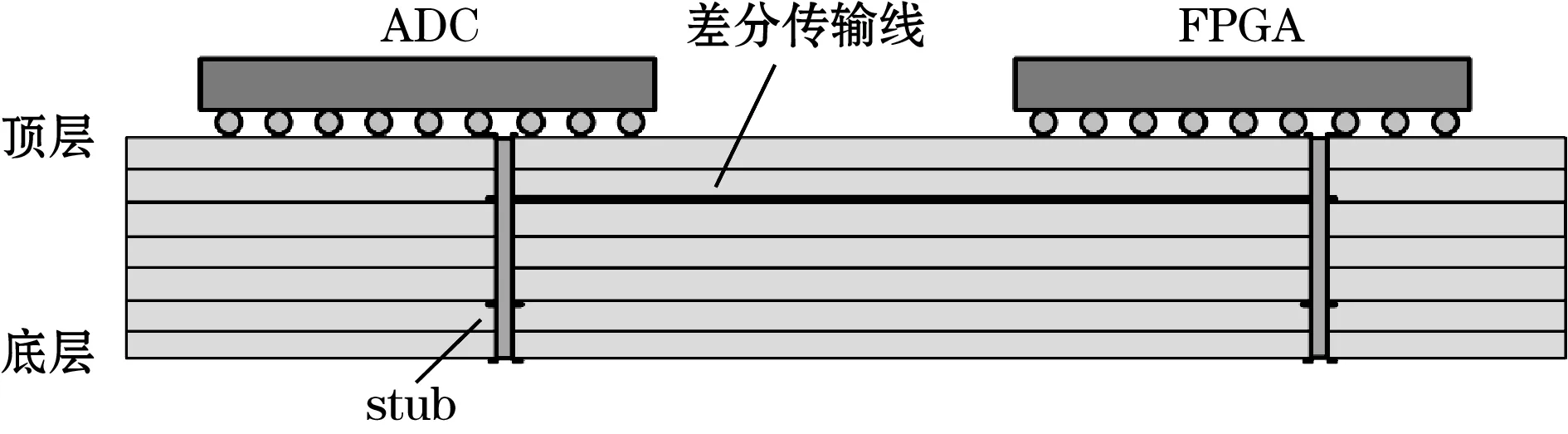

超高速采样系统中的ADC芯片和FPGA置于板卡的外表层,芯片采用的是BGA封装形式,图1为高速数据的传输路径,考虑到PCB板内层的布线空间大,并且带状线受到的电磁干扰以及相邻信号线间的串扰都比表层微带线要小,因而ADC芯片与FPGA之间的LVDS信号线采用内层走线的方式,然而互连线需要通过过孔换层,过孔是传输线上的一个阻抗不连续点,过孔焊盘带来的寄生电容以及过孔的stub带来的短截线效应会加大传输线的延时,减小互连通道的带宽,影响电路系统的信号完整性。

图1 差分信号的传输路径

2 基于分段传输线的差分互连结构设计

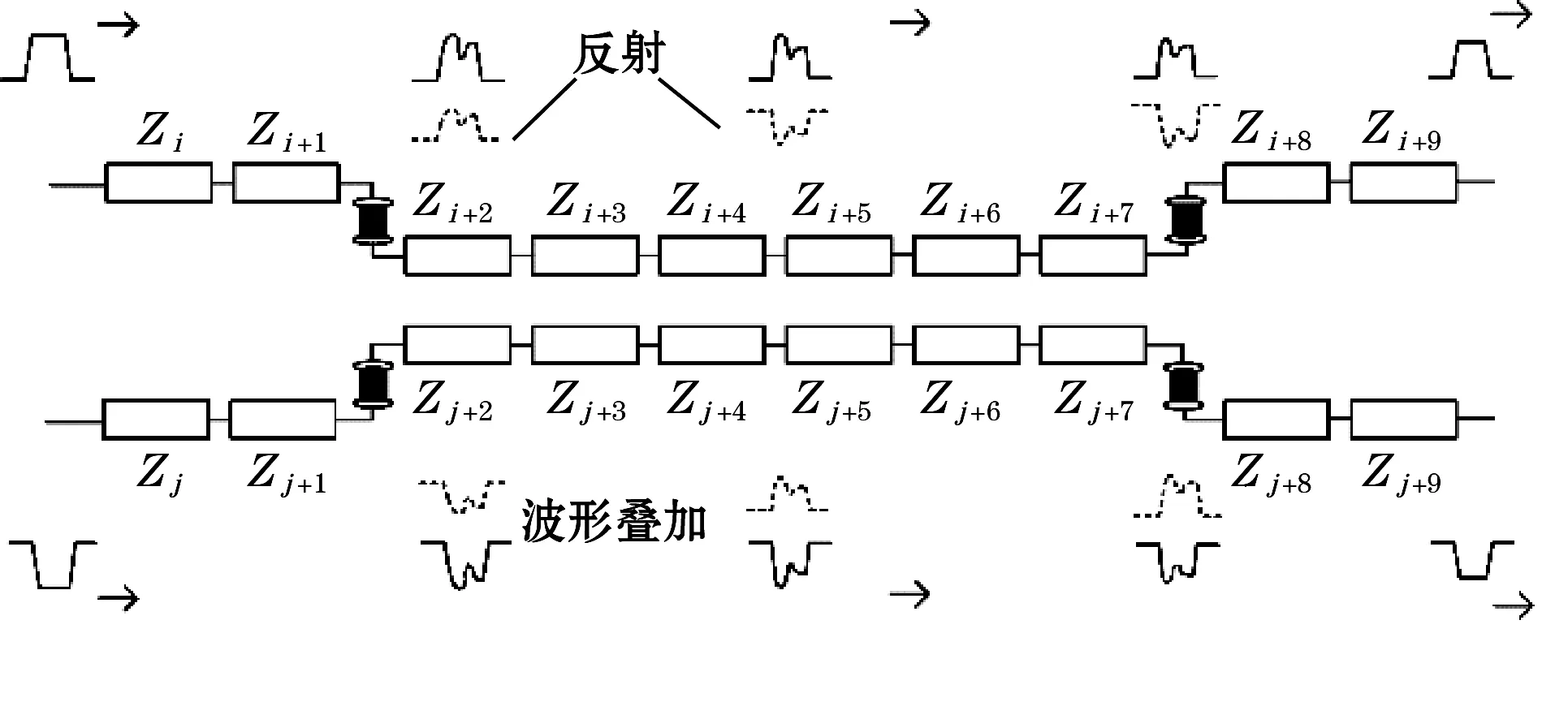

常规基于阻抗匹配的传输线结构如图2所示,在MHz频域内,常规传输线结构可以用来降低信号的反射,改善信号完整性,但是到了GHz频域以后,过孔带来的影响就很突出,用这种方式难以减小这种影响,因而为了解决这个问题,采用一种基于分段传输线的差分互连结构,图3为这种结构的示意图,信号沿传输线传播时,只要遇到瞬时阻抗突变,就会发生反射,反射的电压Vreflect为

图2 常规差分传输线结构

图3 分段差分传输线结构

(1)

式中:Vinc为入射电压;Z2为反射点的阻抗;Z1为传输线的阻抗。

当信号通过阻抗变化点时,可能会发生正反射或负反射,这些反射又会与路径上其他阻抗变化点产生的反射相叠加,使反射增大或者减小,如果各小段传输线的阻抗设置合适,则可以减小由过孔带来的影响[6]。

对于FR4材料的边缘耦合微带线,差分阻抗Zdiff近似为[7]

(2)

式中:Z0为未耦合时的单端特性阻抗;s为走线的边缘间距;h为信号线与参考平面之间的介质厚度。

(3)

式中:εr为介质的介电常数;w为信号线的宽度;t为信号线的厚度。

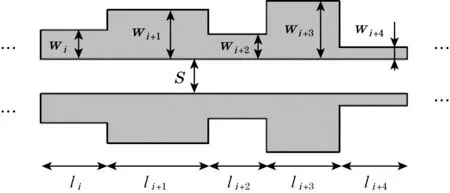

由式(2)和式(3)可知在介质材料确定的电路板中,对传输线差分阻抗的调整实质上是对传输线宽度w和间距s的调整,而各小段传输线的长度l会影响反射信号叠加的时序,进而影响信号的传输质量。图4为分段差分传输线的结构设计,将这种分段结构应用在LVDS差分传输线上时,通过调整分段差分传输线的宽度w、间距s以及长度l,从而在信号接收端获得良好的信号波形。

图4 分段差分线的结构设计

过孔根据连接方式不同可以分为通孔、盲孔及埋孔,实验中的差分过孔采用通孔结构,为了方便后续的仿真分析,将通孔模型进行简化等效,图5为通孔的等效模型,PCB上的通孔结构存在着寄生电容和寄生电感,通孔的寄生电容C和寄生电感L的大小近似为

图5 通孔的等效模型

(4)

式中:εr为介质的介电常数;T为PCB板厚度;D1为焊盘直径;D2为反焊盘直径。

(5)

式中:h为孔的长度;d为孔径。

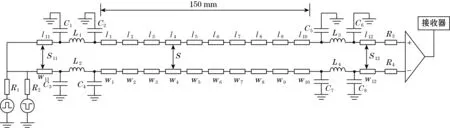

基于分段传输线的差分互连结构的设计模型如图6所示,其中w1~w10为各段的线宽,l1~l10为各段的线长,s为线间距,ADC为BGA封装,芯片引脚比较密集,通常采用就近过孔换层走线的方式,顶层的一小段传输线对整体结构影响不大,因而将顶层线宽w11、w12,顶层线长l11、l12和顶层线间距s11、s12设为固定值,将PCB内层的差分传输线进行分段处理,每段的长度、宽度以及2个传输线间的距离作为变量,传输线的总长为固定值,通过接收器观测差分输出信号。

图6 基于分段传输线的差分互连结构设计模型

3 基于粒子群算法的差分互连结构优化

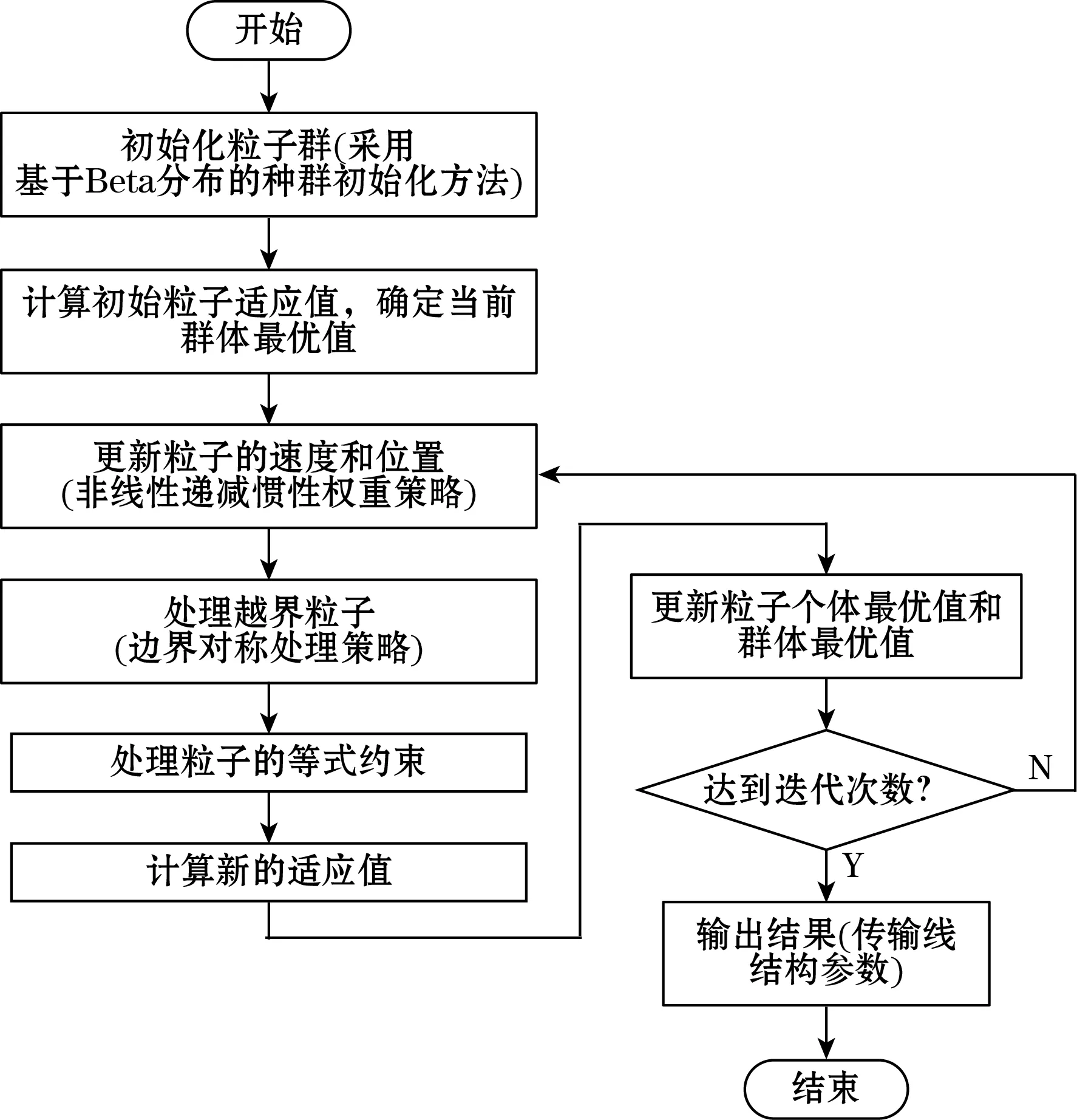

为了使分段差分传输线结构输出良好的信号,传输线参数的搜索空间将会变得非常大,采用粒子群优化算法来解决多个参数变化带来的组合量过大的问题。粒子群算法具有较快的计算速度以及全局搜索能力,是一种高效的并行搜索算法[8-9]。图7为粒子群算法的流程图,当粒子群算法用于差分互连结构优化时,分段差分线的各段线长、线宽以及线间距作为粒子,通过粒子的搜索来确定传输线的结构参数,这也同时需要建立评估差分互连结构适应度的函数以及处理差分互连结构带来的等式约束问题。

图7 粒子群算法流程图

3.1 差分互连结构适应度评估函数

通过接收端信号的眼图对差分互连结构的适应度进行评估,眼图能够体现数字信号的整体特征,可以很好地评估数字信号的质量,而眼宽和眼高是眼图中2个关键的参数,眼宽反映了传输线上信号的稳定时间,眼高反映了信号的噪声容限,这2个参数可以基本反映数字信号的传输质量,将眼宽和眼高共同作为适应度的评估指标,粒子群的适应度评估函数为

fitness=aTwidth+bVheight

(6)

式中:权重a和b为自定义常量,a=5×1011,b=500;Twidth为眼宽,ns;Vheight为眼高,V。

每一代的差分线结构参数输出成电路描述文件,然后将描述文件代入到电路仿真软件中,再将仿真得到的眼图参数导入到适应度评估程序中,从而来计算差分互连结构的适应度。

3.2 等式约束处理

分段差分传输线通过波形的叠加来减小信号在传输过程中遇到的反射和串扰等问题,而波形叠加的时序受到了总传输时间的影响,因而要控制分段传输线的总线长为固定值,即要对粒子群进行等式约束处理,本文处理等式约束的方法是进行分段传输线长度的重新分配和重新组合,等式约束的处理步骤如(1)~(3)所示:

(1)检查等式约束是否成立。如果等式约束成立,则分段传输线的长度分配合理,如果不成立,则继续后续步骤。

(3)检查重新分配后的等式约束是否成立。如果等式约束成立,则分段差分传输线的各段长度分配合理,如果不成立,则转向(2)继续进行。

4 实验结果与分析

4.1 TDR阻抗分析

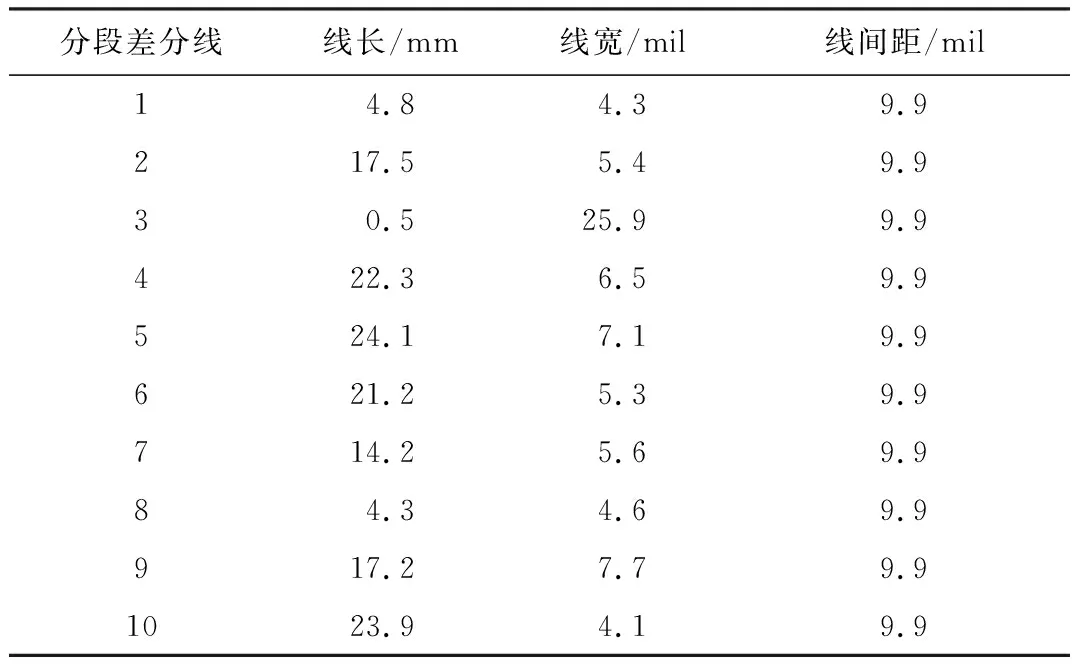

通过粒子群算法得到分段差分线的结构参数,其各段的线长、线宽及线间距如表1所示(1 mil=0.025 mm),将这些参数代入到ADS建立的分段差分线模型中,并对其进行TDR仿真,将生成的结果与基于阻抗匹配的差分传输线的结果进行对比分析,得到如图8所示的差分阻抗曲线。

表1 分段差分传输线的设计参数

图8 TDR差分阻抗曲线

图8中的曲线显示了2个不同传输线结构阻抗不连续点的位置,其中曲线的向下凹陷处为差分过孔在传输线上形成的阻抗突变点,一般情况下,差分传输线的差分阻抗为100 Ω,常规传输线的阻抗除了过孔处出现阻抗突变,其余部分均平稳地分布在100 Ω附近,而分段差分线结构的阻抗则在75~120 Ω区间中波动,差分线结构上有多个阻抗不连续点。

4.2 眼图分析

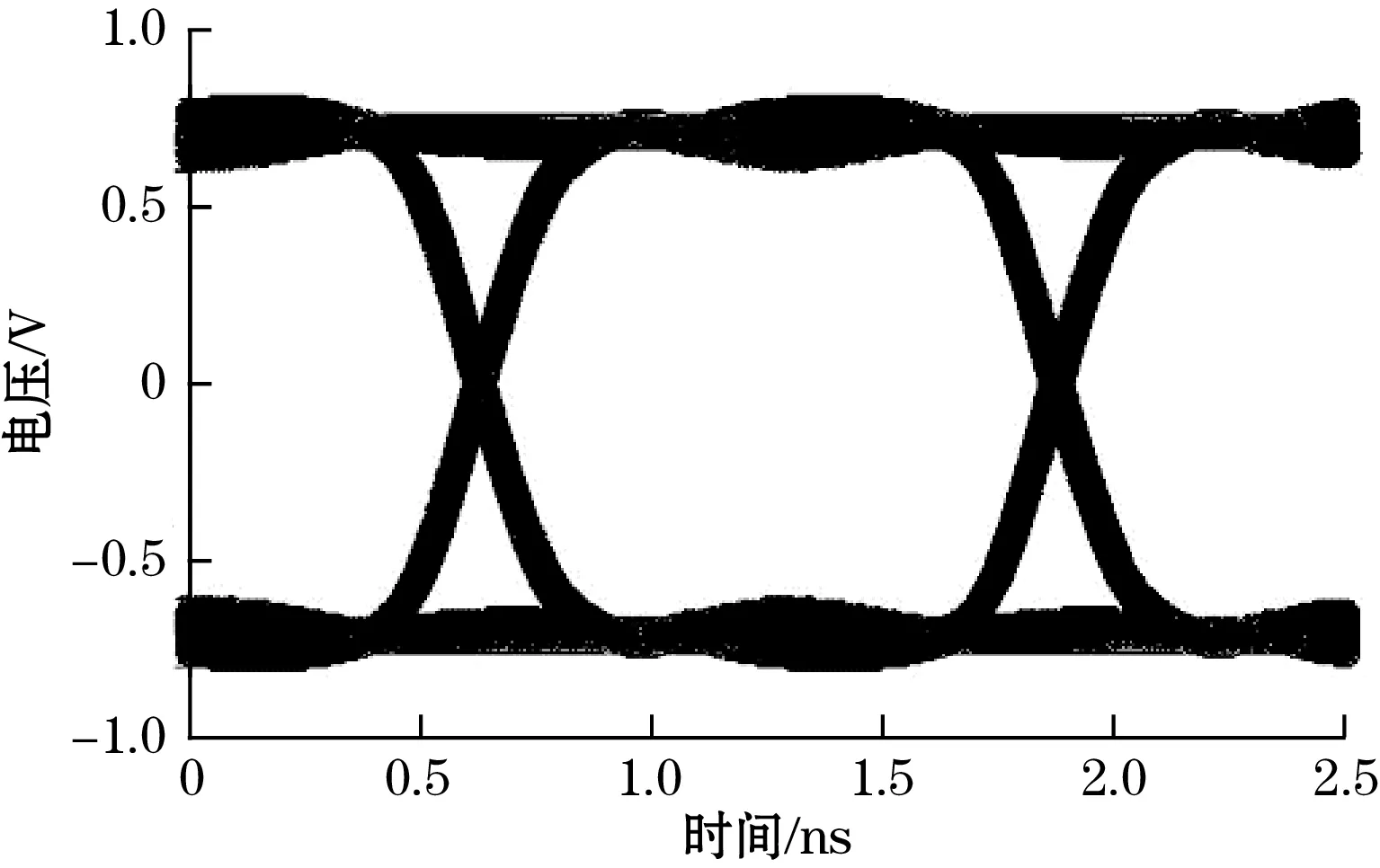

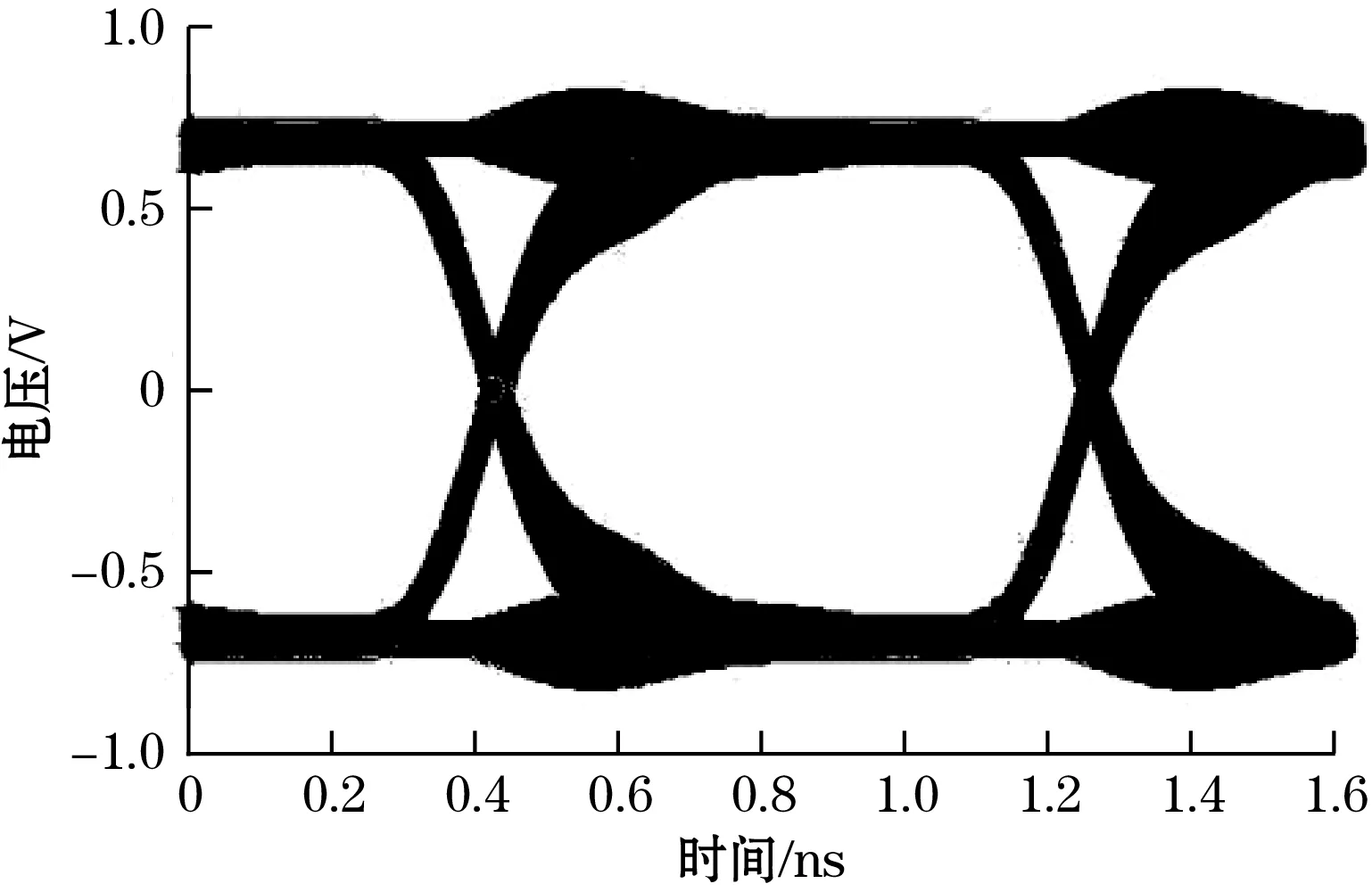

ADC芯片的高速采样数据的输出速率在800~1 600 Mbit/s之间,分别在800、1 200、1 600 Mbit/s传输速率下,对常规差分传输线以及基于分段传输线的差分互连模型进行有源通道仿真,得到如图9~图11所示的眼图。

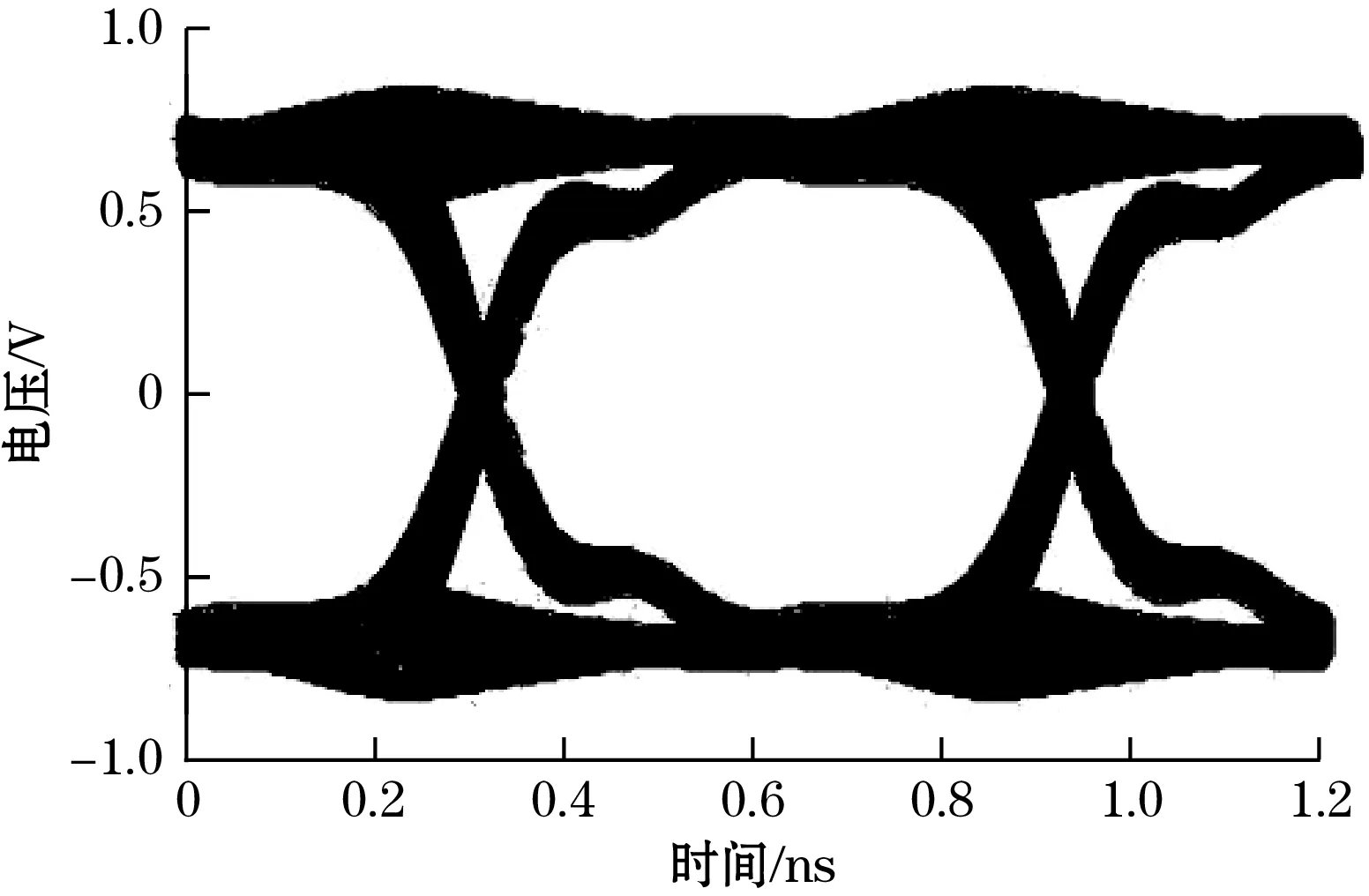

(a)常规差分传输线

(b)分段差分传输线图9 800 Mbit/s传输速率下2种不同传输线结构的眼图

(a)常规差分传输线

(b)分段差分传输线图10 1 200 Mbit/s传输速率下2种不同传输线结构的眼图

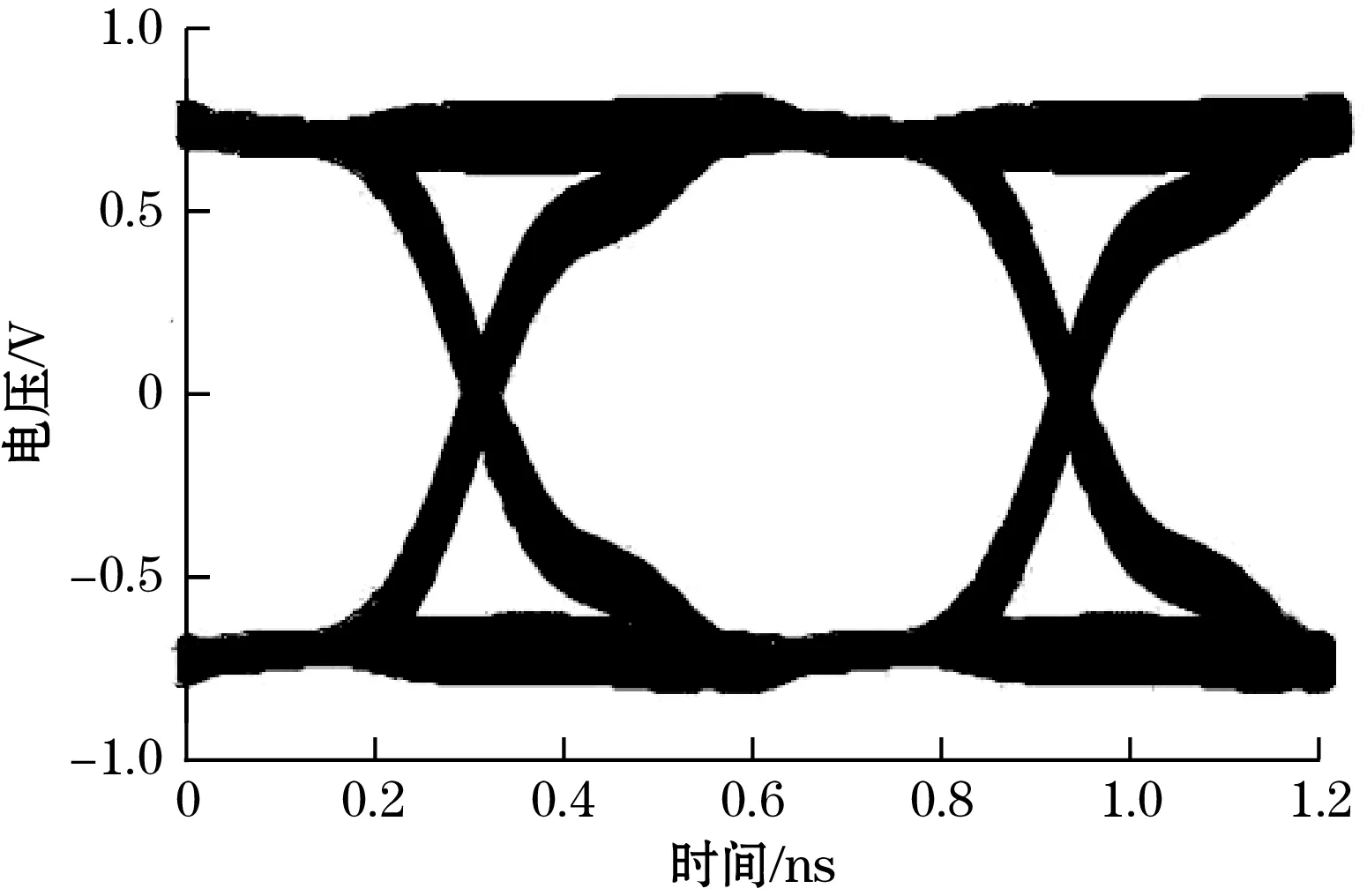

(a)常规差分传输线

(b)分段差分传输线图11 1 600 Mbit/s传输速率下2种不同传输线结构的眼图

表2显示了2种不同传输线下眼图的测量结果,从常规传输线的眼图可以看到,信号在传输时出现了较大的反射和噪声,导致眼图的眼高减小、眼图面积缩小,而采用了分段差分互连结构的传输线,其眼高得到了明显的改善,最大达到了1.369 V,抖动减小,眼图面积更大,信号传输的整体质量更好,并且随着传输速率的增加,常规差分传输线噪声抖动不断增大。在1 600 Mbit/s时达到了最大,其中峰峰值抖动为28.13 ps,均方根抖动为7.122 ps,而分段差分传输线的信号受到的影响较小。因而验证了采用基于分段传输线的差分互连结构能够有效地减小噪声抖动,进而提升LVDS差分信号线的传输质量。

5 结束语

针对超高速采样系统中的ADC与FPGA之间的LVDS差分传输线结构进行了信号完整性设计,采用一种基于分段传输线的差分互连结构来解决过孔带来的信号完整性问题,利用粒子群算法求解带约束的分段差分传输线的结构参数,有源通道仿真结果显示了与常规差分传输线相比,使用分段差分传输线的眼图的眼高和眼宽更大,信号的抖动更小,表明基于分段传输线的差分互连结构的信号完整性优于常规的差分互连结构,该研究为实际中设计高速差分传输线提供了一些参考。