基于1553B 总线的FPGA 在线升级

韩子舟,任勇峰,李辉景

(中北大学仪器科学与动态测试教育部重点实验室电子测试技术重点实验室,山西太原 030051)

FPGA 可重配置的特性为相关电子设备的设计提供了很高的灵活性,可以在生产过程和后期维护中根据不同的需求进行更新,保障产品的可靠及稳定运行[1-3]。传统的程序升级是打开产品外壳,由USB-JTAG的连接方式实现程序的升级。但是,由于一些设备已经交付或已经进行特殊工艺处理,不具有拆卸再次进行程序升级的条件,无法通过USBJTAG 专用线缆和仿真器的方式进行升级[4-5]。针对该难题,文中提出了一种基于1553B 总线的固件更新方法,该方法能够通过现有的1553B 通信接口完成程序的在线更新,无需进行额外的硬件改动,解决了以往只能拆卸产品,再通过专用线缆及仿真器进行程序升级的问题。

1 总体方案设计

总体设计方案如图1 所示,由1553B 通信模块和FPGA 控制模块组成。1553B 模块主要负责与测试台进行通信,实现命令和配置数据的接收,再将其传输到FPGA控制模块中;FPGA控制模块负责接收1553B模块传来的指令和配置文件,实现对Flash的分区擦除、写入等操作。同时,由ICAPE2 模块实现了对FPGA的重配置及Fallback 模式的配置,充分利用FPGA的可编程资源[6-7]。如果在程序升级时,设备断电致使升级失败,则FPGA 在上电后会触发Fallback模式,保证配置文件能够通过外部接口实现升级。

图1 总体设计方案

2 硬件设计方案

2.1 1553B通信模块

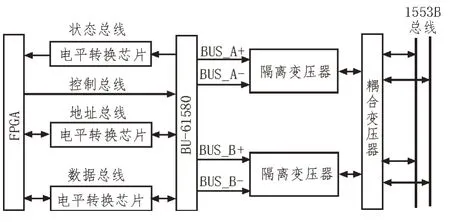

在固件更新时,需要由1553B接口接收命令,并进行相应的操作,电路原理框图如图2 所示。FPGA 对1553B 主控模块BU-61580的控制主要是利用地址总线、数据总线、控制总线、状态总线完成的[8-9]。所用FPGA的接口电平为3.3 V,BU-61580的接口电平为2~5.3 V,控制总线上的指令是从FPGA 传送至BU-61580 芯片中,因此该方向不需要进行电平匹配。而地址线和数据线传输方向是双向的,接口电平会对FPGA 接口产生冲击,因此需要进行电平转换;状态总线上的数据是从BU-61580 向FPGA 传输的,所以也应该转换电平,电路原理框图如图3 所示。

图2 1553B总线接口电路

2.2 FPGA配置电路设计

文中以Xilinx Kintex-7 芯片为例,在进行FPGA配置时,有7 种方式可以选择,分别是主串、主并、主SPI、主BPI、从串、从并及JTAG 配置模式,通过设置M2、M1、M0 3 个引脚的高低电平选择配置模式。

该设计分别将M2、M1、M0 进行下拉、下拉、上拉,把配置模式设为主SPI 模式,配置电路如图3 所示。这种配置模式只需要外挂一个SPI 存储器即可,不仅所需的FPGA 资源少,而且SPI Flash 尺寸小,能够最大化利用电路板狭小的面积[10-11]。

图3 Flash配置电路

3 逻辑设计

3.1 1553B逻辑设计

在设备上电复位以后,1553B 模块首先要做的就是对BU-61580 进行初始化配置,其配置包括寄存器配置和存储器配置。由于BU-61580 模块不具备记忆功能,一旦下电所有配置信息将会丢失,因此需要上电之后对其再次进行配置[12]。而且每次上电之后配置的信息是一致的,故该设计将相关配置信息存储在FPGA的ROM 中,上电之后只需把要配置的数据及地址读出,分别送到数据线及地址线上,发送给BU-61580 即可完成配置。

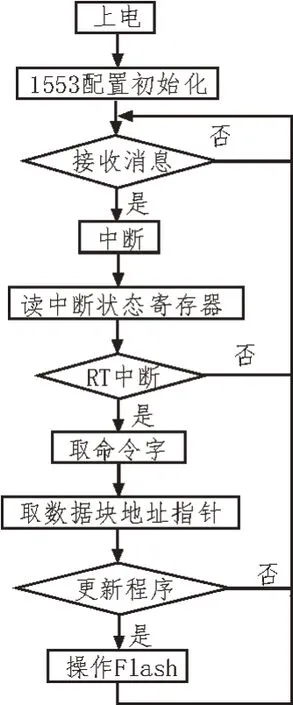

在完成配置之后等待接收消息,每接收完成一条消息就会进入中断,然后读取中断状态寄存器判断中断类别。若为MT 中断则重新回到数据等待接收状态;若为RT 中断,则需要取出区域A的栈指针,然后根据指针指向地址取出命令字,并执行相应操作。更新程序中主要需完成3 种操作,首先是擦除指令,将需要更新的代码全部删除;其次是写指令,把新的代码写入指定的地址,完成更新。在写操作时,需要根据数据块指针,取出1553B 所接收的程序再转发给下一级的FIFO;最后是写关闭指令,在完成程序更新后拉低写使能信号,结束数据的传输。1553B 操作流程如图4 所示。

图4 1553B操作流程图

3.2 固件更新逻辑设计

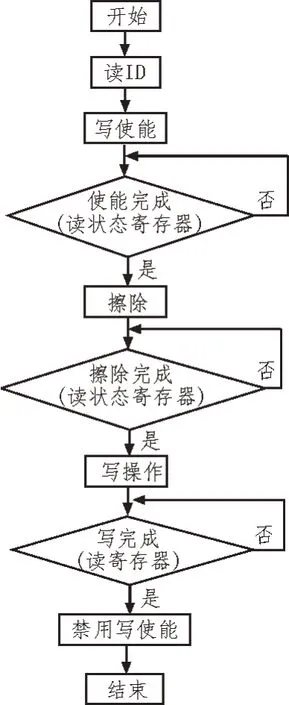

固件更新主要由两部分组成,分别是状态控制模块和Flash 操作模块。状态控制模块主要完成指令的识别,以及要发送指令的赋值操作,完成赋值后进入Flash 开始操作。操作结束后对之前的赋值进行清零,然后进入待机状态等待下一条指令。Flash操作模块主要控制读写寄存器,发送地址与数据,固件更新流程如图5 所示[13]。

图5 固件更新流程

Flash的工作状态主要有识别设备ID、写使能、擦除、写禁用、读状态寄存器、读写数据。FPGA 接收到程序升级的命令以后,首先要进入识别ID 状态得到设备ID。在识别完成后,发送写使能指令,以获取擦除操作的权限。当从状态寄存器中读取到写使能已开启,便开始对Flash的指定地址进行擦除。根据芯片手册,S25FL256S 支持一次擦除的扇区大小为64 kB,而固件存储区域为10 MB,因此应该循环擦除160 次。最后还需通过读取状态寄存器的值,检验擦除是否完成。

Flash 擦除完成后,再由计算机下发需要更新的程序。首先FPGA 将从1553B 总线上接收的程序送入FIFO 中缓存,然后对FIFO的空信号进行判断。若不为空,则把数据送入Flash 中。从图5的操作流程图可知,先由FPGA 下发写使能命令,使得Flash 中存储区域可供修改,再下发写指令、固件数据及页地址。S25FL256S 页编程一次只支持写入256 个字节的数据,因此需要循环提供写使能和写指令给Flash,直至数据全部写入。当判断到FIFO 为空时,开始计时等待。若FIFO 中出现数据,则继续写入Flash 中;若连续等待1 s FIFO 依然为空,则断定数据更新结束,关闭写操作,重新禁用写使能完成配置工作。

3.3 重配置逻辑设计

FPGA 多重配置技术实际是对可编程资源的复用,用户可以根据需求加载不同的配置文件,从而实现多重配置[14]。FPGA 多重配置技术不仅提高了对资源的利用率,还提高了设计的灵活性,使设备易于后期维护与更新[15-16]。多重配置技术主要是由ICAPE2 执行内部编程指令(IPROG)实现的。

当开始重配置时,IPROG 指令由FPGA 内部的ICAPE2 模块发出,使FPGA 从Flash的指定地址开始读取配置文件,地址由重载起始地址(WBSTAR)寄存器决定。在IPROG 指令发出后,FPGA 依次进行三步操作:首先发送同步字(AA995566),然后向WBSTAR 寄存器中写入下一个比特流文件起始地址(00000000),最后发送IPROG命令(0000000F)。IPROG 指令序列如表1 所示。

表1 IPROG指令队列

3.4 Fallback逻辑设计

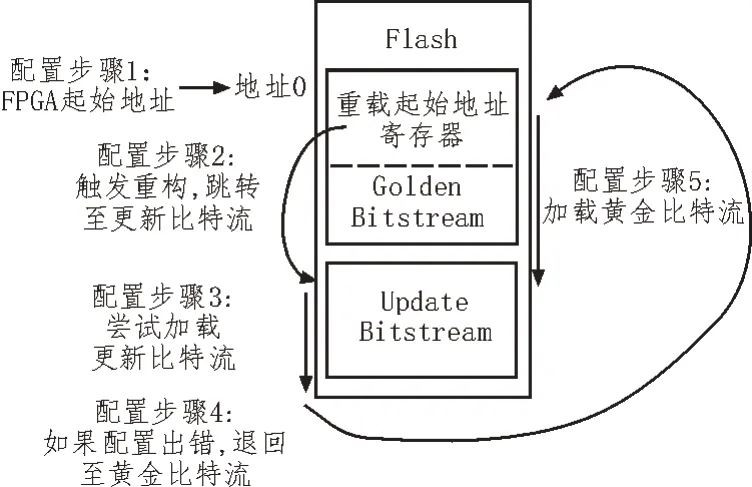

程序在线升级的过程中,如果遇到设备掉电等突发情况,重新上电之后,FPGA 根据触发引导逻辑从Flash 中加载程序,然而旧的程序已经擦除,而新的配置文件还未完全写入。导致设备无法再由1553B 接口接收下发的指令与相关配置文件,FPGA也失去了对Flash的控制。此时,唯一的解决办法就是打开产品外盖,通过USB-JTAG的方式把配置文件下载至Flash 中,给设备的升级造成了不便。为避免此类情况的发生,该设计通过触发Fallback的方式来进行解决,其配置逻辑如图6 所示。

图6 Fallback配置逻辑

在程序更新的过程中,一旦遇到突发情况,FPGA检测到配置出现错误,就会立刻进入到Fallback 模式,将FPGA 进行复位,然后从Flash的起始地址重新加载Golden Bitstream。Golden Bitstream 中包含原有的接口控制逻辑以及FPGA 对Flash的操作逻辑,这就使得FPGA 可以再次通过1553B 总线完成程序升级,保证了更新的可靠性。

有3 种情况会使FPGA 进入Fallback 配置模式,一种是在给定的时间内未检测到同步字AA99556;一种是检验到CRC 校验错误,CRC 校验指令存储在配置文件的尾部,FPGA 只有接收到CRC 校验指令才会进行校验,进而判断数据是否正确;最后一种便是看门狗计时器超时,看门狗会对配置过程进行监测,如果超时则会进入Fallback 模式。程序在线升级的过程中,若设备断电发生在程序擦除中,导致无法检测到同步字,则FPGA 会进入Fallback 模式重新加载Golden Bitstream。如果设备断电发生在写Flash 中,因为同步字在配置文件首部已经写入Flash,而CRC 校验指令在配置文件尾部还未写入,因此无法通过同步字及CRC 来判断校验是否出错。但是设备断电,看门狗计时器便会因FPGA 配置失败而超时,会触发FPGA 配置逻辑重新进入Fallback模式再次配置。通过这种方式,无论设备何时断电,都会触发Fallback 模式,保障了程序在线升级的可靠性。

4 测试结果及分析

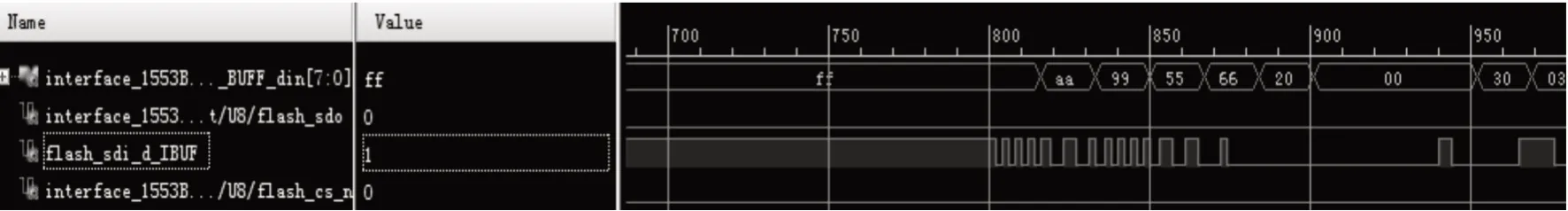

为了验证该设计的可靠性,把通过1553B 总线写入的程序读出,并由上位机软件显示,部分配置文件如图7 所示。再通过Vivado的集成逻辑分析仪ILA 抓取从Flash 中读取的配置文件,如图8 所示。通过对比,能够看到配置文件传输无误。

图7 部分配置文件

图8 正常读取的配置文件

为了对该设计的重配置进行验证,准备了3 个配置文件,其中一个为Golden Bitstream,其余两个为Update Bitstream。其功能为点亮不同的LED 灯,经验证无误,故重配置设计已实现。为了对Fallback模式进行验证,该设计通过ILA 分别抓取正常读出的配置文件、擦除过程中掉电读出的配置文件及写入程序过程中掉电读出的配置文件,分别如图8~10 所示,均与前述设计方案相符,且不论程序升级中设备何时断电,均可触发Fallback 模式,说明Fallback 配置模式已实现,证明了该设计的可靠性。

图9 擦除过程中断电读取的配置文件

图10 写入程序过程中断电读取的配置文件

5 结束语

该设计通过1553B 总线实现了对FPGA的在线升级,避免了特殊环境下无法完成程序更新,提高了程序更新方式的灵活性。同时通过控制Flash 完成了程序的分区擦除及分区写入,并且借助ICAPE2 模块完成了FPGA的多重配置,极大地提高了FPGA 可编程资源的利用率。而且Fallback 模式的配置,使得FPGA 即使在程序升级过程中掉电,也可以重新加载外部接口的控制逻辑和Flash的控制逻辑,再次通过1553B 接口完成在线升级,充分提高了固件更新的可靠性。