一种SDRAM控制器的设计电路

黄海生,党 成,李 鑫,叶小艳

(西安邮电大学 电子工程学院,陕西 西安 710121)

0 引言

以太网数据要通过E1线路传输就必须对以太网净荷数据进行帧封装,才能从E1线路上恢复出以太网数据帧,完成以太网数据的交换。使用HDLC协议进行以太网数据的二次封装,以太网数据在进行HDLC协议封装的传输过程中,不同数据链路进行数据交互时会出现亚稳态和数据吞吐量差异的问题。由于已有设计在以太网模块内部完成了跨时钟域的处理,因此本文提出的电路旨在解决跨时钟域数据通信时的吞吐量差异问题。这个问题的解决通常需要一个存储模块进行缓存,而SDRAM由于具有较高的读写速率和精度、存储容量大等优点,常用于数据缓存模块中,所以本文设计在利用SDRAM基本的缓存特性基础上,提出一种SDRAM控制器的新设计思路,运用模块化的设计方法,即双缓存模块IN_FIFO和OUT_FIFO的设计,将8 bit的输入数据转换为32 bit的数据进行读写处理,有效地提高数据的读写速率;同时增设CIR模块,通过设置CIR寄存器来控制以太网模块至HDLC模块发送的数据吞吐量,从而将SDRAM接收的以太网帧数据发送限制在设定的速率上。

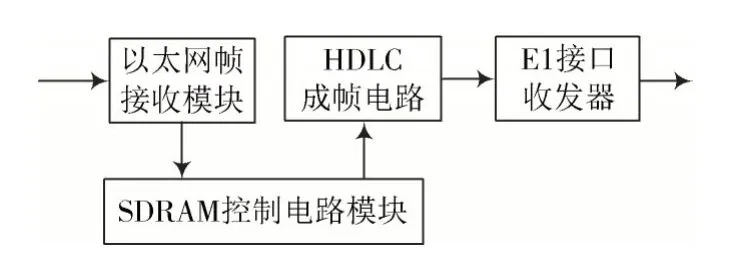

1 系统背景电路

图1所示为SDRAM控制器设计系统的背景框图。图中以太网帧接收模块将接收的数据进行一系列处理,在模块内部完成跨时钟域处理后将数据输出,与SDRAM模块以相同的时钟频率进行交互,由SDRAM将输出的数据送入HDLC成帧电路模块进行封装,得到HDLC帧数据后通过WAN接口发送,WAN接口能够与Dallas Semiconductor/Maxim的E1成帧器、线路接口单元(LIU)和单片收发器(SCT)进行无缝连接。本文提出的SDRAM控制器电路主要是为了使以太网帧和HDLC帧在完成速率同步后,能够正确地对SDRAM进行读写以实现数据缓存。

图1 SDRAM控制器设计系统背景框图

2 SDRAM控制器整体设计

SDRAM控制器整体设计架构如图2所示。首先,将数据写入读缓存IN_FIFO模块,IN_FIFO模块输出的读请求信号RD_REQ经仲裁模块SDRAM_ARB仲裁后,得到SDRAM的写指示信号WR_IND,并送入SDRAM控制模块SDRAM_CTL中,得到SDRAM的写使能信号(即IN_FIFO的读使能信号),并将其送回IN_FIFO模块控制数据的读取。将读出的数据送入SDRAM_CTL模块,在SDRAM写指示信号的控制下将数据通过总线SDATA送入SDRAM模块中进行处理,SDATA为inout类型。SDRAM输出的数据也通过SDATA总线进行传输。在OUT_FIFO写使能信号控制下将数据SDATA写入OUT_FIFO中,经OUT_FIFO读缓冲后输出。

图2 SDRAM控制器设计总体框图

另外,REG_PRO模块将数据队列的最大和最小地址提供给FIFO_CTL模块,进而产生读写地址。CIR_CTL用来控制SDRAM发送数据的吞吐量,将其输出的CIR_ACTIVE信号、OUT_FIFO输出的写请求信号WR_REQ以及FIFO_CTL输出的帧指示信号FRM_IND送入仲裁模块进行仲裁,将得到的读指示信号RD_IND送入SDRAM_CTL中,得到SDRAM的读使能信号(即OUT_FIFO的写使能信号)并发送给OUT_FIFO模块来控制数据SDATA的写入。

3 SDRAM控制器主要模块的设计

3.1 CIR_CTL模块

CIR用于将SDRAM接收的数据发送限制在设定的速率上,CIR寄存器控制数据的吞吐量。CIR寄存器在0~52 Mb/s范围内可设,间隔为500 Kb/s。本文设计中CIR_REG[7:0]值为8′h8F,最高位置1将使能约定信息速率控制器功能,CIR_REG[6:0]提供约定信息速率数值,该数值乘以500 Kb/s得到CIR值。若可用吞吐量为正,则输出CIR_ACTIVE信号送给SDRAM_ARB模块进行仲裁处理,从而控制SDRAM读指示信号的产生。CIR工作原理如下:

1)CIR模块对每125 ms结束时累积的可用吞吐量进行计数。

2)计算新的可用吞吐量,可用吞吐量=原有可用吞吐量-最近发送帧长度(以字节形式表示)。

3)可用吞吐量每125 ms递增CIR/8。

4)每250 ms可用吞吐量复位为CIR初始值。

5)CIR最大值不能超过发送线路速率。

6)对于接收并存储在SDRAM中的数据,向OUT_FIFO模块发送时要求可用吞吐量必须为正。如果可用吞吐量为负,则CIR_ACTIVE为0,将不进行数据传送。

3.2 IN_FIFO与OUT_FIFO模块

在数据高速传输的情况下,应加入缓存器FIFO对SDRAM写入和读出数据进行缓冲,确保数据传输的稳定性和一致性,防止数据失真。本文设计采用双FIFO缓冲设计,即读缓存和写缓存,其中写缓存IN_FIFO模块将其输入的8 bit位宽的以太网帧数据转换为32 bit位宽的数据输出,对32 bit数据的处理有效地提高了SDRAM的读写速率;读缓存OUT_FIFO模块将读出的数据转换为8 bit的数据输出,确保数据输入与输出的一致性。

3.3 SDRAM_ARB模块

仲裁模块管理以太网端口与HDLC端口之间数据的传输请求,管理SDRAM中数据的输入与输出。对IN_FIFO输出的读请求信号进行仲裁,将得到的SDRAM写指示信号发送给SDRAM_CTL模块处理,最终得到FIFO的读使能与SDRAM的写使能。对CIR_CTL输出的CIR_ACTIVE、OUT_FIFO输出的写请求信号WR_REQ、FIFO_CTL输出的帧指示信号FRM_IND进行仲裁,得到SDRAM的读指示信号RD_IND并送入SDRAM_CTL中,最终得到FIFO的写使能与SDRAM的读使能信号。

3.4 SDRAM模块

SDRAM采用MICRON公司的MT48LC4M32B2型号,时钟为100 MHz,SDRAM容量为128 MB,数据位宽为32 bit。SDRAM的工作原理如下:

1)初始化

开机后,SDRAM需要先对逻辑控制单元进行初始化操作(包括所有L-Bank预充电、刷新、设置模式寄存器)。其中,模式寄存器的设置需通过地址线来控制,在本文中突发长度为1,CAS潜伏期CL=2,突发类型选择为顺序。在模式寄存器设置结束后,可以对SDRAM进行数据读写。

2)读写操作

对一个L-Bank中的阵列进行寻址时,首先需要确定行,其次确定列。片选和L-Bank的定址可以与行有效同时进行。文中有12个地址线A0~A11,共4096行,在SDARM控制命令为激活(act)时,L-Bank根据bank地址的不同进行定址,且具体的行地址可由地址线的不同来选择确定。列寻址信号与读写命令是同时发出的。在SDARM的控制命令为读(read)或写(write)时,具体的列地址由地址线A0~A7来决定。在确定列地址之后可找到具体的存储单元,接着可将数据通过I/O通道(DQ)输出到内存总线上。当SDRAM处于突发写操作状态时,数据由DQ总线进入模块;当SDRAM处于突发读操作状态时,数据由DQ总线输出。由于CL为2,因此在进行数据读操作时,从CAS与读命令发出后需要经过2个时钟周期才会有数据输出,并且CL只作用于数据读取时。

3)刷新操作

刷新操作须在64 ms内被执行4096次,可选择周期执行,也可突发执行。本文选择周期性刷新,即每15625 ns内必须执行一次刷新操作,由于系统时钟为100 MHz,周期为10 ns,所以每1562个时钟周期内必须刷新一次,本文选择每17页刷新一次,1页为30个时钟周期。SDRAM控制命令如表1所示。

表1 SDRAM控制命令表

3.5 SDRAM_CTL模块

SDRAM_CTL中各模块分布情况如图3所示。

图3中各模块具体功能如下:

图3 SDRAM_CTL中各模块简单的分布图

1)SDRAM_NORM_INI模块。上电后在SDRAM操作时钟的作用下,通过计数得到SDRAM初始化的指示信号。

2)SDRAM_CMD_PRO模块。该模块在对输入指令进行分析判断后,产生相应的CS、RAS、CAS、WE等信号,从而形成对SDRAM的控制指令。

3)SDRAM_ADDR_PRO模块。在SDRAM初始化指示信号、刷新指示信号、读写指示信号、数据长度指示信号的作用下,将外部发来的地址译码为SDRAM所需要的bank地址和row/col地址命令。

4)SDRAM_DATA_PRO模块。主要在数据写操作时将数据发送到SDATA总线上,数据由输入总线进入SDRAM模块中。

4 SDRAM控制器设计仿真

本文采用Verilog硬件描述语言对电路进行描述,在ModelSim上对该电路进行功能仿真。系统复位结束后,在时钟的作用下将数据写入IN_FIFO缓冲区,由仲裁器负责将IN_FIFO中的数据导入SDRAM中。在CIR的作用下,仲裁器将SDRAM中的数据写入OUT_FIFO缓冲区,最后将OUT_FIFO中的数据读出,观察系统写入与读出数据是否一致。IN_FIFO模块写入的数据波形与OUT_FIFO模块读出的数据波形分别如图4、图5所示。

图4 IN_FIFO模块写入数据的波形

图5 OUT_FIFO模块读出数据的波形

由图4、图5仿真结果表明,OUT_FIFO模块读出的数据与IN_FIFO模块写入的数据一致(其中,OUT_FIFO模块读开始信号所对应的读数据为该帧数据的长度16′h7a)。

5 结 语

本文提出一种SDRAM控制器的设计电路,并使用Verilog HDL对该电路进行了描述。经仿真验证,在满足CIR功能的条件下,OUT_FIFO模块读出的数据与IN_FIFO模块写入的数据始终保持一致,说明了本文设计的正确性。本文电路设计简单,对于以太网映射器的研究有着重要的意义,可广泛地用于不同链路的数据通信中。