基于国产化通用VPX的信号处理板设计

王锡志

摘要:针对当前国家信息化设备的快速发展和国产化的不断推进,结合当前国产芯片发展现状。结合VPX总线架构发展现状,通过开展高速总线互联技术的研究,将二者结合。以国产芯片为基础,完成了基于国产化通用VPX信号处理板的设计。对各功能电路进行了详细阐述,并对主要国产芯片系统进行了介绍。通过硬件平台的开发,在自主化硬件设计、软件适配及VPX总线架构等方面积累经验,为装备实现国产化国产化提供技术支撑。

关键词:国产化;VPX;DSP;FPGA

中图分类号:TN919.3文献标志码:A文章编号:1008-1739(2022)01-52-4

0引言

在我国信息设备建设国产化持续推进下,在提倡创新和自主发展的大背景下,为了行业长远和健康发展,必须在芯片领域坚持自主研发和应用[1]。

随着通信对抗专业领域的技术发展,作战目标多样化、应用场景多元化。对多信号、多功能并行处理能力的设备需求逐步增多,对宽带高速处理与窄带高精度处理的需求在逐步增多,传统的并行总线已不能满足设备需求。VPX总线作为新一代的高速串行总线,采用了高速串行Rapid IO、PCIe等高性能接口,更加适应现代通信对抗领域对功能繁多、运算复杂、数据量大及高速实时处理的要求[2]。

本文结合目前国产化元器件现状和技术发展需求,对国产化元器件和VPX架构的应用进行研究和探索,设计了一款基于国产芯片的VPX架构信号处理板,详细说明各个功能模块的设计与实现,在自主化硬件设计及VPX总线架构等方面积累经验,为国产化国产化提供技术支撑。

1设计原理

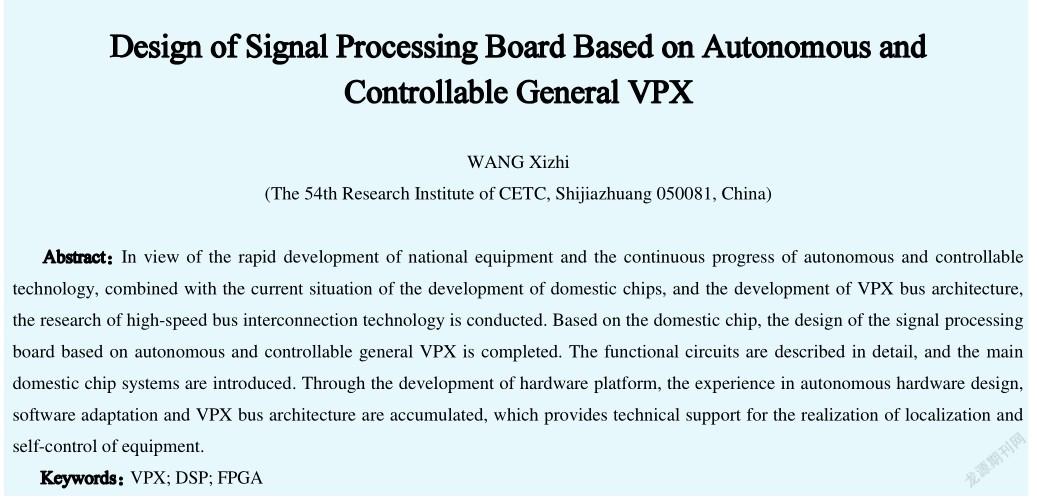

信号处理板采用VPX总线标准的6U尺寸设计,符合Vita46/Vita48规范,采用DSP+FPGA+FMC架构。按照功能设计将接口划分为管理平面、数据平面、扩展平面、控制平面和自定义平面。板卡融合了IPMC管理、SIRO交换、高速串行总线、通用多核DSP和FPGA等。管理平面用于板卡硬件信息的管理和监控,采用双I2C的IPMB总线实现。数据平面支持模块间高速数据传输,采用4x SRIO接口作为数据总线,支持主/备模块间互连。扩展平面为相邻2个处理模块提供收发双向8个通道端口互连。控制平面要求高可靠性,采用SGMII接口作为控制总线,支持1000Base-T。自定义平面用于外部物理接口,可接射频电缆和光纤等。硬件原理如图1所示。

2硬件实现

2.1 IPMC设计

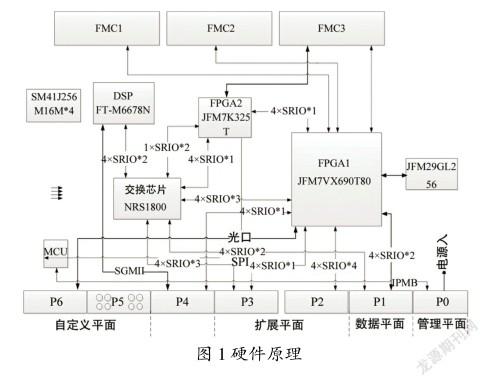

IPMC电路图如图2所示[3]。IPMC主控芯片由兆易创新的GD32F450VKT6来实现。该芯片是一款国产MCU处理器,时钟主频200 MHz,芯片内集成了3 072 Kbytes的片上闪存和512 Kbytes的SRAM内存,同时提供12通道ADC。通过两路I2C总线与背板的IPMB_A,IPMB_B连接。IPMC电路采用独立的+3.3 V_AUX供电。MCU可以实现板卡上电、重启、电压检测、功能自检及故障信息上报等功能。

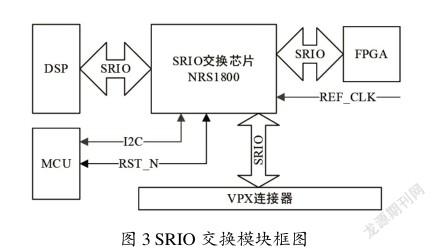

2.2 SRIO交换模块设计

SRIO交换芯片选用的NRS1800,该芯片具有48个双向的数据差分对(Lane),可以配置成1x,2x,4x三种端口模式,最多可以配置成18个1x或12个4x端口,每个lane的速率可选择1.25 Gbit/s,2.5 Gbit/s,3.125Gbit/s,5 Gbit/s,6.25 Gbit/s。NRS1800还有一个标准I2C接口,该接口可以用来完成对芯片的初始化配置,也可以通过I2C读取NRS1800内部寄存器来获取芯片的工作状态。NRS1800可应用于大型处理器集群或背板,支持多种SRIO网络拓扑结构,可以采用灵活的方式进行配置,可选的配置方案也非常丰富。SRIO交换模块如图3所示。

NRS1800的复位引脚RST_N用于全局復位,使所有寄存器恢复到上电默认状态,该引脚接入MCU芯片。RST_N信号需要低电平持续最少5个REF_CLK周期,复位完成后可通过I2C/JTAG对芯片进行配置。

NRS1800的I2C接口符合I2C协议规范,芯片可以作为从设备和临时主设备。MM_N引脚决定上电复位后I2C接口是主模式还是从模式。连接到GND为临时主模式,上拉至3.3 V为从模式。ADS引脚决定从模式下I2C设备地址宽度,连接到3.3 V为10 bit地址,连接到GND为7 bit地址。ID9~ID0引脚为I2C从模式下地址信号。

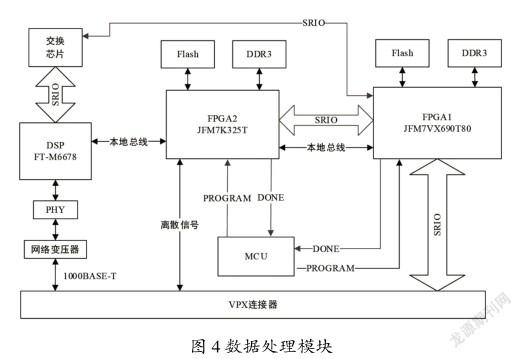

2.3数据处理模块设计

数据处理模块主要由FPGA和DSP组成,组成如图4所示。

FPGA选取复旦微电子7系列JFM7K325T和JFM7VX690T80。2款FPGA沿袭了Xilinx发展路线,如配置方法、时钟接口、电源的接法与Xilinx对应产品完全一致。JFM7K325T主要用来完成本地总线转换、离散信号控制以系统中各模块间I/O时序控制,可用于对另一片FPGA的程序在线更新,实现功能重构技术。JFM7VX690T80实现数据串并转换以及对AD采集的中频信号进行数字下变频、FFT等处理功能。外接DDR3存储器实现数据缓存。FPGA的控制引脚接入MCU芯片,可配置程序从Flash中重新加载。国产FPGA资源列表如表1所示。

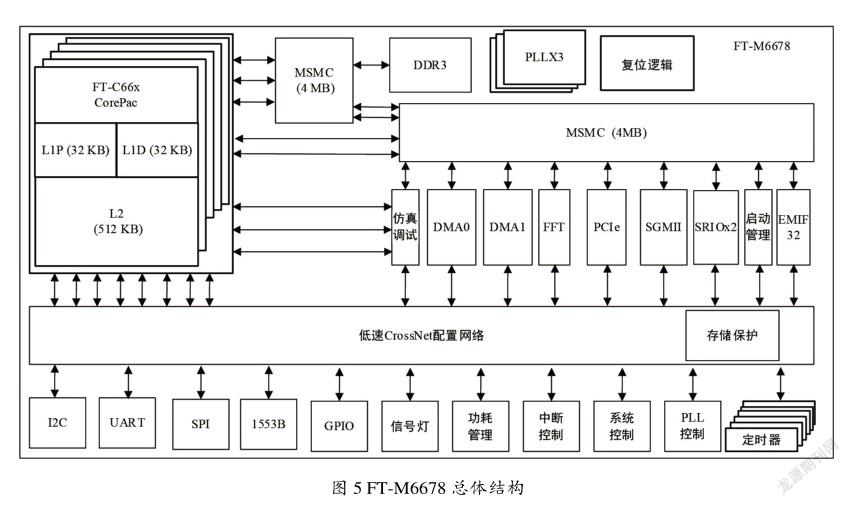

DSP芯片选取FT-M6678,该款芯片是一款高性能浮点/定点数字信号处理器,可满足多种实时信号处理的需要。含有8颗FT-M66x DSP内核,每个内核工作主频为1 GHz。定点运算性能为32 GMACs,浮点运算性能为16 GMACs。有2组SIRO串行总线,每组可配置成1x,2x,4x模式,每Lane传输速率支持1.25 Gbit/s,2.5 Gbit/s,3.125 Gbit/s。除此之外,FT-M6678还有一个SGMII以太网接口,支持支持1000Mbps、100 Mbps,10 Mbps传输。可外接64位DDR3存储器,最大寻址空间8 GB。FT-M6678总体结构如图5所示。

2.4时钟模块设计

信号处理板上用到的时钟非常多,而且频率各不相同,有差分时钟和单端时钟。时钟设计的目标就是用最简单的方案实现板卡上所有器件的时钟需求,以减少电路面积,增加可靠性。本设计选取了1片AD9523时钟芯片,该芯片可以通过编程,由MCU控制,产生信号处理板上所需要的时钟。时钟产生如图6所示。

2.5电源模块设计

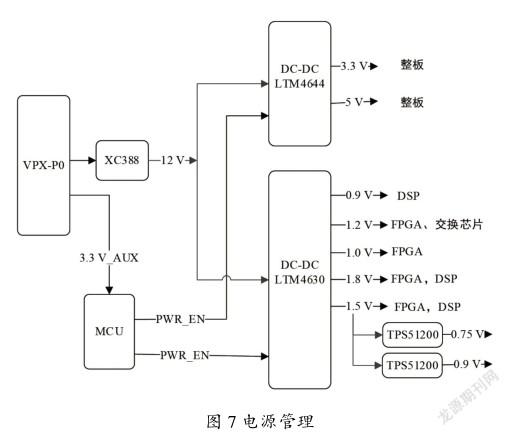

由于信号处理板高速信号线多、系统较复杂,集成了大规模交换芯片、FPGA器件、DSP器件、DDR存储器以及各种接口电路。对电源的输出纹波、转换效率、电压精度、上电顺序以及电源完整性提出更高的要求。VPX接口提供直流12 V和3.3 V。其中3.3 V直接供给MCU芯片,用来对电源模块的上电时序控制。12 V经过电流保护芯片XC388QDC输入DC/DC模块,该芯片最大浪涌电压可达到60 V,通过电阻可以调节输入保护电压。DC/DC电源模块选取LTM4644,LTM4630,2款电源为BGA封装,具有体积小、效率高、易于散热等特点。电源管理如图7所示。

3软件设计

信号处理板的软件包括DSP,FPGA,MCU嵌入式软件。FT-M6678主要用来实现复杂的浮点信号处理,如信号分析与解调、信号侧向、常规信号测量与信号截获等功能。例如,用一片DSP芯片完成7路4 Msps的16QAM信号的解调,或者一路40 Msps的16QAM信号的解调等。在8个核的功能分配上,核0一般用于完成芯片的初始化,解析系统发过来的指令以及控制SRIO收发数据等,其他7个核协同完成信号处理的算法[4]。

模块中的FPGA主要完成系统中各模块间I/O时序控制、数据缓存、数据串并转换以及对AD采集的中频信号进行数字下变频,FFT等预处理的功能。

MCU由VPX的专用电源供电,完成对交换芯片NRS1800的初始配置,完成上电后的系统自检功能,利用其片内AD采集板子上的各种电压值。MCU通过I2C总线与监控模块进行数据交换,实现IPMC管理。

4关键技术

考虑到大部分的差分信号都工作在千兆赫兹,因此,需要采取必要的措施来保证信号的完整性和电磁性,使用MENTOR公司的Hyperlynx仿真软件对关键信号线进行了仿真分析。对交换模块PCB上的高速信号线进行了仿真分析,使每对差分线阻抗保持100Ω,同一个端口内的各差分线之间的信号传输偏移时间小于11 ns,差分线之间没有大的串扰,从而保证了信号的高质量要求[5]。

时钟是整个板卡的工作中枢神经,各个功能单元的有机协调工作都由其来驱动激发[6]。本板采用高性能时钟芯片AD9523,配以高精度的VCXO来输出所需的各种时钟。整个处理板内的所有模块时钟同源,可以改善信号的完整性,使整个板卡工作的性能更高更稳定。

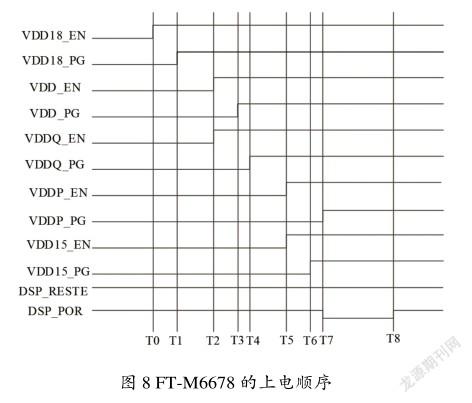

电源是给电子电路提供能量的重要电路组成部分,其电参数的精度和效率直接影响电路的正常工作[7]。本设计中主要以SM4644和SM4630大功率多路输出电源为主,SM74401和SM51200底纹波线性电源为辅的设计方法。芯片的上电时序由MCU控制。交换芯片NRS1800上电时序为3.3 V上电,然后1.2 V再上电,上电间隔要大于10 ms。FT-M6678除了有高速的处理单元,还集成了丰富的片上外设接口。这些接口,有些需要独立的电源,有的接口之间要求特定的上电顺序。FT-M6678的上电顺序如图8所示。

5结束语

在目前的国际形式下,芯片国产化势在必行,且VPX总线架构作为行业内主流的平台,具有模块化、通用化、扩展性、开放性和高可靠等特点。本文设计国产化信号处理板,具有較强的通用性,非常适用在通信侦对抗等领域。通过该板的研制,为高速总线互联设计及国产芯片设计提供非常好的技术借鉴。

参考文献

[1]于东英,陈俊,康令州.基于国产FPGA的高速SRIO接口设计与实现[J].通信技术,2019,52(1):255-258.

[2]肖希,张雄林.基于VPX架构的高速信号板设计[J].兵工自动化,2017,36(12):34-38.

[3]朱红育,李郁,付学斌.IPMI在VPX系统中的应用与设计[J].火控雷达技术,2013,42(4):65-69.

[4]马友科,吴冰.基于多核DSP的通用信号处理板设计[J].无线电工程,2014,44(9):56-59.

[5]齐青茂,冯鹤,马友科.基于Hyperlynx的高速数据传输板SI研究[J].计算机与网络,2012,38(14):47-49.

[6]白月胜,曹淑玉.基于AD9517的高速采样时钟设计[J].工业技术创新,2014,1(4):460-464.

[7]屈召贵,周永强.高精度DC-DC电源设计[J].微型机与应用, 2017,36(17):34-37.