基于FPGA的面阵CCD光谱采集系统设计

陈 瀚,黄 斐,薛 萌,朱亮庆,郭汉明

(上海理工大学光电信息与计算机工程学院,上海 200093)

0 引言

近年来,拉曼光谱技术已成为重要的分子分析方法,在生物学、化学、医学、材料工程、药品及危化品鉴别、文物鉴定等领域,都显现出广阔的应用前景。传统拉曼光谱分析仪器往往造价昂贵、体积庞大、难以携带,且关键技术主要掌握在少数发达国家手中,国内单位研制的产品在技术指标上与进口设备仍有差距。因此,国内急需开发一款体积小巧、集成度高,能够进行现场快速检测的便携式拉曼光谱仪。

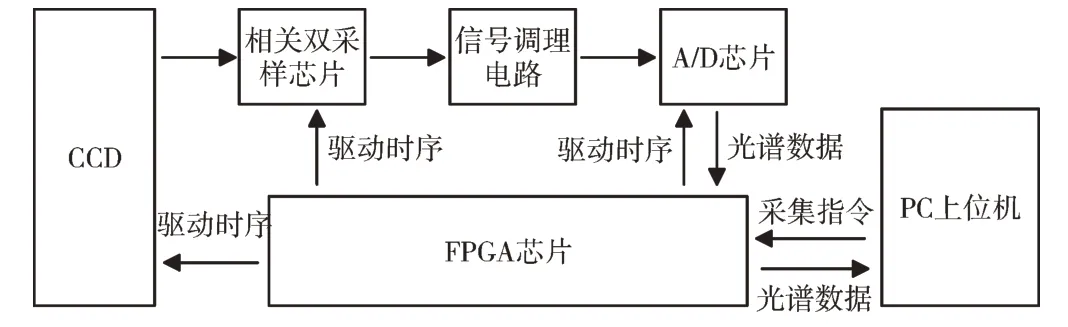

光谱采集系统作为拉曼光谱仪的核心模块,其技术指标对拉曼光谱仪的整体性能有着至关重要的影响。为此,本文设计一款基于面阵CCD的光谱采集系统[1]。系统以Altera FPGA 芯片为控制核心,用来产生CCD的驱动时序,以及相关双采样芯片和模数转换芯片的控制时序,对光谱数据进行存储与传输[2]。本系统充分利用了FPGA 高速并行且可编程的特点,简化了硬件设计的复杂程度,不仅能实现对CCD 信号的高速采集,而且成本大幅降低。

在实验测试中发现,随着CCD 积分时间的增加及环境温度的升高,CCD 输出信号中的暗噪声会随之变大,导致光谱曲线出现基线漂移现象,严重影响拉曼光谱仪探测的动态范围,同时会对后续光谱分析算法的准确性造成很大影响。由于各种现实因素,很少有文献公开报道如何在不使用制冷型CCD 和各种制冷设备的低成本条件下,有效控制CCD 暗噪声引起的基线漂移。为抑制CCD 暗噪声并对基线漂移进行控制,本文在采用相关双采样技术减小CCD输出信号中复位噪声的基础上,设计一种信号补偿电路,采用分立的相关双采样芯片和A/D 芯片,并在两者中间加入信号调理电路,对CCD 输出的模拟信号进行补偿,同时在FPGA 控制程序中设计了CCD 残留电荷自动清空功能。这些措施有效解决了与积分时间和环境温度有关的暗噪声导致的光谱基线漂移问题,保证了光谱采集系统的稳定运行。

1 系统总体设计

电荷耦合器件(Charge-Coupled Device,CCD)是一种灵敏度很高的光电探测器,具有体积小、响应速度快、动态范围大等优点[3]。本设计采用背照式CCD,相比于前照式CCD,背照式CCD的像元前方无任何遮挡,避免了入射信号的吸收损失。以这种方式入射的CCD 整体量子效率较高,峰值量子效率可达80% 以上,非常适用于探测微弱拉曼光谱信号[4]。

由于面阵CCD 需要多路驱动信号,且驱动信号时序比较复杂,同时其输出信号为相关信号,需要进行相关双采样,因此本系统的设计重点在于CCD 驱动设计以及对CCD输出信号的采样、调理与模数转换。

对于CCD 输出的相关信号,可采用带有相关双采样功能的A/D 芯片,这种芯片可直接对CCD 输出信号进行采样,硬件电路比较简单,适用于积分时间变化范围较小的CCD 应用[5]。但在拉曼光谱仪中,积分时间需要根据不同样品进行调节,对于拉曼散射特别微弱的样品,积分时间甚至需要几秒钟。此时拉曼信号的基线会出现比较明显的漂移,如果选用自带相关双采样功能的A/D 芯片,想要对基线进行外部补偿很困难[6]。

为实现对基线进行补偿,本系统采用独立的相关双采样芯片和A/D 芯片。优点是灵活性更好,可在相关双采样芯片与A/D 芯片之间增加信号调理电路,不仅可实现对基线进行外部补偿,而且能够对信号进行放大,同时增益系数可调[7]。

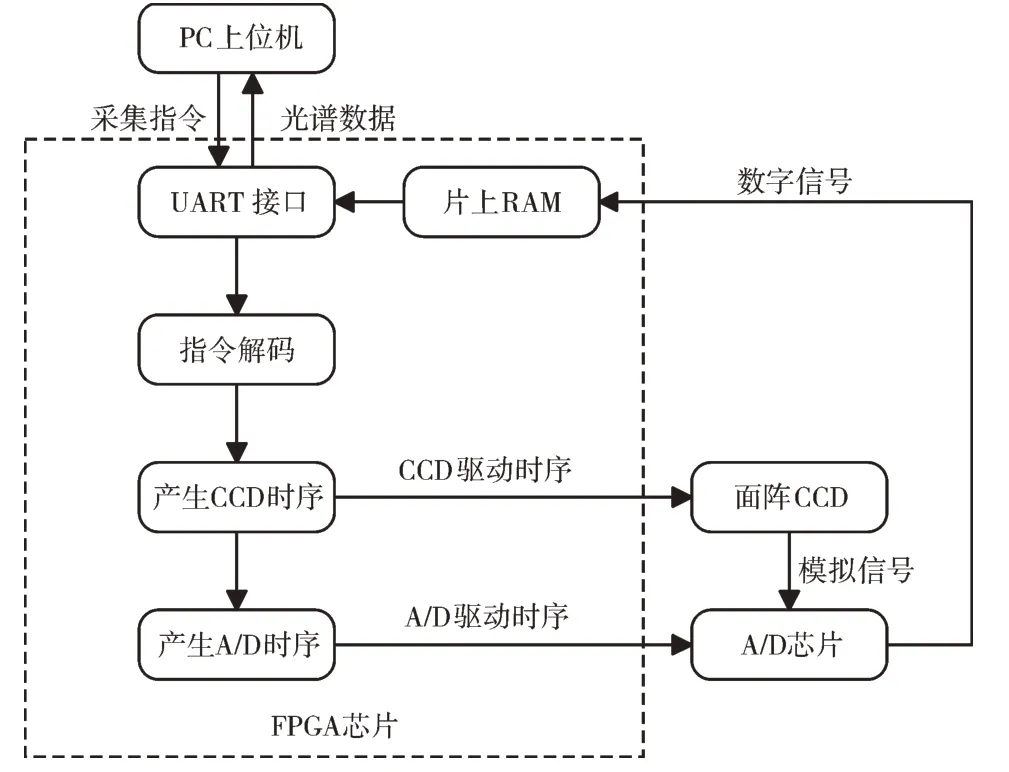

该系统在工作时,CCD 将入射的光信号转换为模拟电信号,通过相关双采样电路、信号调理电路和A/D 转换电路,利用相关双采样原理对CCD 输出的模拟信号进行采样,此方法能够较好地滤除复位噪声。之后光谱数据通过FPGA 串口传至PC 上位机,最终在上位机软件中生成光谱强度分布曲线[8]。该系统结构框图如图1 所示,其中箭头表示CCD 信号和光谱数据传输方向。

Fig.1 Structure block diagram of spectrum acquisition system图1 光谱采集系统结构框图

2 CCD 驱动设计

该光谱采集系统采用Hamamatsu 公司的S11510-1106型CCD,其包含2 048列×64行,共计131 072个有效像素[9]。

根据该型CCD的数据手册,要驱动CCD 正常工作,需要多种电压和多路时序信号。因此,所需的供电电源种类较多,如水平和垂直驱动信号所需的+6V、-5V 和-8V 电源,溢出门需要的+12V 电源,输出门需要的+5V 电源,输出晶体管漏极需要的+24V 电源等[10]。该系统使用蓄电池供电,其额定输出电压为+8.4V,CCD 所需电压使用电源转换芯片由+8.4V 转换得到[11]。

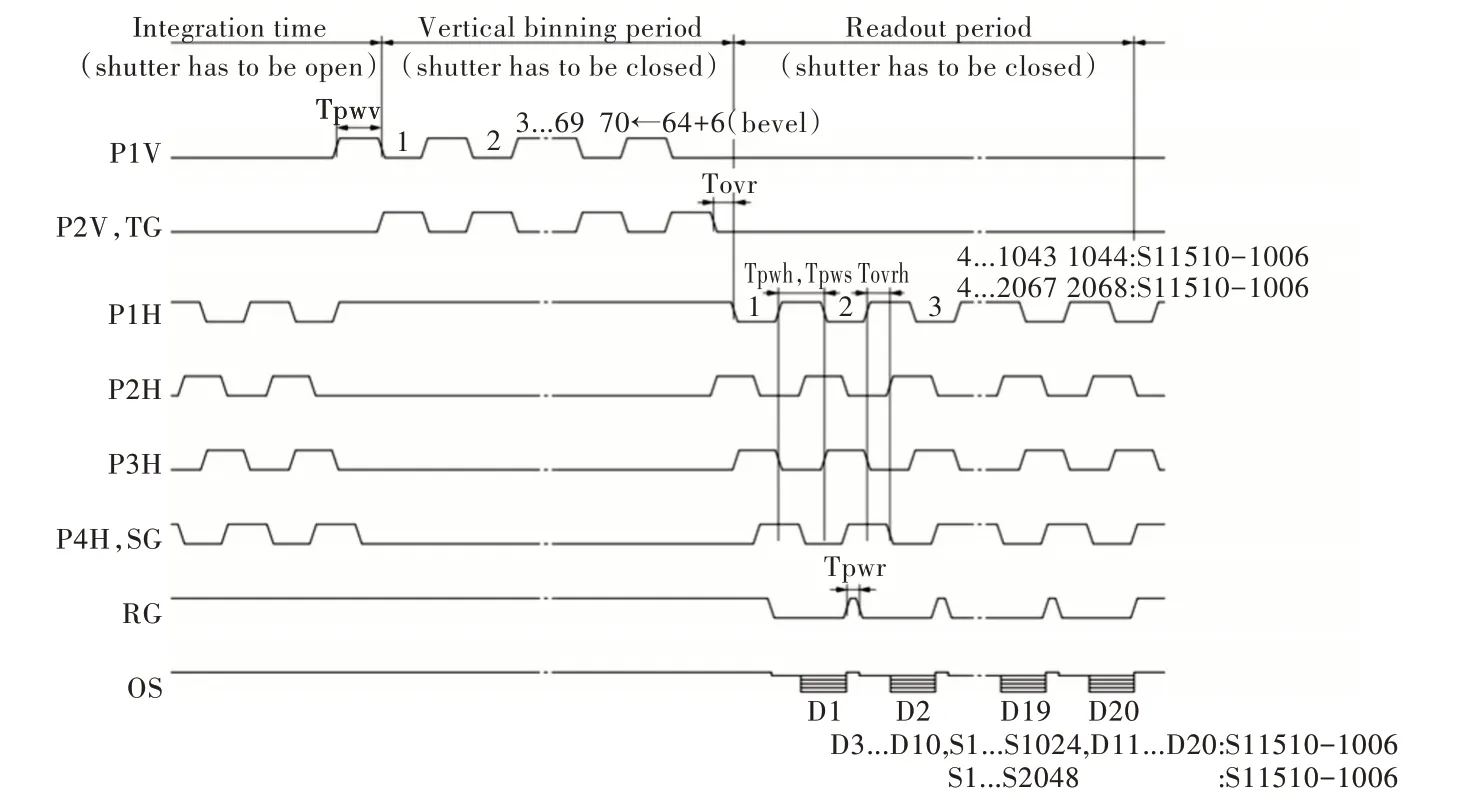

对于该型CCD,共需要七路时序驱动信号,其中包括两路垂直驱动信号P1V 和P2V&TG,四路水平驱动信号P1H、P2H、P3H 和P4H&SG,以及一路复位信号RG。具体时序如图2 所示。

CCD 一次完整的工作过程分为积分时间、垂直装箱周期和读出周期3 个阶段:

(1)积分时间。在四路水平信号(P1H、P2H、P3H、P4H&SG)和一路垂直信号(P1V)的驱动下,CCD 对入射光进行曝光,同时进行光电转换产生电荷,曝光时长称为积分时间。

(2)垂直装箱周期。在垂直信号(P1V,P2V&TG)的驱动下,对CCD 内部的每一列像素分别进行垂直装箱操作,将每一列64 个像素中存储的电荷全部转移到该列像素对应的水平移位寄存器中,等待水平转移输出。

(3)读出周期。在四路水平信号和复位信号(P1H、P2H、P3H、P4H&SG、RG)的驱动下,CCD 将已垂直装箱的2 048 个电荷包依次转移输出,形成CCD 输出信号。

Fig.2 Driving signal timing of S11510-1106 CCD图2 S11510-1106 型CCD 驱动信号时序

该系统在工作时,首先会通过上位机给FPGA 发送CCD 使能指令,FPGA 收到该指令后开始给CCD 发送时序驱动信号,CCD 便开始工作。CCD 会依次执行以上3 个工作周期并且不断循环执行,可将CCD 中产生的电荷不断输出。此时,A/D 电路不会对CCD 输出的信号进行采集。CCD的这种工作模式称为“清空模式”,其作用是在进行正式的光谱采集前,将CCD 中残留的电荷全部清空,因而不会对后面的光谱采集造成干扰[12]。

当需要采集光谱信号时,上位机会给FPGA 发送光谱采集指令,并且可设定积分时间的时长。之后FPGA 会根据设定的时长给CCD 发送时序驱动信号,并给相关双采样芯片和A/D 芯片发送控制时序,以实现光谱采集。在一般情况下,当FPGA 接收到上位机的光谱采集指令时,CCD的工作状态很可能还处在3 个工作周期中的某一个,此时FPGA 会让CCD 将当前的3 个工作周期执行完毕,使CCD 内部电荷被清空,然后再按照上位机设定的积分时间进行正式的光谱采集。完成光谱采集操作后,FPGA 会使CCD 重新进入“清空模式”,再等待下一次的光谱采集指令。

3 信号采集电路设计

3.1 相关双采样电路

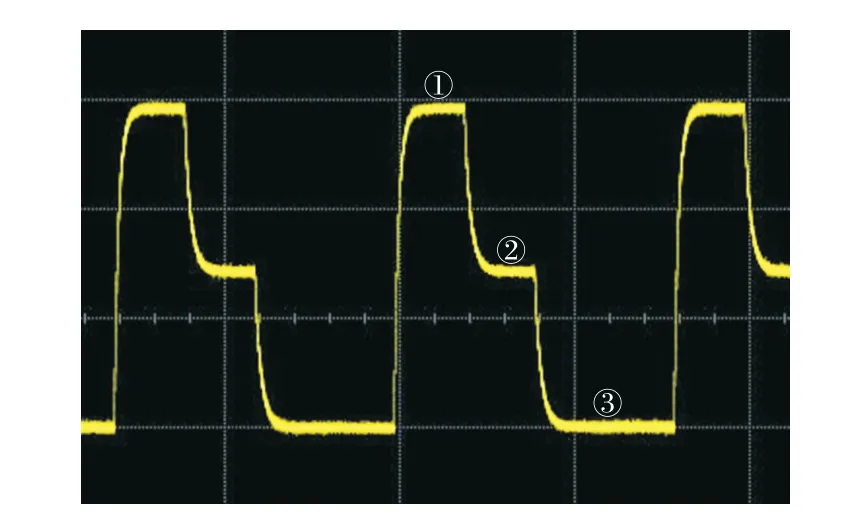

CCD 完成一次光谱采集过程后,会将每一列像素产生的电荷依次输出,输出信号为相关信号,呈阶梯状,如图3所示。其中,阶梯①为复位缓冲电平,阶梯②为复位电平,阶梯③为信号电平[13]。阶梯②与阶梯③之间的电压差值大小与该列像素接收到的光信号强弱直接相关,表达式为:

其中,Vs2为阶梯②的稳定电压,Vs3为阶梯③的稳定电压,Vsignal表示有效信号大小,这两个阶梯电压中都含有相同的复位噪声,因此这种信号被称为相关信号。分别对这两个电压进行采样,然后将两者相减即可抵消复位噪声,得到CCD的有效输出信号,这便是相关双采样法(Correlated Double Sample,简称CDS)[14]。

Fig.3 Waveform of CCD output signal图3 CCD 输出信号波形

根据相关双采样法,本设计采用相关双采样芯片(Correlated Double Sampler,CDS)AD9823 和模数转换芯片(Analog to Digital Converter,A/D)ADS8381 相配合对CCD 信号进行采集。AD9823 是ADI 公司生产的相关双采样芯片,其最大采样频率为40MHz,而CCD的输出信号频率为62.5kHz,因此完全可以满足应用要求。

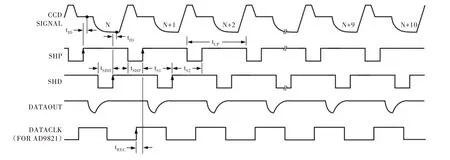

根据相关双采样原理,AD9823 在每个像素周期内对阶梯信号进行两次采样。采样时钟信号分别为SHP 和SHD,其中在SHP 信号的上升沿对复位电平进行采样,在SHD 信号的上升沿对信号电平进行采样。SHP 和SHD的时序波形如图4 所示。其中,CCD SIGNAL 表示CCD的输出信号,DATACLK 表示A/D 芯片的转换时钟。在DATACLK的上升沿,A/D 芯片开始对模拟信号进行转换。

AD9823 对一个像素周期的阶梯信号进行相关双采样后,会同时输出两个电压信号REFOUT 和DATAOUT。其中,REFOUT是参考电压信号,其是一个固定值,大小为+0.5V;DATAOUT 是数据电压信号,典型范围为0.5~1.5V。用DATAOUT 减去REFOUT,即为CCD 信号的有效值。

3.2 信号调理电路

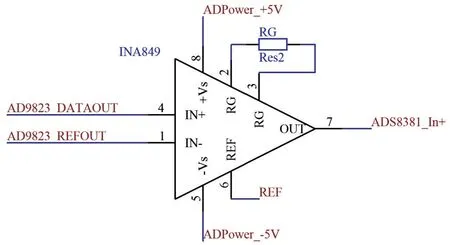

在AD9823 与A/D 芯片之间的信号调理电路要对DATAOUT 和REFOUT 两个信号作差分处理,以得到CCD输出信号的有效值[15]。同时,由于该信号有效值的幅值较小,典型幅值范围为0~1V,而A/D 芯片的输入信号量程较大。为使两者尽可能接近,要求信号调理电路能够对信号进行放大,且增益系数可精确调节,另外还能对CCD 有效信号的基线进行调节,以更好地消除背景噪声干扰[16]。综合以上要求,本设计选用仪表放大器芯片INA849 对信号进行调理。

Fig.4 Timing waveform of AD9823 sampling clock signals图4 AD9823 采样时钟信号时序波形

INA849 是一款超低噪声仪表放大器,具有很小的电压噪声、输入偏移电压和偏移电压漂移。其输入阻抗很大,可达1GΩ,同时输出阻抗很小,开环输出阻抗仅为10Ω。其电路原理如图5所示,其中IN+和IN-是差分信号输入引脚。

Fig.5 Circuit scheme diagram of INA849图5 INA849 电路原理

INA849 可通过一个外部电阻器精确地调节信号增益系数,其计算公式为:

其中,G为信号增益系数,RG为外部电阻器阻值。REF是参考电压输入引脚,REF 电压可调节输出信号的基线。

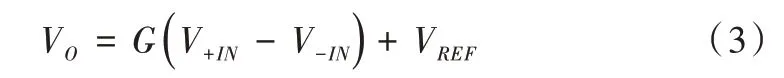

综上,输出信号计算公式为:

其中,VO是INA849 输出电压,V+IN和V-IN是差分输入信号,VREF是输入参考电压。

接下来,在经过信号调理电路之后,CCD 信号进入A/D芯片ADS8381。

3.3 模数转换电路

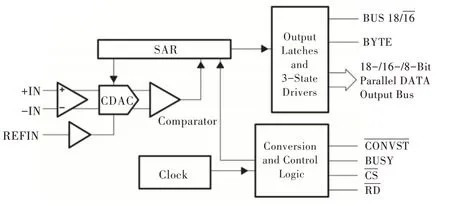

ADS8381 模数转换芯片的最大采样率为580kHz,而CCD 输出信号的频率为62.5kHz,因此完全可满足要求。ADS8381 具有18 位分辨率,能够以二进制格式输出全并行数据。其内部电路结构如图6 所示。

Fig.6 Internal circuit structure of ADS8381图6 ADS8381 内部电路结构

在图6 中,+IN 和-IN 为模拟信号输入端口,根据数据手册,-IN 端的输入电压范围为-0.2~+0.2V,+IN 端的输入电压范围与外部参考电压VREFIN有关,大小为-0.2~VREFIN+0.2V。在本设计中,信号调理电路输出的是单端信号,因此直接将-IN 端连接到GND,+IN 端接入信号调理电路的输出信号。

ADS8381 工作时需要一个外部参考电压,电压范围为2.5~4.2V。REFIN 端口为外部参考电压输入端口,+IN端输入的信号电压必须小于参考电压VREFIN,否则会出现量程饱和现象,损失数字精度[17]。在本设计中选用REF3125参考电压芯片,其可提供2.5V的稳定参考电压。因此,要合理调节信号调理电路的放大倍数和外部参考电压,使进入到ADS8381的模拟信号既不要超过0~2.5V的量程范围,又要尽量占满此范围[18]。

ADS8381工作过程主要由CONVST、CS、RD、BUS、BYTE 5 个信号控制。其中,BUS、BYTE 两个信号用来切换数字信号的输出方式。通过切换这两个信号的组合状态,可分别实现用18 个端口、16 个端口或8 个端口输出18 位二进制数据。

CONVST、CS、RD 3 个信号用来控制模拟信号转换以及数字信号读取,控制方式比较灵活,开发者可根据自己的习惯和实际需要选择不同控制方式。由于当ADS8381对模拟信号进行转换以及输出数字信号时,CS 信号都必须处于低电平状态,因此在本设计中,选择直接将CS 信号置低,使其一直有效。

当CONVST 信号出现下降沿时,ADS8381 会开始对输入信号进行转换。CONVST 信号的下降沿应与AD9823 时序图中DATACLK 信号的上升沿对齐。

当RD 为高电平时,并行输出端口会被置位高阻态。当RD 信号出现低电平时,并行输出端口即会输出数据。当FPGA 接收到ADS8381 输出的数据后,会先进行缓存,然后通过UART 接口(Universal Asynchronous Receiver/Transmitter)将数据发送给上位机。

4 FPGA 程序设计

现场可编程门阵列(Field Programmable Gate Array,FPGA)是一种数字集成电路,开发者可通过硬件描述语言将FPGA 芯片设计成具有特定逻辑功能的数字系统,并且可对其逻辑功能进行反复修改,调试非常方便[19]。

本设计采用Altera 公司(现已被Intel 公司收购)的EP4CE22E22C8N 型FPGA 芯片,其内部包含22 320 个逻辑单元、594 KB 嵌入式内存。外部共有144 个引脚,其中包含79 个I/O 引脚,足以满足本系统的使用要求。I/O 端口是FPGA 芯片内部逻辑系统与外界进行信息交互的桥梁,能够进行信号输入或输出。FPGA的每个I/O 端口都是独立的,可将其配置为高电平、低电平和高阻态3 种状态中的任一种。FPGA 芯片的系统时钟由外部有源晶振提供,频率为50MHz,即周期为1/50MHz=20ns,这是整个FPGA 系统运行的基本时间单位。

FPGA 程序使用QuartusⅡ软件,以Verilog 硬件描述语言编写,采用自上而下模块化的编程方法。程序主要分为UART 接口收发、上位机指令解码、CCD 时序和AD 时序产生、片上数据缓存4 个功能模块。FPGA 程序逻辑功能框图如图7 所示。

Fig.7 Logic function block diagram of FPGA program图7 FPGA 程序逻辑功能框图

首先根据程序逻辑,上位机发送指令给FPGA,FPGA读取指令,得到积分时间数据;然后开始产生CCD的积分时序,当积分时间结束,CCD 开始输出电荷时产生A/D 时序,驱动相关双采样芯片和A/D 芯片采集CCD 信号;最后,FPGA 接收到转换后的数字信号,将其缓存后,通过UART接口将数据发送到上位机。

FPGA 程序设计完成后,要用专门的仿真工具对其进行功能仿真,验证程序的逻辑功能是否符合设计要求,本文使用的仿真软件是Siemens 公司的ModelSim 10.1。ModelSim 功能仿真时序图如图8 所示,从上到下各波形依次为 P1V、P2V&TG、P1H、P2H、P3H、P4H&SG、RG、SHP、SHD、CS、CONVST、RD、BUS、BYTE。

Fig.8 Timing diagram of ModelSim function simulation图8 ModelSim 功能仿真时序图

其中,P1V 和P2V&TG 为CCD的垂直驱动信号,用来将每一列像素中的电荷垂直转移到对应的水平移位寄存器中;P1H、P2H、P3H 和P4H&SG 为CCD的水平驱动信号,RG为复位信号,用来将所有水平移位寄存器中的电荷进行水平转移并输出。P1V 和P2V&TG的周期为64us,占空比为50%,P2V&TG的相位比P1V 滞后180°。P1H、P2H、P3H 和P4H&SG的周期为16us,占空比为50%,其之间的相位关系为:依次比相邻前一个滞后90°。RG的周期也为16us,占空比为25%,其上升沿与P4H&SG的上升沿对齐。以上7路信号是CCD的驱动信号,CCD 输出信号周期与RG 一致,为16us,因此CCD 输出信号频率为62.5 kHz。

SHP 和SHD 是相关双采样芯片AD9823的采样时钟信号,在SHP 和SHD 信号的上升沿处分别对CCD 输出信号的复位电平和信号电平进行采样。

CS、CONVST 和RD 是ADS8381模数转换芯片的转换和输出控制信号,CS 信号被一直拉低,ADS8381 检测到CONVST的下降沿后即会开始转换,检测到RD的低电平时则输出数据。BUS 和BYTE 是ADS8381的输出方式控制信号,这两个信号都被拉低,表示让ADS8381 用18 个并行端口输出数据。

5 测试结果分析

5.1 CCD 采集效果测试

当ADS8381 完成模数转换后,会输出18 位二进制数据。对于本系统而言,16 位精度已足以满足应用需要,并且为使数据传输与保存更加简单,FPGA 会接收并保存其中的高16 位数据,而将最低的两位数据舍弃。但如果有更高的精度要求,也可通过升级程序实现18 位精度。之后,FPGA 会通过串口将16 位数据发送到上位机,上位机软件接收到数据后对数据进行处理,生成光谱强度分布曲线[20]。

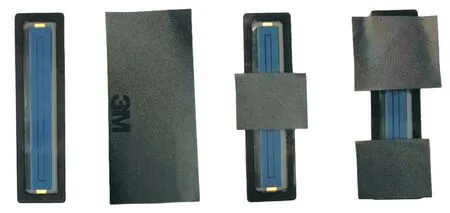

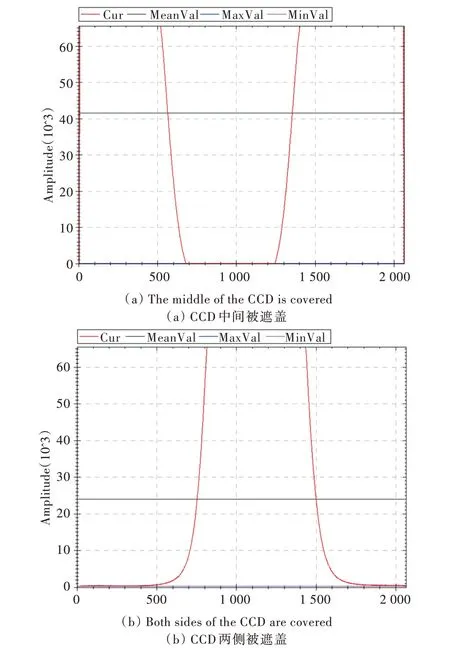

为验证CCD 对光信号的采集效果,对CCD的感光面进行部分遮光,将积分时间设置为10ms,然后观察上位机软件中的光谱强度分布曲线,确认光谱强度分布情况与遮光位置是否一致。CCD 实物及其遮光位置如图9 所示,相应光谱曲线如图10 所示。

服务不可否认性主要针对服务后抵赖问题。服务不可否认性实施的重点是避免系统内部欺诈行为,具体包括源不可否认和接收不可否认。源不可否认是指确保信息发送方在完成数据传送后不能否认曾经的数据发送行为;接收不可否认是指信息接收方在接收到数据之后不能否认曾经的数据接收行为。

Fig.9 Physical diagram of CCD图9 CCD 实物图

在上位机软件界面中,横坐标表示CCD 像素的列数,共有2 048 列像素,因此横坐标范围为0~2 047。纵坐标表示光谱相对强度,由于上位机软件接收到的是16 位二进制数据,因此纵坐标范围为0~65 535。

当CCD 没有任何遮挡时,所有像素都会达到饱和,光谱强度超出系统量程。当CCD 被完全遮盖,处于无光状态时,上位机软件中的光谱强度平均值约为80 左右。图10(a)为遮盖CCD 中间区域采集得到的光谱曲线,曲线中间的凹陷对应黑色胶带的遮光位置;图10(b)为遮盖CCD 两侧区域采集得到的光谱曲线,曲线中间的凸起对应CCD 中间无遮盖的位置。

由此可见,光谱曲线强度分布与CCD 遮光位置符合。另外,如果使用更宽或更窄的胶带进行遮光,则光谱曲线凹陷和凸起区域宽度也会随之变化。同时,由于CCD 遮光区域边缘漏光,导致光谱曲线在遮光边缘处会出现缓慢上升或下降的现象。经过计算可以得出,该系统的信噪比最高可达58dB 以上,表明该系统具有较好的噪声抑制能力。

5.2 光谱测试

Fig.10 Spectral curves图10 光谱曲线

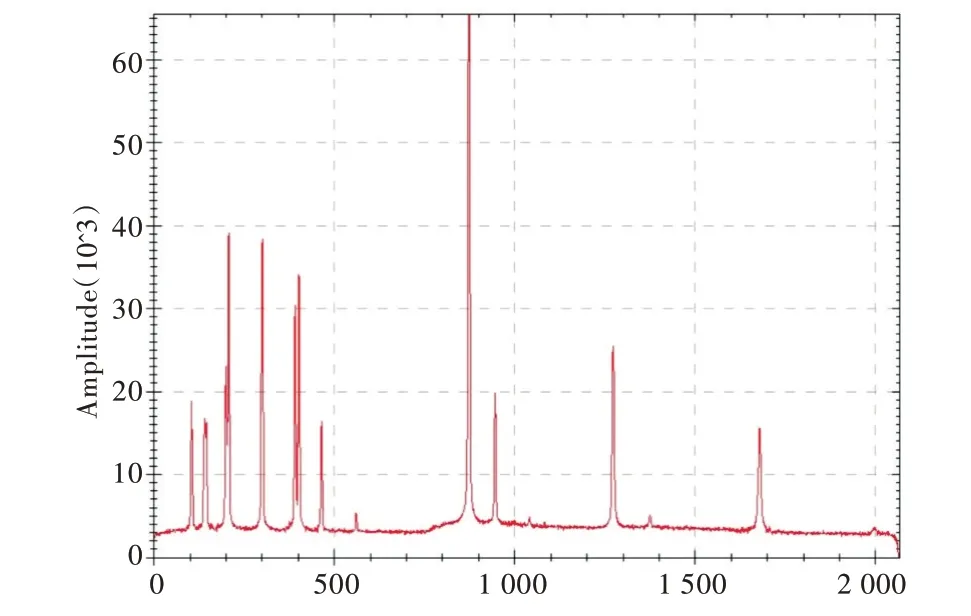

结合光路结构对光谱采集系统进行测试。使用汞氩灯作为信号源,灯光先通过光路结构,经光栅分光,分光之后的光谱照在CCD 感光面上。通过调整CCD 与光栅的相对位置,可改变照在CCD 上的光谱波长范围。根据光路结构设计,CCD 接收到的光谱波长范围为796~1 048nm。

然后,通过上位机软件给FPGA 发送采集指令,观察软件界面。如果上位机软件中显示的光谱强度分布曲线与汞氩灯的实际光谱相符合,则说明该光谱采集系统可实现预期功能。上位机软件生成的汞氩灯光谱图如图11 所示。

Fig.11 Spectrogram of mercury argon lamp图11 汞氩灯光谱图

在图11 中,将光谱强度分布图中的CCD 像素列数与波长范围进行对应,确定图中各个光谱峰位置所对应的波长。经观察,图中有11 个比较明显的峰,对应波长分别为794.82nm、800.61nm、811.53nm、826.45nm、840.5nm、842.46nm、852.14nm、912.3nm、922.45nm、965.78nm、1 013.98nm,这与汞氩灯的实际光谱特征峰基本符合,说明该光谱采集系统实现了预期功能。

在测试过程中,通过设置信号调理电路中INA849 仪表放大器的放大倍数和外部参考电压大小,可使进入到A/D芯片ADS8381的输入信号大小与其有效检测范围尽可能吻合,以实现最大的动态范围和检测精度,从而验证了该设计方案的有效性。

6 结语

由测试结果可知,本文设计的以面阵CCD 为探测器、以FPGA 为控制核心的光谱采集系统具有良好的光谱采集效果,噪声在可接受范围内,并且具有很好的灵活性,能够很方便地调节光谱基线和信号放大倍数,从而实现最大的动态范围和检测精度。在此基础上,还可增加滤波电路并对供电电路进行优化,以进一步减小噪声,实现更高的信噪比。

综上,本设计能够为拉曼光谱仪提供一个可靠的光谱采集方案。同时,本设计具有一定通用性,对于相似的CCD,只需将电源模块和CCD 驱动程序稍作修改即可。