22 nm FDSOI工艺SRAM单粒子效应的重离子实验研究

赵 雯,赵 凯,陈 伟,沈鸣杰,王 坦,郭晓强,贺朝会

(1.西安交通大学 核科学与技术学院,陕西 西安 710049;2.强脉冲辐射环境模拟与效应国家重点实验室,西北核技术研究所,陕西 西安 710024;3.上海复旦微电子集团股份有限公司,上海 200433)

全耗尽绝缘体上硅(FDSOI)工艺以其优越的短沟道控制力、低功耗、较强的抗单粒子效应(SEE)能力在抗辐射集成电路领域备受关注[1-3]。现有研究表明[4-7],FDSOI工艺静态随机存储器(SRAM)存储阵列自身的抗多单元翻转(MCU)能力较强,即使在离子大倾角入射情况下,对存储阵列采取一定的加固措施也可使其MCU得到很好控制。但是随器件工作频率的提高,SRAM外围电路单粒子瞬态(SET)所导致的存储阵列MCU的发生概率显著提高,评估这类MCU的影响和分析此类MCU的具体成因对全面提高FDSOI工艺SRAM的抗MCU能力很有必要。其次,部分研究者报道了不同测试向量对FDSOI工艺SRAM SEE的影响[5-7],但是对一些测试向量(如衬底偏置等)影响机制的分析并不深入,而影响机制分析对有效指导加固设计至关重要。最后,不同电路形式、版图布局和加固设计的FDSOI工艺SRAM的SEE特性存在差异,相关的对比性研究并不多见。

本文针对5款不同加固设计的22 nm FDSOI工艺SRAM开展重离子实验研究,对比不同测试图形、工作频率、衬底偏置和离子入射角度下SRAM的翻转截面差异,分析这些测试向量对翻转截面的影响机制;基于SRAM外围电路SET所导致的存储阵列MCU的地址信息揭示此类MCU的成因,为针对性地指导FDSOI工艺SRAM外围电路加固提供有用信息;此外,还针对不同加固设计的FDSOI工艺SRAM的抗SEE性能优劣进行讨论。

1 实验样品和设置

实验样品为22 nm FDSOI工艺SRAM,超薄体硅厚度为8 nm,埋氧层厚度为18 nm。样品含5款不同加固结构的SRAM,总存储容量为1 Mbits,共17个地址位(A0~A16)和8个数据位(B0~B7)。图1所示为存储阵列的布局图,阵列被划分为8个Block,由地址位A16A15A14控制。每个Block分为4个Section,每个Section的四分之一象限中,数据位B0~B7将该象限划分为8大行,每大行中由A9A8A7区分为8行,地址位A10A5A4A3A2A1A0控制每个象限的128列,因此,每个象限有64行×128列的存储单元。由于每个Block共2×8个象限,即每个Block共128行×1 024列的存储单元(128 kbits)。

图1 SRAM存储阵列的布局Fig.1 Layout schematic of SRAM array

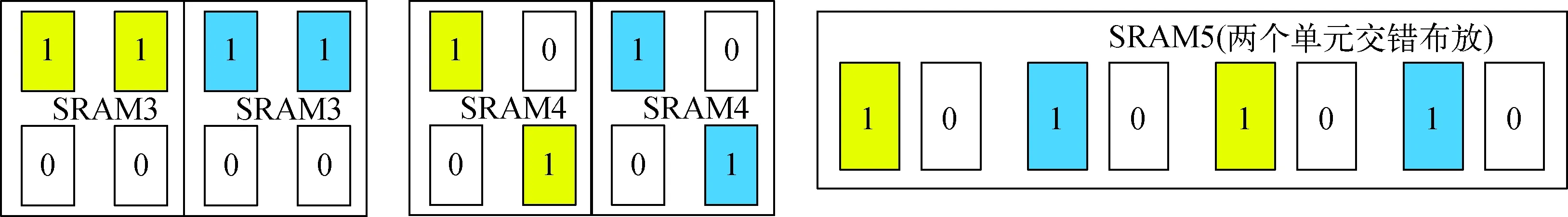

5款SRAM通过地址位的高3位A16A15A14进行区分,表1为5款SRAM的相关信息。SRAM1是在标准22 nm FDSOI SRAM的基础上通过对字线和位线的连接进行特殊处理来实现冗余加固的SRAM;SRAM2为八管加固型SRAM;SRAM3~SRAM5为3款双互锁结构(DICE)加固SRAM。DICE加固SRAM的原理如图2所示,3款DICE加固SRAM的版图布局如图3所示。

表1 5款SRAM的相关信息Table 1 Detailed information of five types of SRAMs

实验离子选用中国科学院近代物理研究所回旋加速器(HIRFL)提供的Ta离子,离子经50 mm空气层降能后,能量为1 403 MeV,射程为83.5 μm,垂直入射条件下的LET值为81.3 MeV·cm2·mg-1。实验中采用多种离子入射角度(垂直入射、45°沿字线方向入射、45°沿位线方向入射)、测试图形(全0、全1、棋盘)、衬底偏置组合(零偏置、N管正偏且P管负偏、N管负偏且P管正偏)和工作频率(1、5、10 MHz)。

图2 DICE结构原理图Fig.2 Schematic diagram of DICE structure

SEE测试采用动态测试模式,辐照前对SRAM全地址写入全0、全1或棋盘数据,在辐照过程中实时回读,若某个地址的SRAM单元所存储的数据与测试前写入的数据有差异,则认定发生翻转,此时测试系统记录下该单元的地址和错误数据,并立刻对该地址对应的存储单元配置初始数据,然后继续对后续地址进行读操作。实验中离子注量率采用104cm-2·s-1,总注量为5×106cm-2。位翻转截面计算采用式(1):

(1)

其中:i为MCU事件中发生翻转的单元个数;Ei-cell代表有i个单元发生翻转的MCU事件数;F为离子的注量;N为SRAM的存储容量;θ为离子入射角度。

图3 SRAM3~SRAM5的版图布局Fig.3 Layout schematic of SRAM3-SRAM5

2 实验结果及分析

2.1 测试图形对SEE敏感性的影响

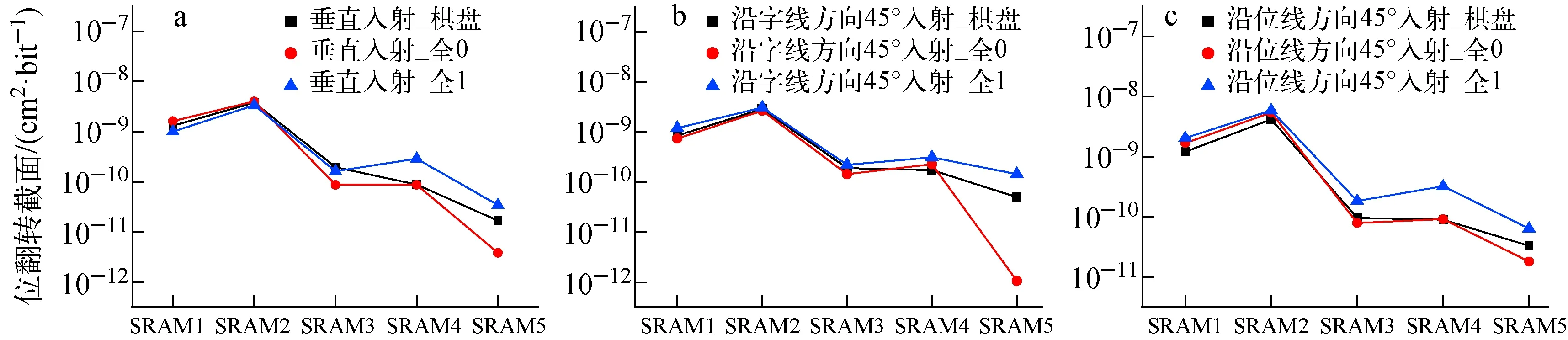

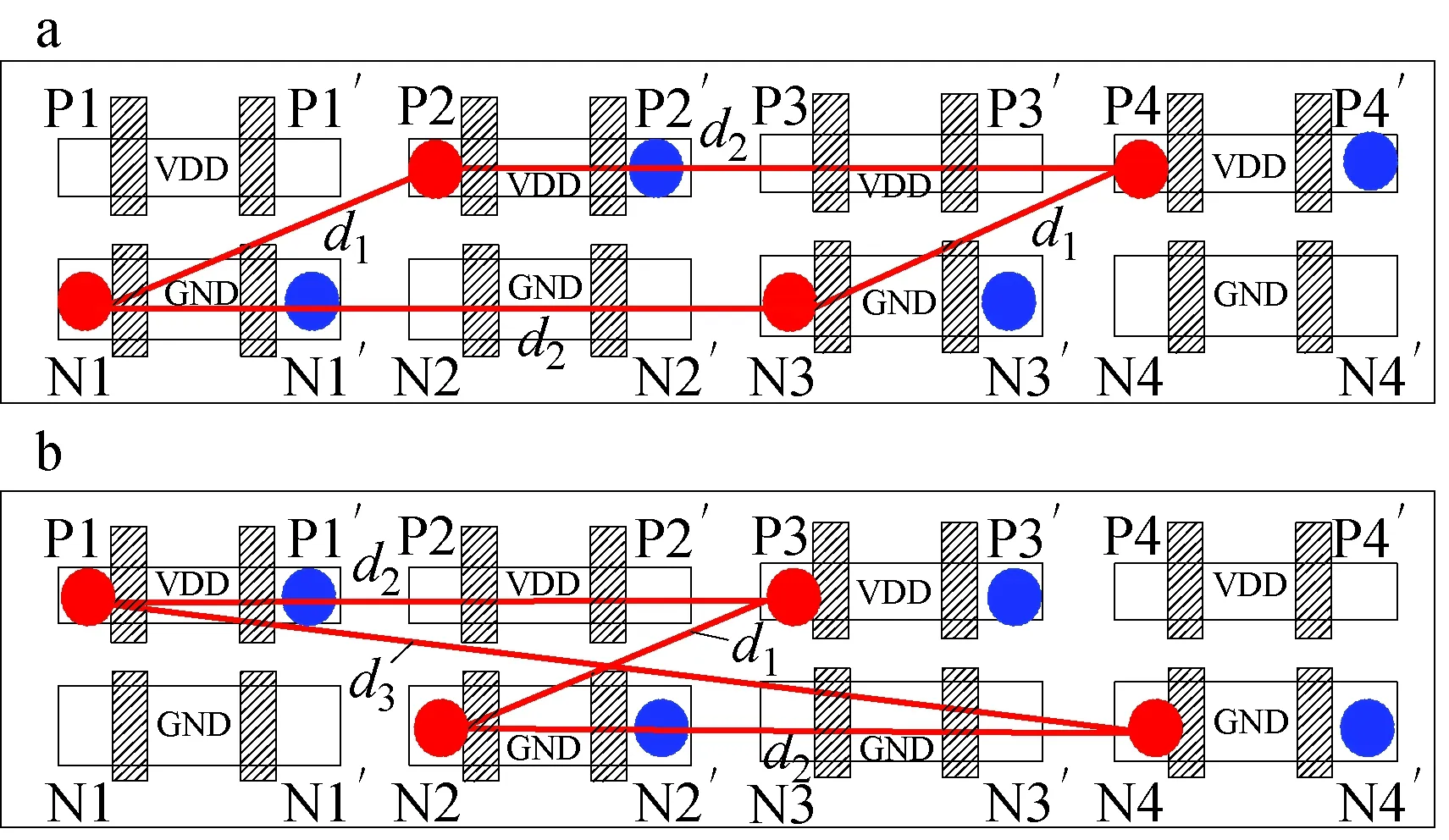

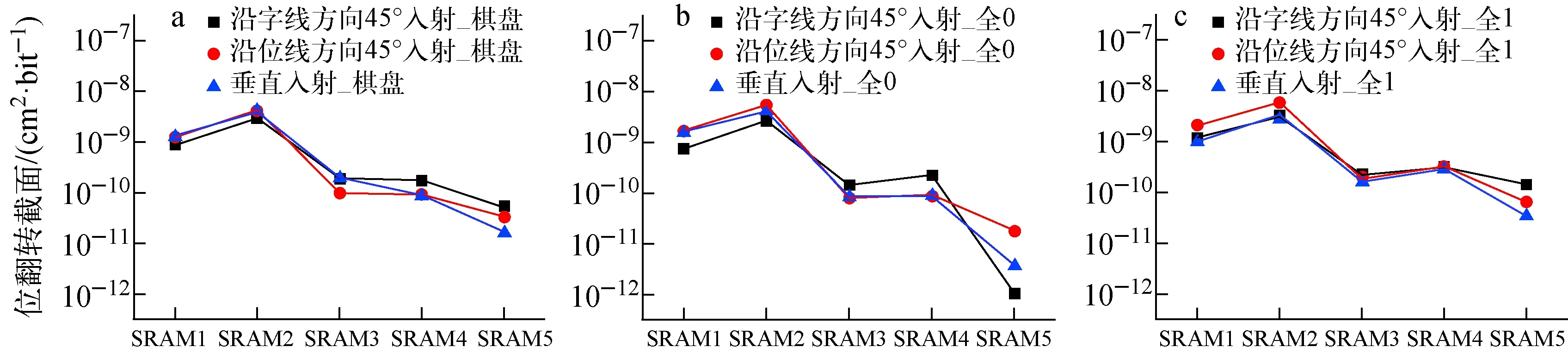

为SRAM配置3种测试图形(全0、全1和棋盘)分别进行测试,对比不同测试图形的位翻转截面差异。图4a~c分别为垂直入射、沿字线方向45°入射、沿位线方向45°入射3种条件下获取的对比结果,SRAM工作频率为1 MHz,零衬底偏置。可看出,SRAM1/SRAM2在不同测试图形下的位翻转截面差异不明显,这与不同测试图形下敏感区的对称分布有关;但对于SRAM3/SRAM4/SRAM5而言,全1测试图形的位翻转截面明显高于全0测试图形,说明1→0翻转比0→1翻转更易发生。这是由DICE单元的SEE敏感对在全0和全1测试图形下物理分布不同造成的[8],以SRAM5为例,图5a~b为SRAM5的DICE敏感对在全1和全0测试图形下的分布,SRAM5为双DICE结构,一个DICE结构的敏感对标注为红色,另一个DICE结构的敏感对标注为蓝色,两个DICE结构的敏感对分布完全一致。全1测试图形下,DICE结构4个敏感对的物理间距分别为d1、d1、d2、d2(图5a);全0测试图形下,DICE结构4个敏感对的物理间距分别为d1、d2、d2、d3(图5b)。通过对比发现,两种测试图形下,DICE结构的4个敏感对中仅有1个敏感对的物理间距存在差异,该间距在全1测试图形下为d1,在全0测试图形下为d3,由于d1明显小于d3,因此全1测试图形下更易发生单粒子翻转(SEU),其位翻转截面更高。

图4 3种离子入射角度下SRAM采用不同测试图形时测到的位翻转截面Fig.4 Bit-flip cross section measured in SRAM under different test patterns with three ion incidence angles

a——全1;b——全0图5 SRAM5的DICE敏感对在全1和全0测试图形下的物理位置分布Fig.5 Physical location distribution of DICE sensitive-area pair of SRAM5 under all 1 and all 0 test patterns

2.2 工作频率对SEE敏感性的影响

针对配置了棋盘测试图形的SRAM,对比其在1、5和10 MHz工作频率下的位翻转截面差异。图6为离子垂直入射且零衬底偏置下所获取的位翻转截面对比结果。可看出:SRAM1/SRAM2在不同频率下的位翻转截面差异不明显;SRAM3/SRAM4/SRAM5的位翻转截面随频率的增加有增大的趋势。

图6 不同工作频率下的SRAM位翻转截面Fig.6 Bit-flip cross section of SRAM at different operation frequencies

随着工作频率的增大,外围组合逻辑电路SET被俘获的概率变大[9-12],SRAM读写错误增多。这些读写错误导致的存储阵列翻转与存储阵列自身的翻转有明显区别,前者多数是同一字线上的多位同时发生翻转。通过翻转位图发现,1 MHz频率下未发现读写错误导致的存储阵列翻转,但在5 MHz和10 MHz频率下,读写错误所导致的存储阵列翻转在5款SRAM中均有发生。图7为5 MHz和10 MHz频率下,读写错误所导致的存储阵列MCU的物理位图(SRAM配置棋盘测试图形,离子垂直入射,椭圆标注的为1→0翻转,未标注的为0→1翻转)。分析发现,读写错误所导致的存储阵列MCU表现为同一字线上的4个位同时翻转,且这4位为8位数据中的间隔位:2、4、6、8位或1、3、5、7位。测试时SRAM写入的是棋盘测试图形,2、4、6、8位发生的是0→1翻转,1、3、5、7位发生的是1→0翻转,在图7中将4位的1→0翻转进行了圈注,可看出,4位的1→0翻转的事件数明显小于4位的0→1翻转的事件数。对于发生概率明显较高的4位0→1翻转(错误发生后同一字线的8个数据位全为1)事件,分析原因是:当读电路受到离子入射后产生SET,SET被俘获导致读时序出现错误,被选中的地址上的8位数据无法被正常地读出,由于8条读数据线上的预冲数据为1,因此,读出了8个数据位全为1的错误信息。对于发生概率很低的4位的1→0翻转(错误发生后同一字线的8个数据位全为0)事件,分析原因是:在某一读周期检测到某个地址发生翻转,立即对该地址执行写操作,但写电路的SET影响到正常的写预冲功能,导致8个数据位全部被写为0,在下一个读周期,读电路读出了8个数据位全为0的错误信息。由于在测试过程中,读操作在循环进行,写操作只在监测到翻转后才执行,因此写操作出错的概率明显低于读操作,导致4位的1→0翻转的事件数明显小于4位的0→1翻转的事件数。由图7可看出,随工作频率从5 MHz增加到10 MHz,5款SRAM的读写错误所导致的存储阵列翻转事件数均增大,这与读写电路发生SET后被俘获的概率增大有关。值得注意的是,写错误导致的MCU发生在同一字线的4个数据位,传统的错误校正码(ECC)并不能很好地对其纠错,读错误导致的MCU虽只在特定周期存在,但也会干扰电路的正常功能。

对SRAM1/SRAM2而言,读写错误所导致的存储阵列翻转数(翻转事件数×4)比总翻转数(读写错误所导致的存储阵列翻转数与存储阵列自身的翻转数之和)低2~3个数量级,虽然随工作频率的提高,读写错误所导致的存储阵列翻转数有所增加,但是这个增加量并不能对总的位翻转截面产生明显影响,因此这两款SRAM在不同频率下的位翻转截面差异不明显;然而,SRAM3/SRAM4的总翻转数介于100~200之间,SRAM5的总翻转数甚至小于100,随着工作频率提高,读写错误所导致的存储阵列翻转数的增加量基本在几十个左右,对位翻转截面的影响显著,导致SRAM3/SRAM4/SRAM5的位翻转截面随频率的增加出现增大的趋势。

2.3 衬底偏置对SEE敏感性的影响

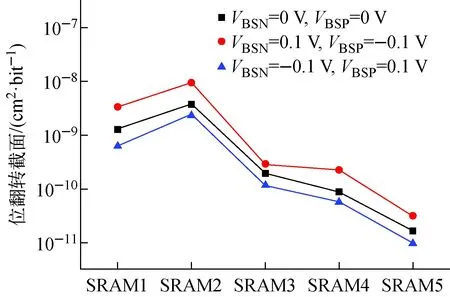

FDSOI器件的一大优势是可通过调节衬底偏置实现电路工作频率和功耗的性能优化:正向衬底偏置模式下器件的阈值电压较小,可应用在需要快速导通晶体管的电路中;负向衬底偏置模式下器件的漏电流更低,可应用在对功耗要求较高的电路中[13]。对FDSOI工艺的抗辐射集成电路而言,研究衬底偏置对FDSOI SRAM SEE的影响具有必要性。针对配置了棋盘测试图形的SRAM,分别采用不同的衬底偏置组合(NMOS和PMOS衬底均采用零偏置、NMOS衬底采用0.1 V偏置且PMOS衬底采用-0.1 V偏置、NMOS衬底采用-0.1 V偏置且PMOS衬底采用0.1 V偏置)进行测试,对比不同衬底偏置情况下的位翻转截面差异,图8为离子垂直入射时不同衬底偏置情况下的SRAM位翻转截面。

图7 5 MHz频率(a)和10 MHz频率(b)下读写错误所导致的存储阵列MCU的物理位图Fig.7 Physical bitmap of storage array MCU caused by read-write error at 5 MHz frequency (a) and 10 MHz frequency (b)

图8 不同衬底偏置情况下的SRAM位翻转截面Fig.8 Bit-flip cross section of SRAM with different substrate-bias voltages

将NMOS的衬底偏置用VBSN表示,PMOS的衬底偏置用VBSP表示,可看出,5款SRAM表现出相同的趋势:VBSN=0.1 V且VBSP=-0.1 V时的截面最大,VBSN=VBSP=0 V时的截面次之,VBSN=-0.1 V且VBSP=0.1 V时的截面最小。这与文献[5-6]的实验结果类似。当NMOS衬底偏置电压大于0 V时,顶层硅膜的耗尽层变窄,电离受主数量减少。一方面,由于固定栅压下负电荷的数量一定,电离受主数量的减少导致反型层电子数量增多[13],为产生与衬底零偏置情况相同数量的反型层电子,NMOS衬底偏置电压大于0 V时,栅极电压需降低,即NMOS阈值电压Vthn减小;另一方面,离子入射后产生大量电子-空穴对,电子被漏极收集,当NMOS衬底偏置电压大于0 V时,顶层硅膜的耗尽层变窄,有利于空穴堆积在体区以抬高体电势,促进寄生双极放大效应的产生。FDSOI工艺器件的寄生双极放大效应和阱结构不太相关,因此NMOS寄生双极放大效应和PMOS寄生双极放大效应是类似的。同理,当PMOS衬底偏置电压小于0 V时,顶层硅膜的耗尽层变窄,电离施主数量减少。一方面,由于固定栅压下正电荷的数量一定,电离施主数量的减少导致反型层空穴数量增多,为产生与衬底零偏置情况相同数量的反型层空穴,PMOS衬底偏置电压小于0 V时,栅极电压绝对值需降低,即PMOS阈值电压绝对值|Vthp|减小;另一方面,离子入射后产生大量电子-空穴对,空穴被漏极收集,当PMOS衬底偏置电压小于0 V时,顶层硅膜的耗尽层变窄,有利于电子堆积在体区以降低体电势,促进寄生双极放大效应的产生。

综上,VBSN=0.1 V且VBSP=-0.1 V时,Vthn和|Vthp|均减小,NMOS和PMOS的寄生双极放大效应的发生概率提高。当VBSN=-0.1 V且VBSP=0.1 V时,Vthn和|Vthp|均增大,NMOS和PMOS的寄生双极放大效应受到抑制。

根据文献[14]可知,SRAM中对SEE敏感的截止NMOS和截止PMOS的临界电荷分别为:

(2)

(3)

其中:Qcri-N为NMOS临界电荷;Qcri-P为PMOS临界电荷;Cg-N为NMOS的栅极电容;Cg-P为PMOS的栅极电容;Vsw为NMOS和PMOS所组成反相器的转移特性曲线的转换电压。这里默认SRAM中两个反相器的特性一致,因此SRAM中两组反相器的Vsw相等。从式(2)、(3)可知,临界电荷与Vsw和Cg有关。

NMOS和PMOS阈值电压的变化会影响SRAM的电压转换特性,从而影响Vsw的数值。HSPICE仿真结果(图9)显示,对SRAM1/SRAM2而言,VBSN=0.1 V且VBSP=-0.1 V时,Vsw比零偏置情况低1 mV;VBSN=-0.1 V且VBSP=0.1 V时,Vsw比零偏置情况高1 mV。对SRAM3/SRAM4/SRAM5而言,VBSN=0.1 V且VBSP=-0.1 V时,Vsw比零偏置情况低2 mV;VBSN=-0.1 V且VBSP=0.1 V时,Vsw比零偏置情况高2 mV。可看出,Vsw在3种偏置条件下的差异很小。

栅极电容Cg的计算参见式(4),其中εox和Tox分别为栅极氧化层的介电常数和厚度,Lg和Wg分别为晶体管的栅长和栅宽。据文献[15]分析,晶体管衬底偏置会通过影响沟道长度Lg来使栅极电容Cg发生变化,但是对于0.1 V的衬底偏置电压而言,Cg的改变可忽略不计。

(4)

综上分析,3组衬底偏置条件下,Vsw和Cg的差异很小,根据式(2)、(3),晶体管SEE临界电荷的差异不会很大,不足以造成图8中3组衬底偏置条件的明显截面差异。因此,衬底偏置电压主要通过对寄生双极放大效应的控制来影响SRAM的SEE敏感性。VBSN=0.1 V且VBSP=-0.1 V时,NMOS和PMOS的寄生双极放大效应的发生概率提高,电荷收集增加,因此SRAM位翻转截面最大。当VBSN=-0.1 V且VBSP=0.1 V时,寄生双极放大效应受到抑制,因此SRAM位翻转截面最小。

2.4 离子入射角度对SEE敏感性的影响

采用3种不同离子入射角度(垂直入射、沿字线方向45°入射和沿位线方向45°入射)对SRAM分别进行辐照,对比不同入射角度下的位翻转截面差异(频率为1 MHz,零衬底偏置)。图10a~c分别为棋盘、全0和全1测试图形下获取的对比结果。可看出,5款SRAM的位翻转截面并未随着离子入射角度的增加而明显增大,这是FDSOI工艺SRAM与体硅SRAM的差异。SOI工艺器件埋氧层的存在,使得离子在其衬底沉积的电荷并不能被漏极收集,很大程度地降低了总电荷收集量。同时,SOI工艺器件的SEE敏感区位于顶层硅膜的超薄区域,只有离子入射的倾角很大时才能使得离子径迹同时穿过多个敏感区来诱发MCU[16]。对体硅SRAM而言,沉积在衬底的电荷可通过漏斗效应被有效收集[17],共用阱工艺也会大幅增加电荷共享[18-21],因此即使在较小的离子入射倾角下仍可能诱发MCU。

a——SRAM1/SRAM2;b——SRAM3/SRAM4/SRAM5图9 SRAM中对接反相器的转移特性曲线的转换电压随NMOS/PMOS晶体管衬底偏置的变化Fig.9 Switching voltage of transfer characteristic curve of inverter in SRAM vs substrate-bias voltage of NMOS/PMOS transistor

图10 3种测试图形下离子以不同角度入射SRAM时测到的位翻转截面Fig.10 Bit-flip cross section measured in SRAM for different ion incidence angles under three test patterns

2.5 5款SRAM的SEU和MCU敏感性对比

从不同测试条件下5款SRAM的位翻转截面来看,SRAM2的抗翻转能力最弱,SRAM1稍强,3款DICE加固的SRAM(SRAM3/SRAM4/SRAM5)抗翻转能力较好。进一步比较3款DICE加固的SRAM可发现,采用双DICE结构的SRAM5的抗翻转能力最强。对SRAM3和SRAM4而言,在棋盘测试图形下,SRAM4的截面较低;但在全0和全1测试图形下,SRAM4的截面较高。

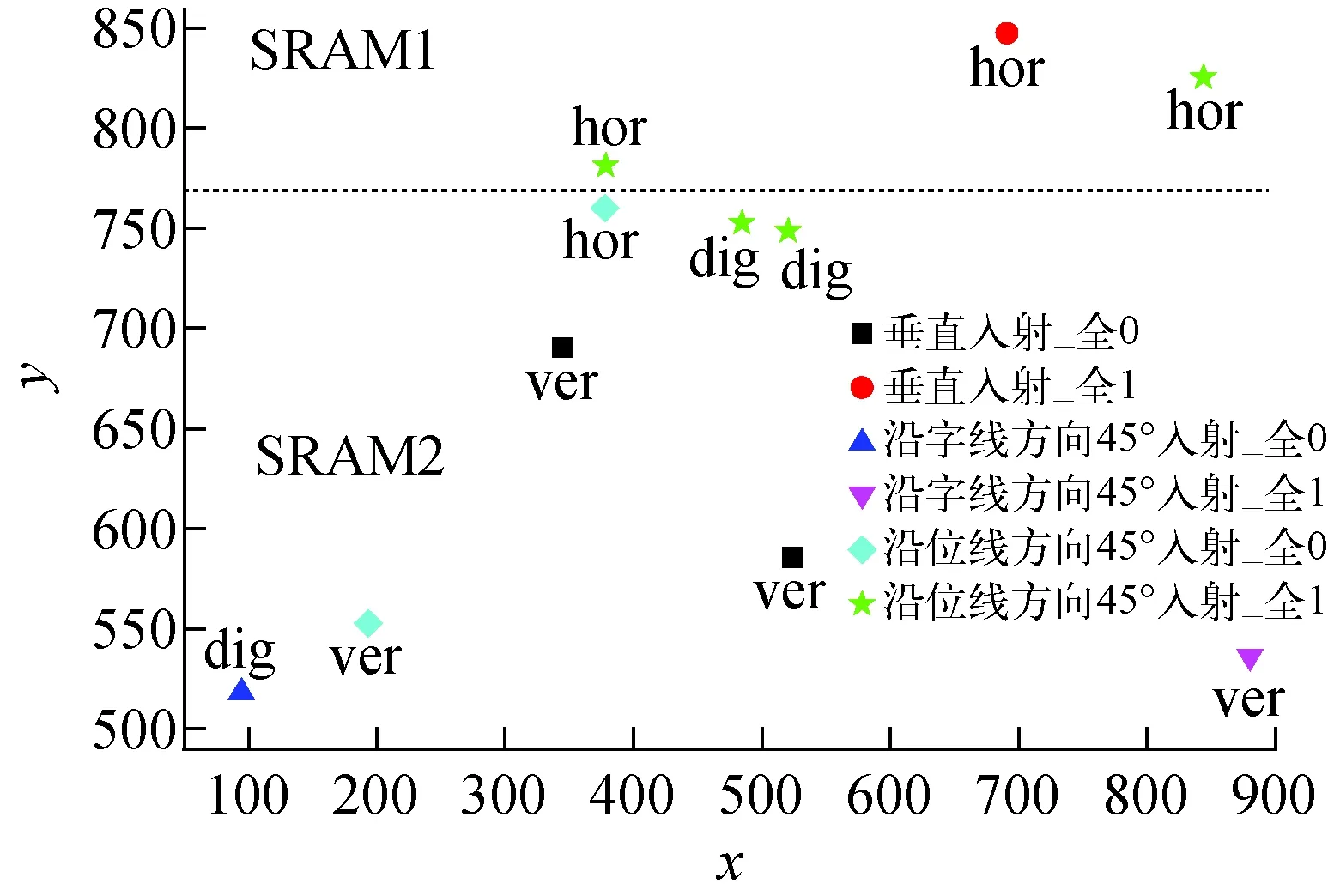

图11 SRAM1和SRAM2中测到的2位MCU的物理位图Fig.11 2-bit MCU physical bitmap measured in SRAM1 and SRAM2

若剔除外围电路读写错误导致的MCU而只考虑存储阵列自身的MCU,5款SRAM中,仅SRAM1和SRAM2发生了极少量的2位MCU,且SRAM2的2位MCU数量比SRAM1多,DICE加固的3款SRAM未发生存储阵列自身的MCU,这证明FDSOI工艺DICE结构在离子高线性能量传输值(LET)或斜入射情况下仍具有较强的抗MCU能力。对于体硅DICE结构而言,离子LET值增大或斜入射会增加其MCU敏感性,但当DICE结构采用FDSOI工艺时,即使在离子高LET值或斜入射情况下,MCU敏感性很低。将SRAM1和SRAM2中观察到的2位MCU的物理位图示于图11,由于发生翻转的2个SRAM单元的物理位置很近,在图11中难以区分翻转图形,因此在2位MCU的发生位置处将翻转图形做了文字标注,其中ver代表垂直2位MCU,hor代表水平2位MCU,dig代表对角2位MCU,可看出,SRAM1的2位MCU均为水平方向,SRAM2的2位MCU以垂直方向和对角方向居多,这与SRAM的敏感区在水平和垂直方向的间距差异有关。

3 结论

本文针对5款不同加固设计的22 nm FDSOI工艺SRAM开展了重离子SEE实验,获取了不同测试图形、工作频率、衬底偏置和离子入射角度下SRAM的翻转数据。结果发现,对于存储阵列加固效果较好的3款DICE型FDSOI工艺SRAM而言,存储阵列自身的翻转数较小,读写错误所导致的存储阵列翻转对SRAM软错误的影响显著,且该影响随频率的升高更加严重。3种衬底偏置条件下SRAM的临界电荷变化不大,衬底偏置电压主要通过对寄生双极放大效应的控制来影响SRAM的翻转敏感性。从不同测试条件下5款SRAM的位翻转截面来看,抗翻转能力由弱到强依次为八管加固型SRAM2、冗余加固型SRAM1、DICE加固型SRAM3或SRAM4(棋盘测试图形下,SRAM3的抗翻转能力比SRAM4弱;全0、全1测试图形下,SRAM3的抗翻转能力比SRAM4强)、双DICE加固型SRAM5。此外,在存储阵列自身抗MCU性能方面,SRAM1和SRAM2发生了极少量的2位MCU,且SRAM2的2位MCU数量比SRAM1多,DICE加固的3款SRAM未发生存储阵列自身的MCU,这证明FDSOI工艺DICE结构在离子高LET值或斜入射情况下仍具有较强的抗MCU能力。