基于国产HKSP6101处理器的数据处理子卡设计

王晓鸽 韩振国 孔梁 张梦园

【摘要】 航空电子系统的复杂度日益增大,因而对处理器等关键硬件技术提出了更高的要求。对嵌入式系统的数据处理能力的要求也越来越高[1]。近年来,嵌入式系统越来越趋向于综合化、智能化,对于国产处理器数据处理硬件设计的要求也逐步提升。本文介绍了一种基于国产HKSP6101处理器的数据处理子卡设计和实现,并对部分功能单元的设计进行了详细描述。该模块具有处理能力强、通用性强、功耗低等特点,具有较高的应用价值,目前该模块已经应用于多种嵌入式电子设备中,能够在接口功能、处理性能等方面覆盖多种同级别PowerPC处理器的指标,实现完全替代或者功能替代。

【关键词】 HKSP6101处理器 数据处理子卡 嵌入式

引言:

随着计算机技术、通信技术的飞速发展,数据处理子卡设计向着高技术、高性能、低功耗的目标发展[2]。与此同时,进口处理器也面临停产风险,因此,国产器件也需要具备高质量的数据处理能力,本文介绍了一种基于国产HKSP6101处理器的高性能数据处理子卡,采用通用设计思想、可配置性设计,可用于多种嵌入式系统。

一、系统结构

本文所描述的数据处理子卡是基于国产HKSP6101处理器,硬件配置256MB的SDRAM,128MB的FLASH,128KB的NvRAM存储电路。子卡提供100MHz以太網、RS232、PCI总线等对外接口。数据处理子卡选用CPLD实现中断管理、复位控制、看门狗、离散量采集等功能,子卡原理组成结构如图 1。

二、设计与实现

(一)处理器

数据处理子卡采用国产HPSK6101处理器,该处理器整体架构图如图 2所示。HPSK6101处理器包含双指令执行、32位超标量RISC处理单元,最高工作主频为250MHz。HPSK6101集成L1 Cache,32kB指令Cache和32kB数据Cache。同时,集成L2 Cache,256kB指令、数据共享型Cache。HPSK6101处理器提供EBC存储器接口和SDRAM存储器接口,32/64位数据接口,支持ECC校验和自动刷新。HPSK6101还提供PCI主机接口,支持HOST及AGENT模式,频率支持33/66MHz和2路以太网接口,支持10/100Mbps自适应传输速率。HPSK6101还提供4路UART、16路双向GPIO、2路I2C和航空专用接口(1553B)等对外接口。

(二)存储器

数据处理子卡存储器计有SDRAM存储器、SYSTEM FLASH存储器、USER FLASH存储器、NVSRAM存储器。

数据处理子卡配置72位宽度(其中8位为ECC数据校验位)的256Mbyte的SDRAM、16位宽度32Mbytes的USER FLASH存储器、16位宽度32Mbytes的SYSTEM FLASH和128KB的NVSRAM。其中,USER FLASH存储器用于存储应用程序;SYSTEM FLASH用于存储CPU模块引导程序、PUBIT测试程序,FLASH在板编程程序,网口操作系统;NVSRAM用于掉电数据保护。每片内有128KB的SRAM和128KB的EEPROM,掉电时利用大容量钽电容的电能由SRAM中的数据写入EEPROM中,上电时自动从EEPROM中写入SRAM中,恢复掉电时的数据。

(三)复位

控制子卡的复位电路通过SM706复位芯片和CPLD实现对子卡复位信号的管理,看门狗功能的喂狗操作可以采用0欧姆跳线选择CPLD与6101处理器。具体设计如图 3所示:

(四)时钟设计

数据处理子卡时钟电路如图 4所示。采用40MHz晶振,为HKSP6101处理器提供40MHz的SYSCLK,经过处理器分频和倍频输出66MHz的SDRAM时钟和33MHz的PCI时钟;采用25MHz晶振,提供25MHz的单端时钟,为以太网PHY芯片提供工作时钟。

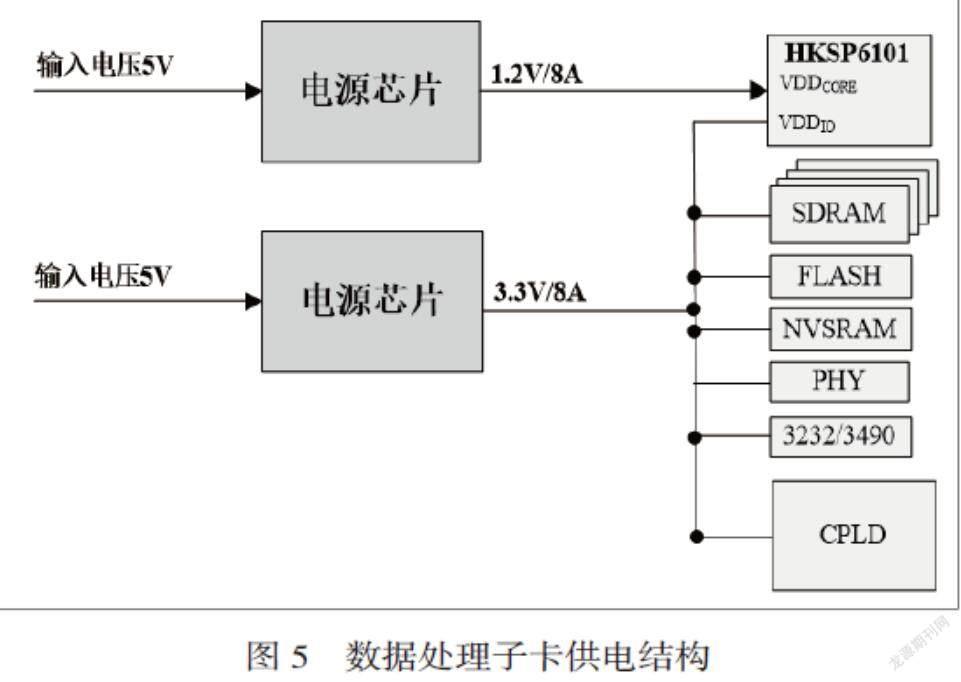

(五)电源设计

数据处理子卡供电设计如图 5所示,通道1提供一路3.3V作为芯片的接口电压和CPLD的电压;通道2提供一路1.2V作为HKSP6101处理器核电压。

控制管理模块上的输入电源为来自母板的数字5V电源。对于处理器端,需要产生IO电压3.3V、内核电1.2V、处理器锁相环电压VCC_3.3V_PLL1;CPLD侧,供电电压IO电压为3.3V。

三、结束语

本文结合国产的HPSK6101处理器的特征,设计了一款通用数据处理子卡,可硬件配置存储电路,提供以太网、RS232、PCI总线等对外接口,实现中断管理、复位控制、看门狗、离散量采集等功能,适用于多种航空武器装备。该子卡能够适用于大多数嵌入式应用环境,有广泛的应用场景。

作者单位:王晓鸽 韩振国 孔梁 张梦园

航空工业西安航空计算技术研究所

参 考 文 献

[1]韩振国,边庆.基于P2010处理器的综合化模块数据处理硬件设计[J].信息通信,2018.

[2]高毅,韩振国,沈华.数据链系统中高性能通信处理模块设计与实现[J].大众科技,2015.