一种用于频率估算的USB3.0 高速数据传输系统*

郝艳阳,苏淑靖,裴永浩,冯成林

(中北大学电子测试技术国家重点实验室,山西 太原 030051)

频率估算是信号处理的最基本问题之一,也是振动分析、阵列信号处理、电磁学等众多领域的关键问题[1-3]。计算机或专用设备只能对有限多个样本进行计算,因此需对信号进行截断,由此导致在使用快速傅里叶变换(fast Fourier transform,FFT)对信号进行处理时会产生频谱泄露等问题。基于此,提出了全相位快速傅里叶变换(all-phase fast Fourier transform,apFFT),其通过对数据进行预处理来减小信号的截断误差。同时apFFT 谱分析具有良好的抑制频谱泄漏性能和水平相位特性等优良性质[4],无需借助任何校正方法即可从谱分析中获得真实相位值,根据精确的相位来估算频率。

在文献[3]中用实验验证,在低噪声场合下,全相位频率估算的频率校正误差为(10-4~10-5)×Δω级别,Δω为频率分辨率,其值为Δω=2π/N,N为样本大小,由此可知,样本点数越多,频率估算精度越高。当采样点数较多时,实时信号处理可操作难度大,需要先预存采集数据,以便后续数据分析处理,因此本设计先将时钟信号数据传送至PC 机进行存储,再通过调用存储文件进行频率估算。本设计使用速度快且易扩展的USB3.0 进行数据传输,USB 3.0 外设控制器使用Cypress 旗下的EZ_USB FX3。该控制器有一个高度灵活的可编程接口——GPIF II接口,将其连接至外部FPGA,使之作为同步从设备FIFO(Slave FIFO)接口,完成从FPGA 至USB 至PC机的数据传输。在数据传输速率得到有效提升的同时,确保数据传输的可靠性与稳定性。

1 系统整体方案设计

本文设计的频率估算系统由时钟源、FPGA 控制单元、USB 传输单元及频率估算单元组成。如图1 所示,FPGA 控制A/D 转换器将时钟源产生的1 MHz 模拟信号转换为16 位串行数据传送至FPGA,并将读取回的串行数据转换为16 位并行数据通过数据缓存FIFO 传输至USB 芯片,进而传输至PC 机进行存储。再由仿真软件调用文件对接收到的数据进行apFFT 频率估算。

图1 系统结构框图

2 FPGA 内部设计

FPGA 作为频率估算系统的控制核心,利用A/D转换器对时钟源进行采样,并控制USB3.0 将采集到的数据传输至PC 机。FPGA 采用Xillix 公司的Airtix-7 系列XC7A100T 芯片,适合高速数据通信和高速数据采集等应用,可以很好地满足系统的控制需求。

当GPIF II 接口作为同步Slave FIFO 接口[5]时,FPGA 作为主控制器,可将EZ_USB FX3 看作FIFO存储器(DMA 缓冲区,DMA buffer),通过编写代码,实现在FPGA 上执行一个与同步Slave FIFO 相兼容的主控接口,完成从FPGA 至USB 的数据传输。根据USB 同步Slave FIFO 接口控制框图及接口时序图对FPGA 的控制程序进行设计:FPGA 内部开辟一个大小为16 KB 的FIFO 缓冲单元,对从时钟信号源采集到的数据进行缓存,当数据缓存至缓冲区半满时,将Slave FIFO 接口写入选通信号slwr 拉低,开始向FX3 的DMA buffer 内写入数据。FPGA 内部执行一个计数机制,始终将与DMA buffer 大小(8 KB)相同的数据量写入DMA buffer 内,当计数值超过DMA buffer 的大小时结束数据传输。该计数机制只通过监控满/空标志FLAG_A 来决定数据传输开始的时间,避免了使用USB 局部标志FLAG_B 来决定结束传输的时间,免除了水印值的设置。

FPGA 状态机包含两个状态:“等状态”与“传数状态”,具体状态转换条件如图2 所示。

图2 状态机跳转及其条件转换关系

如图2 所示,系统启动后进入状态机“等状态”,D 触发器在flag_A 上升沿时触发并锁存“1”进去,此时等待FPGA 内部FIFO 被写至半满(8 KB,即写入4 096 个点),半满信号来临与D 触发器所存结果(信号1)进行“与”操作,其结果为“1”时跳转至“传数状态”,与此同时,半满信号触发计数器执行计数,计数0~4 095 时,计数器输出count_flag 标志信号,计至4 095 后自动将计数清零,并将标志count_flag 拉低,count_flag 信号同时送至FIFO 读使能端作为读使能信号rd_en,控制FIFO 在100 MHz读时钟驱动下往外读数并送数据至EZ-USB FX3 的DMA buffer 内,FIFO 输出数据的有效标志valid 信号取反后作为USB 的写使能slwr。

3 USB 固件及上位机设计

3.1 数据传输架构的搭建

EZ_USB FX3 以同步从设备FIFO 方式工作,依靠芯片内部的多个FIFO 缓冲区来实现使用FX3 的DMA 运行机制工作[6],即通过套接字(Socket)、DMA 描述符(DMA descriptor)、DMA 缓冲区(DMA buffer)共同配合完成数据传输。根据FPGA 的逻辑设计,同时结合DMA 运行机制来搭建USB3.0 数据传输的架构。本设计创建一个从GPIF II 处理接口模块(PIB 模块)至USB 接口模块(UIB 模块)的DMA 通道,将之设置为AUTO 模式,使外部数据无需片内CPU 干预,便可以通过同步Slave FIFO 接口将数据连续写入FX3,再传输至PC 机;在DMA 通道内设置4 个大小为8 KB 的DMA buffer,用于上传数据的存储;将USB 端点设置为块传输模式,且端点的最大数据包大小为1 024 byte;数据传输构架如图3 所示,PIB 模块根据FPGA 发送来的0x00 地址信号,匹配内部的专用数据路径GPIF 线程0,将外部数据引脚连接至默认映射的套接字0(PIB_SOCKET_0),使得套接字0 作为发送套接字,将数据写入DMA 缓冲区内。使用UIB 模块的套接字1(UIB_SOCKET_1)作为接收套接字,从DMA 缓冲区内读取数据,将数据传送至USB 输入(IN)端点0x81,通过管道传输给PC 机。

图3 FX3 数据传输架构

3.2 FX3 固件应用程序设计

FX3 上电后,需加载存储于EEPROM 芯片(电可擦除可编程存储非只读芯片)中的设备“驱动软件”——固件[7],驱动FX3 来完成预期的设备功能。FX3 固件应用程序主要由初始化程序和用户定义程序两部分组成[8-9]。初始化程序首先完成设备(FX3)的初始化,后进入RTOS(实时操作系统),调用CyFxApplicationDefine 函数创建并激活用户自定义线程,进入用户定义程序(从设备FIFO)部分。用户定义程序先对GPIF II 模块及USB 模块进行初始化,后注册回调函数,对各种请求和事务进行响应。当接收到USB_SET_CONFIGURATION 请求时调用CyFxSlFifoAppInStart()函数,根据需求配置USB 端点并创建GPIF 接口和USB 端点之间的DMA 通道。当检测到USB 复位或断开连接时调用CyFxSlFifoAppInStop()函数,禁用USB 端点并释放DMA 通道。程序结构流程图如图4 所示。

图4 固件程序结构流程图

本设计的FX3 固件程序主要配置以下几项内容:使用GPIF II Designer 工具对GPIF II 接口进行配置;使用Eclipse 开发环境进行固件开发,对USB端点进行配置,创建GPIF 接口和USB 端点之间的DMA 通道。

使用GPIF II Designer 将GPIF II 接口设置为同步Slave FIFO 接口,规定其并行数据总线宽度为16位,地址总线为2 位,设置信号FLAG_A 的工作模式为Tread_0_DMA_Ready,将该标志配置为线程0 的跟随标志,用来监控DMA buffer 的满空状态。GPIF II Designer 根据设计需求生成状态机,并在项目编译后生成cyfxgpifconfig.h 文件,将此头文件包含到Eclipse 项目,即可实现对GPIF II 接口的配置。

在Eclipse 开发环境中,根据搭建好的USB3.0 数据传输架构,在固件用户自定义程序中对USB 端点进行配置并创建对应的DMA 通道。定义DMA buffer的个数为4,每个DMA buffer 的大小为8 KB;定义USB 端点1 为输入端点,其地址为0x81(第7 位代表传输方向,1 为输入,0 为输出);定义生产者的发送套接字为PIB 模块的套接字0,消费者的接收套接字为UIB 模块的套接字1;功能实现代码如下:

在CyFxSlFifoAppInStart(void)函数中进行端点的配置及DMA 通道的建立。先进行USB 端点的配置,将端点使能,设置其类型为CY_U3P_USB_EP_BULK,使USB 与PC 机的传输方式为块传输;当检测到连接的主机USB 接口为USB3.0 时,设置端点的最大数据包大小为1 024 byte(1 kbyte);将配置好的端点赋给端点1,功能实现代码如下:

其次,创建PIB 模块至UIB 模块的DMA 通道。DMA 通道的类型为自动模式;其中DMA buffer 的个数,每个DMA buffer 的大小,发送套接字与接受套接字均按宏定义进行设置,其他设置按默认设置即可,功能实现代码如下:

3.3 数据传输上位机的设计

Cypress 公司提供了完整的测速软件程序,其核心控制类为CyAPI 控制函数类,该类为EZ_USB FX3 系列USB 接口芯片提供了精细的控制接口,通过插入CyAPI.h 头文件和CyAPI.lib 库文件于应用程序中,可便捷实现相应控制函数的调用[8-9]。该程序首先安排了用户界面以及按钮资源,并通过CCyUSBDevice 函数获取USB 设备及输入端点,其次建立了XferLoop 线程,在线程内开辟内存来存放来自USB 的数据,通过BeginDataXfer 函数与Finish-DataXfer 函数来开启或关断通过USB 端点的数据传输。该软件用于对数据传输速率的测试,无法满足存储数据的应用需求,需添加写文件功能。首先添加头文件及命名空间:

其次在私有成员数据中添加静态文件指针数据:

最后分别在XferLoop()函数与AbortXferLoop()函数中添加写文件与关闭文件,将PC 机buffer块中的数据以二进制形式写入文件中,关键代码分别如下:

实现将USB 上传至PC 机的数据存储至文件中。

4 apFFT 频率估计算法

本文采用全相位时移相位差法校正法[10]来估算频率精度,其区别于普通相位差法校正法在于对数据进行全相位FFT 谱分析(apFFT 谱分析)。

apFFT 谱分析的重心在于全相位数据预处理。数据预处理流程:先把两个N阶窗进行卷积运算得到长为2N-1 的卷积窗ωc,用卷积窗ωc与长为2N-1的数据向量进行数据加权,后将左边各数据向右平移N个延时单元,再与位置重叠的另一个数据相加,形成N个数据y(i),i=0,1,…,N-1。对形成的N个数据作FFT(快速傅里叶变换),即为apFFT。最终可得到离散谱Y(k)。apFFT 谱分析结构框图如图5 所示。

图5 全相位谱分析结构框图

采连续两段长为N的样本并分别进行FFT,利用对应谱线的相位差值校正出谱峰处的准确频率和相位是第一类传统相位差校正法[11],该方法相比于传统能量重心法具有更高的频率估计精度,它是基于传统FFT 谱分析的线性时不变性质而推出的。而全相位FFT 谱分析具有线性性质和相位不变性这两个重要性质,充分利用这两个性质并结合传统第一类相位差法的算法构造思路,便形成了基于全相位FFT 谱分析的时移相位差校正法[12]。文献[13]已证,对序列x(n)=Aej(ω0n+θ),n∈[-N+1,N-1]进行前、后双窗均为f的双窗apFFT,得到的离散谱为:

式中:A为幅值,ω0为数字角频率,θ为初相,Fg(ω)为f对应的归一化幅度谱。主谱线k*上的相位谱为

图6 apFFT 时移相位差法的频谱校正流程图

式中:fs为采样频率。因汉宁窗可以有效抑制频谱泄露且频率分辨率较高,本文选用其作“双窗apFFT”。根据以上算法流程,编写MATLAB 程序,实现对频率的估算。

5 测试结果分析

采用分步调试的方法对本系统进行测试。先对FPGA 时序逻辑的正确性以及数据传输状态进行测试,再对频率估计算法的准确性进行测试。

对于控制USB 3.0 进行数据传输的控制时序结果,使用FPGA 内嵌逻辑分析仪对USB3.0 从设备FIFO 的接口时钟PCLK、USB 内监测DMA buffer 状态的标志信号flag_A、FPGA 内16 KB FIFO 的半满信号Half_full、flag_A 信号与Half_full 信号的与信号State_flag、计数器的输出标志count_flag、FPGA 内16 KB FIFO 的读使能信号rd_en 及数据有效标志信号valid、USB 写使能信号进行测试。如图8 所示,Waveform 窗口中显示,PCLK 时钟频率100 MHz,每当USB内DMA buffer 由满至空时,会使监测状态标志信号flag_A 产生上升沿,当等待FPGA 内FIFO 半满时,启动计数同时开始向USB 内部传输数据,当传输数据量为8 KB 时,DMA buffer 被写满,falg_A 拉低,完成一次数据传输。FPGA 写入USB 从机数据时序控制仿真结果如图7 所示,时序状态与设计一致,保证了高速数据传输的可靠性。

图7 FPGA 写入从机数据时序控制测试图

单次数据传输完毕,将传输至PC 机的数据保存至文件内,为后续apFFT 频率估计算法提供充足的、精确的数据源。数据传输界面如图8 所示。

图8 数据传输界面

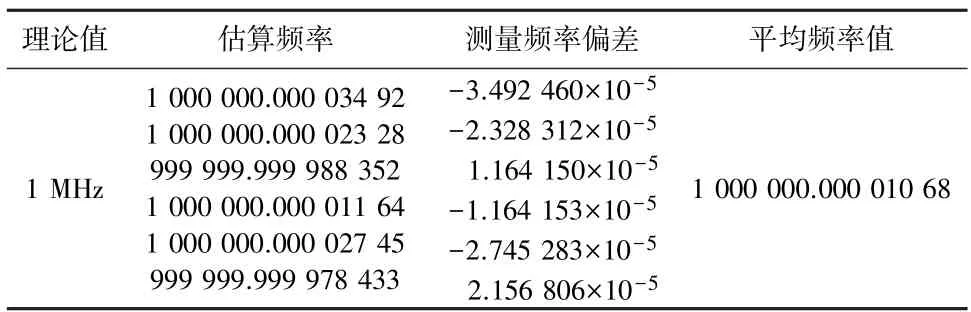

在MATLAB 环境下,通过高精度频率估计算法对多次上传数据进行apFFT 频率估算,设置频率估算数据量s=49 151,采样率fs=40 650 406、apFFT长度N=16 384、时延L=16 384。,多次估算结果如表1 所示,源信号频率理论值为1 MHz,平均频率值为1 000 000.000 010 68 Hz,精度可达小数点后5 位。

表1 频率估计算法估算结果表 单位:Hz

6 总结

本设计提出的用于apFFT 频率估算的USB3.0 高速数据传输系统,采用A/D 转换器将时钟源产生的高稳定度模拟信号转换为16 位并行数据传送主控器至FPGA,同时设计FPGA 执行计数机制,通过控制一次性写入USB DMA buffer 的数据量,来免除对USB局部标志的使用,实现了高速数据传输。设计的基于apFFT 的高精度频率估计算法对回传数据的频率测算精度达小数点后5 位,证明该系统在高速高精度传输及测试环境下具有极高的工程应用价值。