数字电路系统可测性设计(DFT)技术实现方法研究

黄小妹

(江苏省启东市第二中等专业学校,江苏启东,226200)

0 引言

数字电路系统与其自身规模的大小和芯片使用的型号有直接关系。PPC、DSP、FPGA 等是目前市面上使用较多的梳子芯片。大多数芯片采用的都是BGA 封装,这类芯片不但间距小,而且引脚数量多,且导致数字电路系统上可测试的节点距离也逐渐缩小,该问题的出现非常不利用芯片生产和系统检测。对于数字电路系统可测试节点的缩小,使逻辑分析仪器和传统示波器在系统测试方面效率急剧下降,难度急剧上升,为后期的故障检测及定位工作带来了一定难度。为了进一步提高数字电路系统的可测试性和步骤简化性,在该系统的设计过程中就要对该问题就行充分考虑。文章通过与数字电路系统优势的结合,重点对边界扫描原理的结构性、可测性设计在数字系统硬件中的实现做了深入探究。

1 边界扫描测试原理

边界扫描标准是联合测试小组在1985 年制定的检测PCB 和IC 芯片的一个标准,该标准在1990 年被修改成为一个IEEE 的标准,这就是IEEE1149.1。随着科技时代的发展,IEEE1149.1 已逐渐成为测试数字电路系统的主要技术。这种测试标准的使用,不仅能监测数字芯片输入和输出的管脚状态,还对芯片的工作情况和断、开路故障实施精准定位[1]。数字芯片的内部与管脚都是以边界扫描测试为背景,并在此基础上添加扫描单元,最终利用边界扫描单位来监控芯片的引脚状态。通过上述原理对边界单元进行扫描,将边界单元的指定状态从测试数据端口进行输入,然后串行移位到输出引脚,在边界扫描工作状态不变的情况下,采集输入引脚的响应,最后将响应值和输入数值相比对,以此判断芯片之间的故障。数字电路系统中大部分使用的数字芯片在标准选择方面都是符合IEEE1149.1 测试规范的。而PPC、DSP、FPGA 等芯片由于BGA 封装原因的不同,导致物理探针和管脚之间的距离狭窄,无法接触。该情况的出现为数字电路系统边界扫描故障测试带来了困难,也正是因为这种现象的出现,所以在数字电路系统硬件设计过程,必须充分考虑DFT 技术的结构性,为后期简化测试步骤提供有力支撑。

2 可测性设计的实现

DFT 可测试性设计是针对数字电路系统展开的全面测试,是对整个系统结构性的测试,不单单指系统和电路设计过程中的测试问题。数字电路系统芯片之间的互联故障测试主要依靠该系统提供的结构性边界测试标准来实现的。所以,在数字电路系统设计过程中,有关边界测试性的设计,首先,边界扫描器件要满足IEEE1149.1 标准;其次,还要对边界扫描器件的管理连接方法进行完善。比如:PPC、DSP、FPGA 等类型的芯片,在工作状态下也可进行边界扫描,但其设计并不完全符合IEEE1149.1 标准[2]。通过以上阐述,充分印证了要想保障数字电路系统在正常工作状态下实现模式切换自如,还有无法全部实现。

■2.1 串行边界扫描链

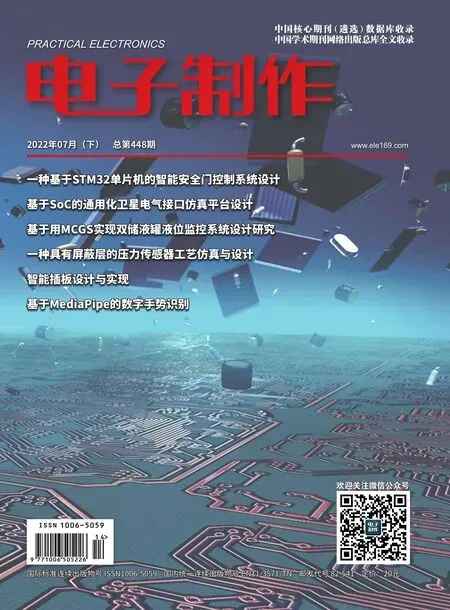

在电路系统中,边界扫描的基础测试是以扫描链路为背景,然后通过并行、串行以及独立路径的连接方式进行测试。串行的方式很简单,不需在模块上增加额外的电路,只需要一个JTAG 接口直接连接到边界扫描控制器上即可。串行方式比较适用于功能模块少的,且各个组件之间的连接关系比较简单的系统。采用这种串联方式可实现最简单的系统级边界扫描测试环路,如图 1 所示。

图1 串行边界扫描链

串行连接方式的边界扫描只适用电路连接简单的系统,如果系统中有链路的芯片损坏或者空槽的问题的出现,那么整个系统的边界扫描链路就会断开,无法继续工作。除此以外,当需要对某个器件进行重复扫描时,这时会进行串行移位操作,该操作非常繁琐,且时间较长。还有一种可能发生的问题就是,进行反复的边界扫描时,部分数据会涉及到手动修改,在手动修改过程中,不仅容易出错,还比较浪费时间。因此,边界扫描在串行连接方式中使用较多,若系统连接较为复杂、器件多的情况下不建议使用[3]。

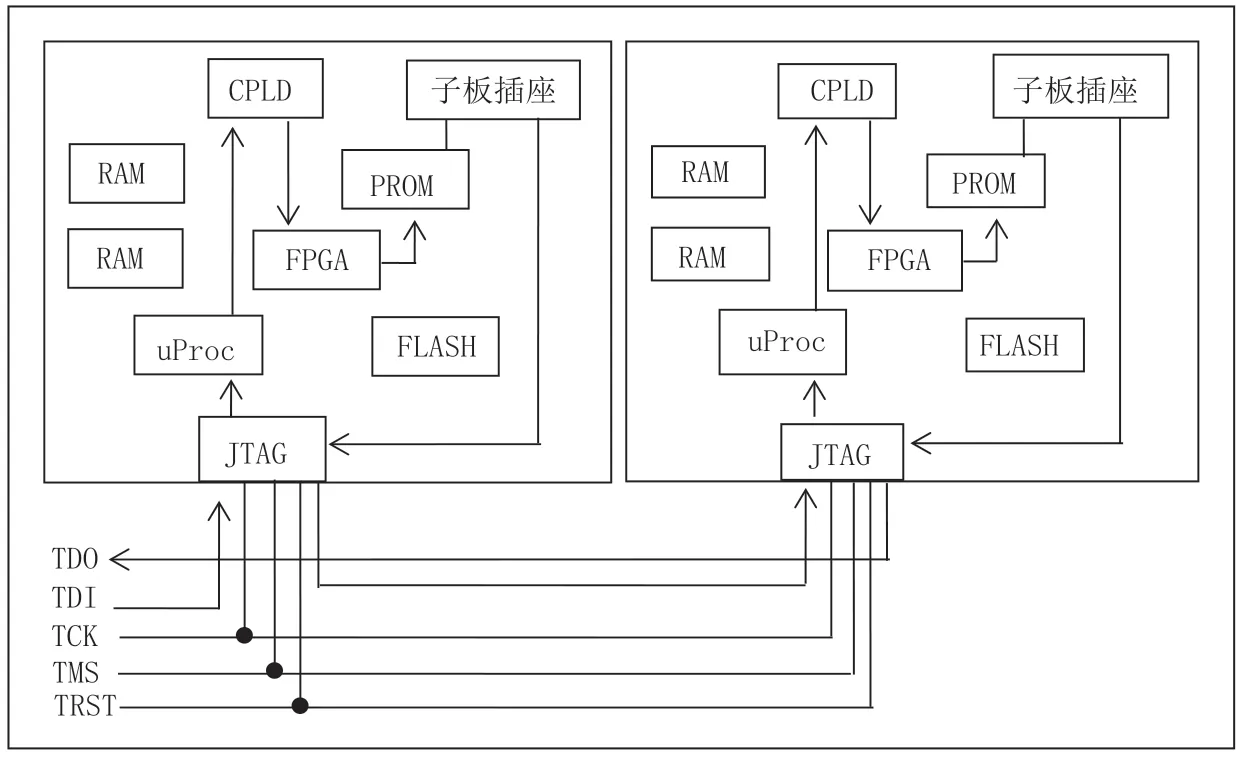

■2.2 并行边界扫描链

并行连接的方式是对链路进行分割管理,这种连接方式明确了链路。简化了芯片对各链路条的管理,简化程序尤其体现在串行移位操作步骤,增加了链路扫描的灵敏性。如图2 所示,在整个数字电路系统中,所有需要处理的模块都是并联在测试总线上,若其中的一个模块有损坏,其他模块也会正常工作,不会受影响。这种并行链路扫描方法是实现稍微有一点复杂,具体操作步骤是将每个通用处理模块都添加扫描芯片。扫描芯片的作用是将通用模块内部的扫描链路有序区分开来,最后按照每个区域规则分配独立扫描链路。

图2 并联连接边界扫描链

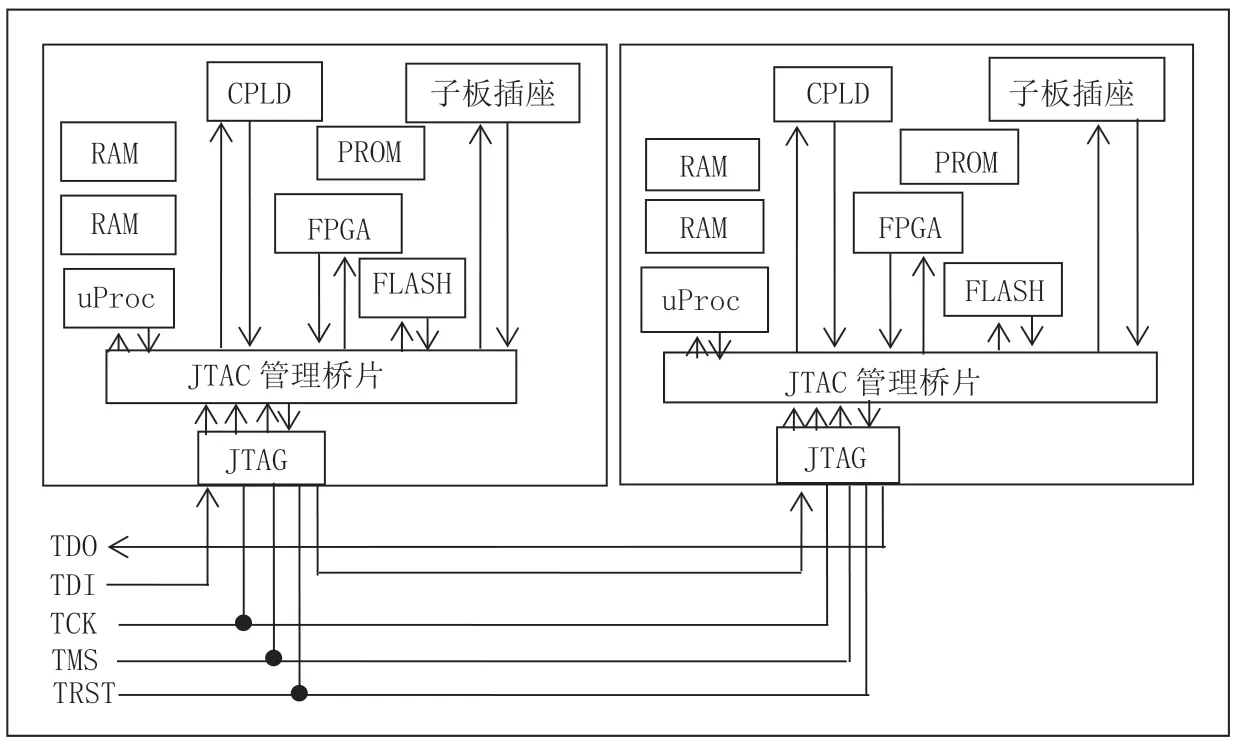

■2.3 独立的边界扫描链

图3 所示为独立边界扫描链,该扫描链的组织方式是为各个模块提供单独的扫描测试,其中每个模块的扫描连接测试口和测试总线都是独立的,这也是实现模块级边界扫描测试的方式之一。独立边界扫描链中,各个模块之间的链路都是相互隔开的,相互配合实现系统级边界扫描测试难度较高,操作复杂。若电路系统规模较大,那么系统内部的模块数量也逐渐增多,那么背板用于测试总线的空间不足,所以这种情况下不太适用改方式进行扫描。

图3 独立边界扫描链

■2.4 兼容性设计

边界扫描的测试和工作模式来回切换,都离不开数字芯片的支持。为了保证数字电路系统各个模块的正常工作,在通用处理模块设计环节,应通过数字芯片的特性,来延伸边界扫描模式和系统工作模式的切换的兼容性设计。

■2.5 JTAG 引脚的兼容性设计

传统的数字芯片在对数字电路系统进行边界扫描时,可在原有的芯片基础上增加额外的JTAG 引脚,而系统需要对增加的引脚进行兼容性设计,使其能够正常的工作。如:TI公司DSP 芯片增加JTAG 引脚,是以IEEE1149.1 标准为基础增加的,而增加的引脚可对系统的工作状态进行切换,同时,实现JTAG 边界扫描。当对DSP 芯片进行仿真试验和正常工作状态进行调试时,两个信号均需向上拉,此时JTAG 接口处是无效的。对于 XILINX 公司的XC4000E/EX/XL 等类型的 FPGA,在添加边界扫描模块时需在系统配置之前进行设计,这是与其他类型芯片不一样的地方[4]。

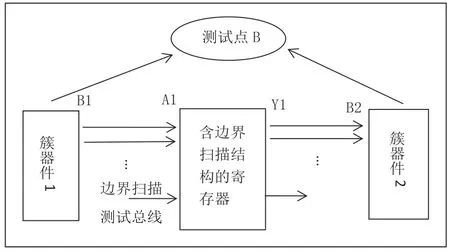

3 簇测试设计

簇(Cluster) 是非边界扫描器件。具体指符合边界扫描标准的数字芯片,其中还包括电子转换器、传输器和缓冲器的数字芯片。簇测试采用的测试方法一般是建立虚拟测试通道。该通道主要是为了给两种器件提供扫描测试通道。这两种分别是不具备边界扫描和具备边界扫描的器件,详情可见图4。

图4 簇测试原理

根据图4 的簇测试原理可见,簇件器1 和2 都与边界扫描器相连接。簇器件1 的输出可以通过边界测试器的测试总线在簇器件2 进行读取。同样的测试方法,簇器件2的输出也可在簇器件1 读取。簇模型是一种软件器件模型,这种模型主要是在边界扫描控制器无法获取被观测网表面簇器件性质而设计的。对于该模型的使用不仅是为了给非边界扫描器件提供信息,还间接增加电路故障测试覆盖率。非边界扫描器件中,有的具有直通特性,比如:驱动器、串联电阻等。鉴于该情况的存在,对于器件逻辑值的输出可以不变。但为了使利用簇模型合并的网表规模达到理想目标,可以充分利用器件的这个特点[5]。

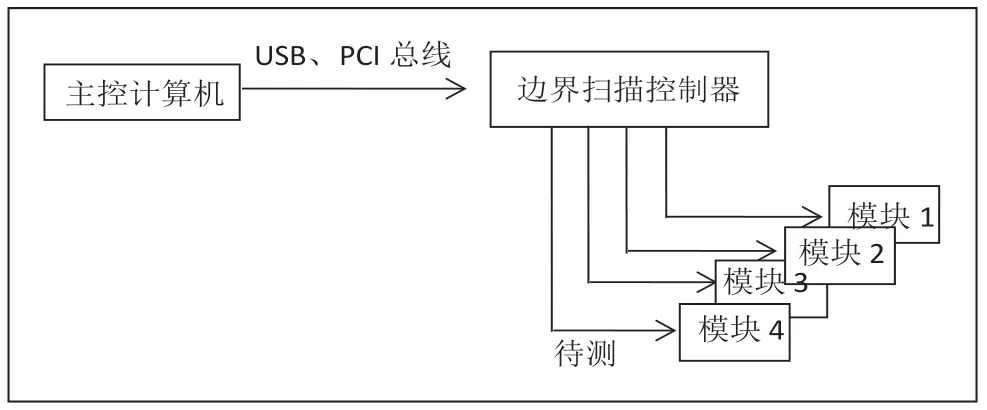

4 实验结果

利用边界扫描测试对数字电路系统进行故障诊断,详情如图5 所示。边界扫描测试系统主要可划分为三部分,分别为主控计算机、边界扫描控制器和待测模块。将待测模块与边界扫描控制器相连接,然后利用USB 和PCI 总线将连接好的边界控制器与主控计算机连接。

图5 边界扫描测试系统

DFT 技术使用前后,在故障覆盖率、定位精准度、时间以及测试范围数据方面的对比都有不同程度的差距。DFT技术在使用后,数字电路系统的测试性幅度大大提升。DFT技术使用前,由于数字电路系统内部边界扫描没有规律和组织性,导致芯片无法实现协同扫描,同时,获取的管脚值也无法进行对比。由于DD R等存储芯片均被当做普通器件,通过控制与之相连的数字芯片的边界扫描寄存器,产生测试序列,选取地址并进行读写内容校验即可,所以采用通用测试程序即可完成存储器测试。

为了验证待测系统在应用DFT 技术后对边界扫描系统实现管脚级故障定位的准确性,可在DFT 设计后的待测系统中某个模块的 DSP 与 FPGA 之间的某条互连线通过跳线设置为短路,利用边界扫描系统进行测试,并与实际情况相比较,观察位置是否相符。个方面研究了超大规模数字电路的结构性可测性(DFT)设计实现方法,并在某大规模数字系统中成功应用了该技术,实现了一键式互连故障诊断及可扫描网络故障精确定位。该技术对边界扫描测试技术在大规模数字电路故障测试中应用具有一定的指导作用。

5 结论

数字电路系统的整体结构较为复杂,集成难度非常高,再加之其使用的芯片间距小和物理探测点少的问题,充分证明了该系统的诊断难度和复杂程度。借助IEEE1149.1 兼容的这类数字芯片在测试方面的优势与数字电路系统的可测性(DFT)技术的配合,可搭建结构简单、诊断精度高的故障测试系统。全文通过扫描链路、模块兼容性等方面对数字电路系统的结构可测性(DFT)设计方法进行延伸分析,并成功的将其技术应用至该系统,进一步实现了对数字电路系统互联障碍的诊断及准确定位。同时,该技术对边界扫描测试技术在数字电路故障测试中还具有一定的指导作用。