基于FPGA 的软件锁相环分析与实现

康 晋,曹 旭,姜育生

(1.杨凌职业技术学院,陕西 杨凌 712100;2.陕西西北民航招标咨询有限公司,陕西西安 710065;3.陕西工商职业学院,陕西西安 710119)

高速数字信号处理和射频混合单板对于时钟的要求很高,时钟的信号精度直接影响到系统的性能。单板的时钟参考来自于BBU,CPU 与接口FPGA互相配合,通过软件锁相环的方式将本地时钟同步到BBU 的参考时钟上,获得一个稳定的10 MHz 参考时钟。

1 概述

系统必须以BBU光纤恢复的时钟作为参考,生成本地的工作时钟,实现整个网络的时钟同步。LMX2306是NS 公司生产的一款单片集成的射频PLL 芯片,由LMX2306 构成锁相环,只需结合高稳定度的本地参考振荡,再外置环路滤波和压控振荡器(VCO)及其他的外围电路即可实现频率的合成。LMX2306 硬件锁相环生成光口的发送时钟61.44 MHz,LMX2306实现鉴相和低通滤波,输出压控电压控制一片VCO,采用时钟驱动器MC100LVEP 实现锁相环的反馈[1-2]。

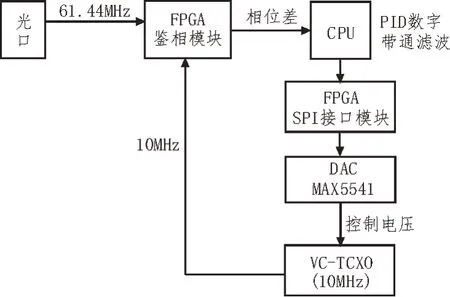

如图1 所示,本地61.44 MHz 时钟为SerDes 模块提供参考时钟和数据发送时钟,SerDes 模块从基带传来的光接口数据中恢复出153.6 MHz 并行数据时钟,与TCXO 的输出10 MHz 时钟进行锁相,得到一个稳定的10 MHz 时钟,其准确度优于0.05 ppm,并将该10 MHz时钟作为参考时钟进行分发。AD9516与此10 MHz时钟生成中频电路的工作时钟122.88 MHz,完成去抖动后分配给AD、DA 芯片,并提供给FPGA 最小系统使用[3-4]。

图1 系统时钟

2 10 MHz时钟软锁

FPGA 器件选用Xilinx 公司生产的Virtex-5 系列中的XC5VLX50T,内置的SerDes 模块可以实现光口高速串行信号到并行信号的转换,同时支持CPRI 和OBSAI 协议[6-7]。

如图2 所示,SERDES 光模块从BBU 发送过来的光信号中恢复出153.6 MHz 的数据时钟,单板上的VC-TCXO 器件产生一个10 MHz 的本地时钟。FPGA 对两路时钟分频到1.6 kHz 后进行鉴相处理,并把鉴相值上传给CPU,CPU 的软件锁相进程通过PID 算法将鉴相差值转换为控制电压,通过DAC MAX5541 控制VC-TCXO 进行频率的校准。当FPGA 鉴相的相位差值小于某特定阈值并且持续稳定一段时间后,则可以认为本地的VC-TCXO 时钟已经和来自BBU 的光信号时钟同步[8-9]。

图2 10 MHz时钟软锁的原理图

3 FPGA鉴相

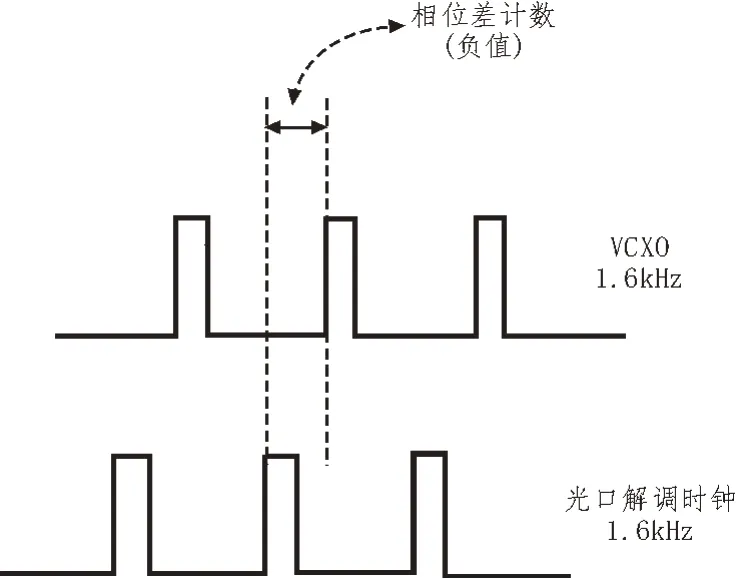

FPGA 首先将这两路时钟分别分频到1.6 kHz,然后用80 MHz 时钟的上升和下降沿对两路时钟的相位差计数。在锁定状态之前相位差是不确定的,所以相位差的范围是0 到一个周期。CPU 从FPGA的寄存器中读出80 MHz 时钟的鉴相计数值,当VCTCXO 时钟超前光口解调时钟半个周期以内时,CPU认为相位差是正值,相位差为正值时的时钟相位如图3 所示。当VC-TCXO 时钟超前光口解调时钟大于半个周期时,CPU 将鉴相计数值减去一个整周期的80 MHz 时钟计数值,得到一个负值的相位差[10-11],相位差为负值时的时钟相位如图4 所示。

图3 相位差为正值时的时钟相位

图4 相位差为负值时的时钟相位

CPU 从FPGA 获得相位差后,利用一个PID 算法将相位差转换为要写入DAC MAX5541 的控制参数,DAC 产生控制电压,从而调整VC-TCXO 的输出时钟频率。PID 算法的公式如下:

其中,P、I和D分别为控制参数,P为比例系数,I为积分系数,D为差分系数,V_K为控制电压的压控斜率,p(n)为当前从FPGA 读取的鉴相差,p(n-1)和p(n-2)分别为上次和上上次从FPGA 读取的鉴相差,Δp(n)=p(n)-p(n-1),Δp′(n)=Δp(n)-Δp(n-1)。经过PID算法计算得出的ΔV(n)就是需要写入DAC 的控制电压[12-13]。

当CPU判断从FPGA读出的鉴相差的绝对值小于某一特定阈值并且持续稳定一分钟后,则会对10 MHz时钟锁定的标志位置位。而一旦鉴相差大于这一阈值,则会进行复位操作。由于外在和内在环境的不稳定,单板的时钟必须时刻与BBU 时钟保持锁定,所以CPU 的鉴相进程在随单板上电初始化启动之后,会一直工作下去[14-15]。

4 软件接口

1)数据结构:PHASEPAR,用来存储鉴相进程不同工作模式时的参数。代码如下:

2)函数功能:初始化LMX2306。代码如下:

参数:wChannel:通道号

返回值:0 操作成功;非0 操作失败

3)函数功能:初始化光网络,该函数首先向控制VCO 的DA 芯片写入初始值,之后启动鉴相进程。代码如下:

5 软件锁相流程

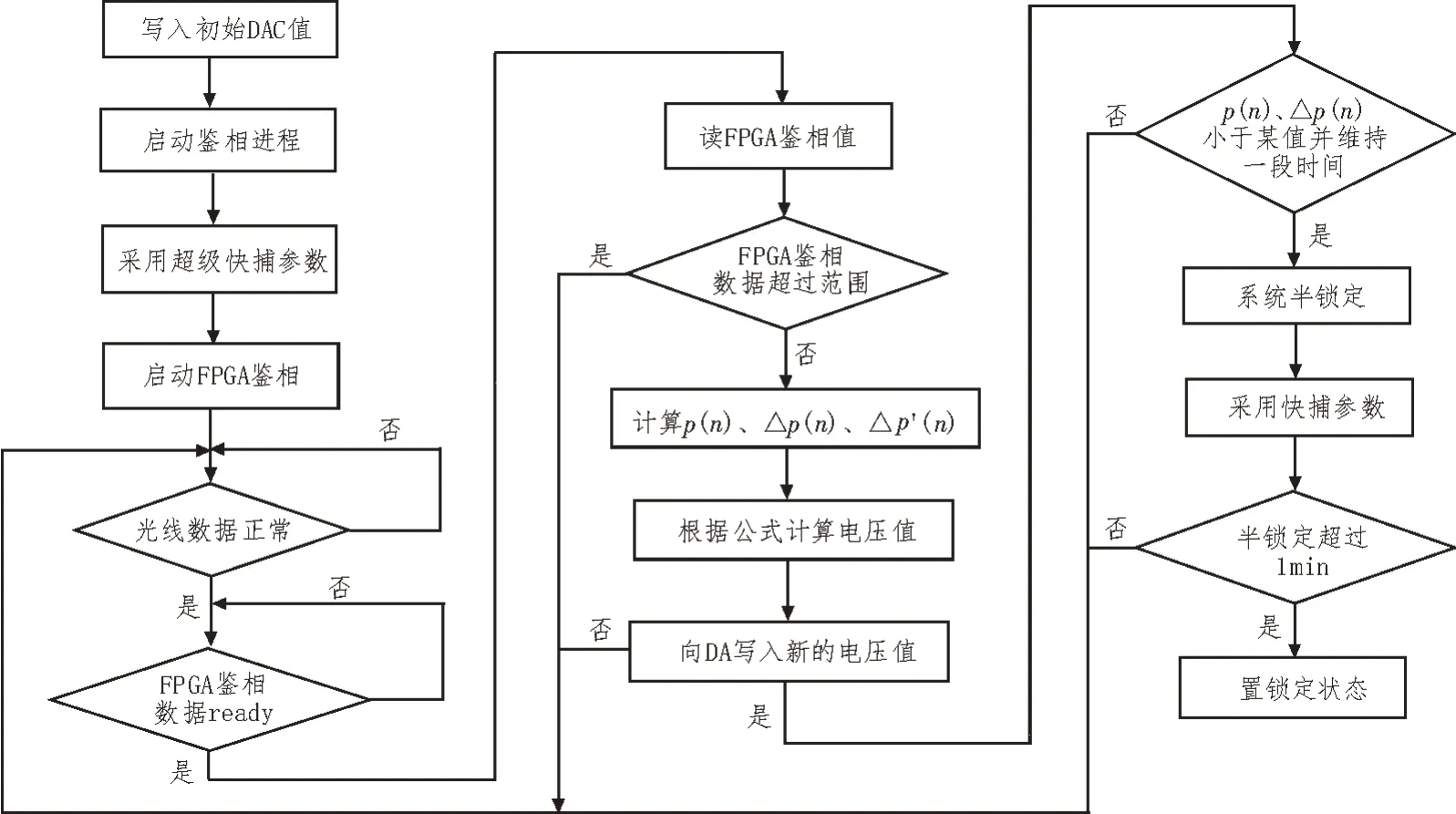

软件锁相进程的流程图如图5 所示。

图5 软件锁相进程的流程图

整个流程可以看做是一个闭环的反馈系统,PID算法相当于一个数字滤波器。软锁进程根据从FPGA 读出的鉴相差,不断对本地VC-TCXO 进行校正,从而使本地时钟与BBU 解调时钟相耦合,达到锁相的目的。在刚开始启动锁相进程时相位差比较大,采用粗调的超级快捕参数,可以加快本地10 MHz时钟趋近于BBU 时钟的步伐;当相位差变小后,由于超级快捕参数的调整幅度较大,本地时钟不容易稳定下来,所以采用调整更为精细的快捕参数,最终使本地10 MHz 时钟趋于稳定[16-17]。

6 结束语

RRU 的本地时钟必须同BBU 的时钟系统实时同步,对RRU 的性能指标影响很大。根据本地时钟10 MHz 和从光接口数据中恢复出153.6 MHz 进行FPGA 鉴相,通过PID 算法实现软件锁相,获取稳定的10 MHz 时钟信号,分发给各功能单元使用。该文分析了时钟同步的过程、软件锁相的原理、算法,给出了接口函数以及软件流程,该软件锁相的方法已经在4G 中广泛应用,对5G 无线系统仍然有一定的借鉴意义。