一种高稳定快速响应的LDO 设计

闫冬冬,唐 威,王甲柱,张 森

(西安邮电大学 电子工程学院,陕西 西安 710121)

低压差线性稳压器(Low-Dropout Regulator,LDO)作为电源管理系统的重要电路之一,具有低成本、低功耗、体积小、高精度等特点,成为应用最广泛的芯片之一[1]。5G 时代已经到来,移动通信设备快速迭代,IC 系统的时钟频率显著提高[2],因此,作为电源管理系统的LDO 常需要驱动超高速的数字集成电路,其负载电流往往会在极短的时间内变化[3-4]。这种变化要求LDO 电路对负载电流跳变引起的瞬态变化进行快速响应,并在不同负载下都有良好的频率稳定性[5-6]。

针对这些问题,李旭等[7]提出了一种增强型AB跟随器以增强LDO 的瞬态响应,但此结构是以牺牲过冲电压为代价,在负载跳变时输出电压会有较大波动;Shi 等[8]利用比较器与锁存器实现了LDO 的低功耗与快速响应,但过冲电压较大,且需要占用的芯片面积较大,不利于芯片的高度集成。

本文提出了一种基于零极点追踪电路与摆率增强电路的高稳定快速响应LDO。使用零极点追踪电路进行采样并动态地对电路进行频率补偿,同时通过摆率增强电路(Slew Rate Enhancement Circuit,SRE Circuit)采样负载电流的变化,采样电流经过电流镜复制之后为功率管的栅极寄生电容快速充放电。以此实现高稳定性和较大的带宽,并提升了整体LDO 的瞬态响应。

1 传统LDO 结构

传统LDO 结构如图1 所示,该电路由误差放大器、缓冲器(源跟随器)、功率管MP、反馈网络、基准输入构成[9]。其中Vref与Vfb分别为基准电压与反馈电压,RESR为输出电容Cout的等效寄生电阻,RL为负载电阻,Roa和Rbuf分别为误差放大器和缓冲器的等效输出阻抗,Cbuf和Cpar分别为缓冲器和功率管的栅极寄生电容,CC为密勒电容。

图1 传统LDO 电路图Fig.1 Traditional LDO circuit diagram

对于LDO 的频率稳定性,基于误差放大器有较大输出阻抗的特性,Roa与Cbuf在A 点会产生一个低频极点PA并影响环路的频率稳定性[10],该极点表示为:

由于Rbuf极小,在B 点产生的极点PB处于高频,不会影响电路的频率稳定性。当电路处于轻载时,RL与MP 的输出阻抗较大,会在功率管的输出结点产生第二个低频极点Pout。当电路存在两个低频极点时,输出会因相位裕度过低而产生振荡[11]。传统LDO 通常引入密勒电容CC对电路进行补偿,该电容将PA推向低频,从而使其成为主极点,并将Pout推向高频[12],改善环路的稳定性。但是,该结构会减小带宽,并因为在高频时CC形成前馈通路,产生一个右半平面零点表示为:

式中:gmp为MP 的跨导。在重载情况下,gmp较大,若该零点进入带宽内,则会带来更大的相位滞后,使稳定性下降。

对于LDO 的瞬态响应,考虑到瞬态响应与带宽呈正相关,且密勒补偿增大相位裕度的同时减小了带宽,所以该结构增大了负载电流跳变时的过冲电压与稳定时间[14-15]。传统LDO 仅使用负载电容的充放电过程改善电路的瞬态响应,若Cout较小,则瞬态响应较差;若Cout较大,则不利于芯片的高度集成。因此,需要通过其他技术实现高稳定性和快速瞬态响应。

2 本文设计的LDO 电路

2.1 电路结构和原理

针对传统密勒补偿产生左半平面零点并减小带宽的问题,本文基于零极点追踪补偿与摆率增强技术改进了传统LDO 结构,如图2 所示,使用零极点追踪电路替换密勒电容,并在功率管栅端加入摆率增强电路。通过前者增大电路的相位裕度与带宽,通过后者实现快速瞬态响应。

图2 本文设计的LDO 电路拓扑图Fig.2 Proposed circuit topology diagram of the LDO

图3 为本文设计的LDO 电路图,其中A1为反向增益误差放大器,M1、M2 为源跟随器,Vb1为偏置电压,为其提供合适的偏置电流,为了得到更大的带宽,功率管选择高增益的PMOS 管。M5~M9、C1、R1、R2构成零极点追踪电路,M10~M22、R3、R4构成SRE 电路。

图3 本文设计的LDO 电路图Fig.3 Proposed circuit diagram of the LDO

LDO 的输出端Vout接M3 的栅端并在其源端产生NMOSFET 阈值电压的电位差,该信号又经过M7 在其源端产生PMOSFET 阈值电压的电位差,最终输出至采样管的漏端。此时M6 的漏端电压与功率管相似,同时其输入与功率管栅极相连,此结构令M6 成为采样管并采样负载电流的变化。该电路的优点是Vout接直流阻抗无穷大的MOS 管的栅极,不会影响LDO 的输出精度。考虑到在标准CMOS 工艺中,PMOSFET的阈值电压大于NMOSFET,采样管的漏端电压略小于Vout,不能够进行精确采样,因此在其源端串联小电阻R1,通过电阻分压降低采样管的VGS,提高采样电流与负载电流的匹配度。为了进一步提高采样精度,为其并联一路由M5 提供的偏置电流,补足因信号传输损失的电流。由于该偏置电流较小,不会引入过大的静态功耗。

M11 的工作原理与M6 相同,采样电流经过两次电流镜复制至M17。M18 为开关管,栅极接M1 的栅极,当电路为轻载时,功率管与源跟随器的栅端均为高电位,开关管关断,采样电流Is经过两次电流镜复制至M22;当电路为重载时,F 点电压降低,Is流向有较大宽长比的开关管。

2.2 稳定性分析

对于本次设计,当LDO 负载电流小于10 mA,即LDO 为轻载时,功率管MP 的输出阻抗和RL较大,输出极点进入带宽内部。此时,包括第一级运放的输出极点在内,带宽内至少存在两个极点,需要引入一个低频零点进行补偿。

由于流过采样管M6 的采样电流极小,该电流流过M8 并在其栅端产生较小的栅压,同时该栅压作用于M9 上,使其进入亚阈值区。已知MOSFET 处于亚阈值区时内阻极大,因此M9 的内阻ro9与C1产生一个低频零点Z1:

此时Z1追踪并补偿了处于低频的输出端极点Pout,使电路保持足够的相位裕度。当负载电流增大至100 mA,即再次转为重载时,M9 的栅压变大并进入深线性区,ro9急剧减小,Z1被推至带宽外,不会因为电路处于重载时相位裕度过大而影响整体电路的响应时间。

为了分析整体电路的稳定性,绘制小信号电路图如图4 所示,其中gm1、gm2分别为误差放大器、源跟随器的等效跨导,Rout为功率管的输出阻抗与RL的并联值。因为Rbuf极小,功率管栅端极点的位置处于单位增益带宽的十倍频之外,所以在小信号分析中忽略该极点对系统带来的影响。

图4 LDO 小信号电路图Fig.4 Proposed small signal circuit diagram of the LDO

基于以下两点假设来讨论该运放的传输函数:(1)C1和Cout远大于Cbuf;(2)Roa、Rout和ro9远大于RESR。该运放的传输函数为:

由式(4)可知,该系统共有三个极点和两个零点,经过零点对极点的补偿,仅剩一个极点P-3db留在带宽内,表示为:

利用Roa较大的特性,本文使用零极点补偿电容C1将第一级放大器的输出端固定为主极点,且该极点接近原点,因此移动的Pout不会与P-3db重合而影响频率稳定性。为了该追踪补偿的精度,C1容值至少为10 pF。

综上所述,相较于传统LDO 电路在轻载时的稳定性远低于重载,本文基于零极点追踪补偿电路提出的LDO 使电路成为单极点系统,保证在电路处于轻载与重载时都有足够的相位裕度和带宽。

2.3 瞬态响应分析

LDO 电路瞬态响应的曲线如图5 所示,其中ΔV1与ΔV2分别为下冲电压与过冲电压,即Vout在负载跳变时的最大电压变化量,Δt1与Δt3分别为下冲与过冲的响应时间,Δt2与Δt4分别为下冲与过冲的稳定时间。

图5 LDO 瞬态响应曲线Fig.5 LDO transient response curve

环路的下冲/过冲电压ΔV与响应时间Δt表示为:

式中: BWcl为系统的闭环带宽;tsr为LDO 对Cpar充/放电的时间;Isr为功率管前级运放对Cpar充/放电的电流。根据式(11)可知,增大BWcl或Isr均可减小Δt和ΔV并改善环路的瞬态响应(Δt2与Δt4的大小亦由BWcl和Isr共同决定)。

在2.2 节的分析中,通过零极点追踪电路保证了足够大的带宽,但对Isr并无影响。因此,本文通过摆率增强电路来增大功率管的驱动能力,以此进一步增强电路的瞬态响应。

当电路由轻载转为重载时,功率管栅压减小,需要对功率管的栅极寄生电容进行快速放电。由于摆率增强电路的存在,电路对Cpar的放电电流Isr-并不是固定的,表示为:

式中:IM1和Iboost分别为图3 中流过M1 的电流和采样电流;x是一个恒定的镜像比,由M13 和M14 的尺寸决定,表示为:

为了更快地响应负载电流的变化,M13 与M14 均设置较大的宽长比,以保证采样电流的灵敏度。

通过增大Isr-,加之较大的带宽,本文提出的电路在轻载转为重载时具有较好的瞬态响应,即ΔV1、Δt1与Δt2都较小。

当电路由重载转为轻载时,功率管栅压增大,需要对功率管的栅极寄生电容进行快速充电。此时M22打开,电路对Cpar的充电电流Isr+表示为:

式中:Ib1和IM22分别为流过M2 和M22 的电流。因为增大了Isr+,所以电路在重载转为轻载时也具有较好的瞬态响应。

考虑到负载电流与Isr会随着电源电压升高而略微增大,当电路为高压输入时,负载跳变对输出电压的影响会更小。

综上所述,相较于传统LDO 电路仅靠外部负载电容充放电改变负载瞬态响应,本文基于摆率增强电路提出的LDO 通过采样负载电流的变化自动为功率管的栅极寄生电容充放电,极大地改善了电路负载跳变对输出的影响。

3 数据仿真及分析

基于0.18 μm CMOS 工艺,采用Cadence 软件对电路进行Spectre 仿真。基准电压为1.1 V,负载电容为100 pF,负载电流的最大值与最小值分别为100 mA和1 mA。

图6 为LDO 环路稳定性仿真曲线。输入电压为3 V,分别取负载电流的边界值进行仿真。当负载电流为1 mA 时,低频增益为106 dB,相位裕度为89.6°,带宽为1.14 MHz;当负载电流为100 mA 时,低频增益为97.6 dB,相位裕度为94.7°,带宽为1.84 MHz。

图6 LDO 环路的稳定性仿真曲线Fig.6 Stability simulation curves of the LDO loop

图7 为LDO 环路稳定性在各工艺角下的仿真曲线。输入电压为3 V,在负载电流为10 mA 下进行仿真。其中,tt 工艺角下低频增益为104.6 dB,相位裕度为92.7°,带宽为1.32 MHz;ss 工艺角下低频增益为94.6 dB,相位裕度为99.1°,带宽为0.44 MHz;ff工艺角下低频增益为110.6 dB,相位裕度为81.4°,带宽为3.13 MHz,fs 与sf 工艺角各项参数与tt 工艺角接近。

图7 LDO 环路在各工艺角下的稳定性仿真曲线Fig.7 Stability simulation curves of the LDO loop for each process

综上所述,因为零极点追踪电路对电路的补偿,本文所设计LDO 在各负载与各工艺角下均有良好的环路稳定性。

图8 为LDO 输出的负载瞬态响应曲线,输入电压为2.3 V,输出电压稳定时为1.8 V,负载电流均在1 μs 内进行重载与轻载的切换。由图8 可知,采用本文提出的SRE 电路,LDO 电路的负载瞬态下冲电压与过冲电压的稳定时间分别为1.24 μs 与1.52 μs。若不采用本文提出的技术,在相同的仿真条件下,则下冲电压与过冲电压的稳定时间分别为1.87 μs 与1.98 μs。在输出过冲电压与下冲电压的减小幅度方面,采用本文提出的SRE 电路的输出相较无SRE 电路的输出,下冲电压减小了12 mV,下降了20.3%;过冲电压减小了15 mV,下降了27.4%。

图8 负载瞬态响应曲线Fig.8 Load transient response curves

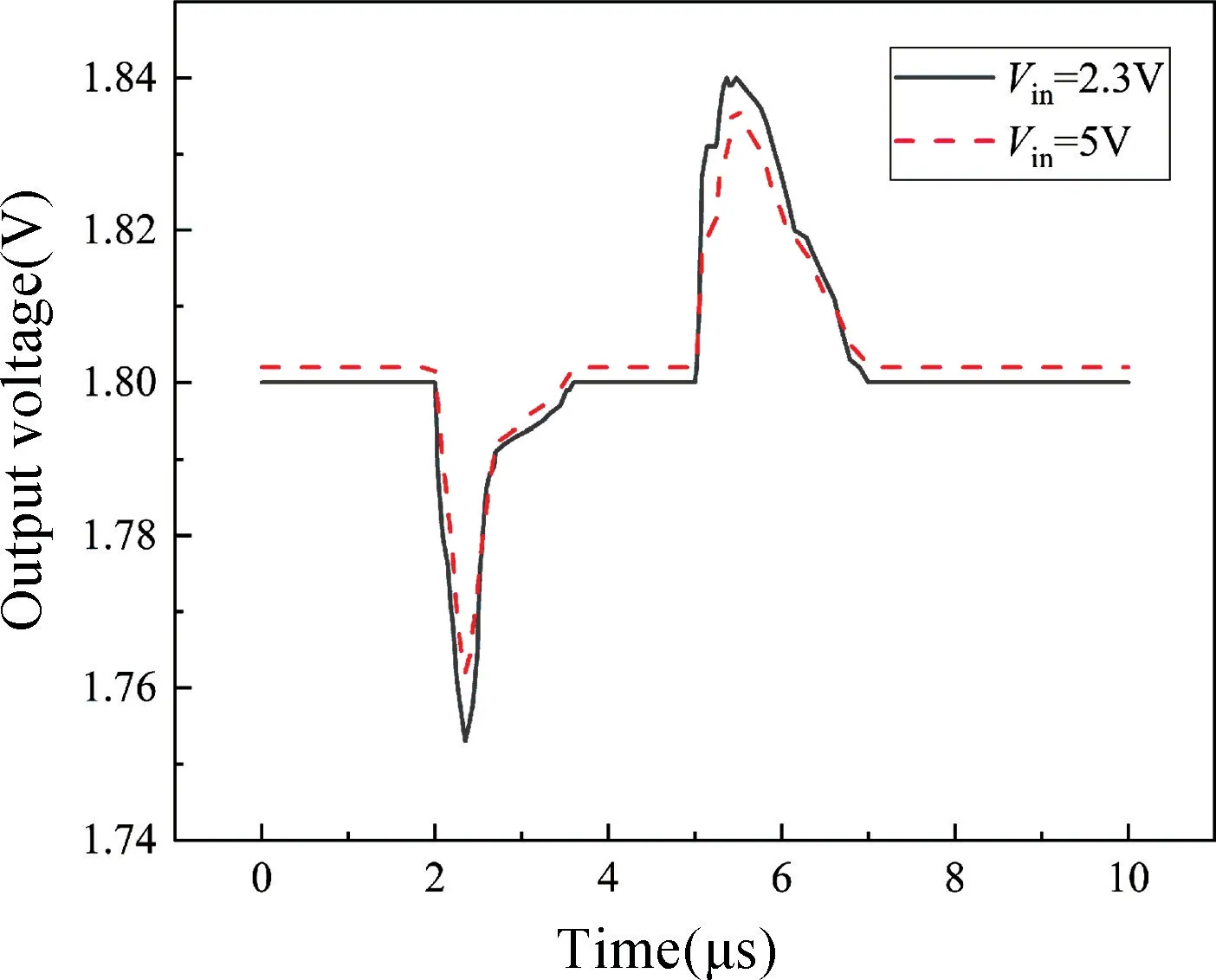

图9 为不同输入电压下的负载瞬态响应曲线,电源电压为最大值5 V 时的下冲电压比低电源电压2.3 V 的下冲电压减小了9 mV,过冲电压减小了4 mV,高压输入时的负载电流会略大于低压输入,因此高压输入有更好的负载瞬态响应。

图9 不同输入电压下的负载瞬态响应曲线Fig.9 Load transient response curves at different input voltages

图10 为LDO 输出的负载瞬态响应在各工艺角下的曲线图,仿真条件与上文相同。由图可知,在各工艺角下负载跳变的下冲电压与过冲电压稳定时间基本一致,且该电压最大值均小于50 mV。

图10 负载瞬态响应在各工艺角下的仿真曲线图Fig.10 Simulation curves of load transient response for each process

图11 为负载电流为30 mA 时,LDO 输出的电源抑制比(PSRR)在各工艺角下的曲线图。由图11 可知,各工艺角在1 kHz 的PSRR 均大于78 dB。

图11 PSRR 工艺角仿真曲线图Fig.11 PSRR process angle simulation curves

图12 为输出为1.8 V 时LDO 输出由1 mA 至100 mA的负载调整率,输出变化量为121.6 μV,负载调整率为0.001 mV·mA-1。因为LDO 的负载调整率与增益成正比,各负载下较大的增益均可得到较好的负载调整率。

图12 负载调整率仿真图Fig.12 Simulation diagram of load adjustment rate

表1 为本文的LDO 性能仿真结果与近年文献的数据对比。从表1 可以看出,本文的LDO 在瞬态响应与PSRR 方面优势更大。

表1 与其他文献的性能对比Tab.1 Performance comparison with other literatures

4 结论

本文基于0.18 μm CMOS 工艺,设计了一种高稳定性和快速瞬态响应的低压差线性稳压器。在传统LDO 的基础上引入零极点追踪电路和摆率增强电路,同时保证了电路的稳定性与负载瞬态响应。经仿真验证,LDO 整体电路全负载与各工艺角的相位裕度均大于80°,达到了高稳定性的设计要求;当负载电流跳变时,下冲电压与过冲电压均小于50 mV,最大过冲稳定时间为1.52 μs,且各工艺角下的下冲电压与过冲电压均小于50 mV,达到了快速瞬态响应的设计要求,满足了需要负载电流在极短时间内变化的超高速集成电路需求。