基于实时频谱分析的便携式射频通信干扰器设计

翟建龙,郭全全,娄贵鑫,李鹏月

(1.中国人民武装警察部队研究院,北京 100012;2.天津锘华仪器科技有限公司,天津 300309)

0 引言

随着通信技术的快速发展,未来战争已经演变成一种电子对抗的战争。在电子对抗中,为了防止电子干扰,跳频通信技术凭借其优秀的抗干扰、低截获率、抗衰落等优点,被广泛的应用[1-8]。如何快速简便识别并干扰高速跳频信号成为了电子对抗的关键点。

电子干扰按照干扰生成的方式分为有源电子干扰以及无源电子干扰[9]:有源电子干扰是通过发射或传递某种特定形式的电磁波,扰乱或者破坏使敌方的电子设备以及电子系统。干扰信号的功率、载频和干扰样式是根据被干扰的电子设备的类型、技术体制、工作频率等进行选择的。无源电子干扰是用一些本身不能发射电磁波的器材,例如反射器、箔条或电波吸收体等,将敌方电子设备发射的电磁波反射或吸收掉,削弱或破坏其效能[10]。在通信干扰中,有源电子干扰因其主动性和灵活性被广泛应用。

目前通信干扰器产品大部分采有源电子干扰技术,并被广泛应用于电子对抗领域[11-12],干扰器通过识别敌方无线通信的频点,来对其施加干扰电磁波使敌方通信系统瘫痪或短暂的失效,从而实现电子干扰的目的[13]。传统的干扰器大都采用独立的仪器设备通过系统集成来实现,具有系统复杂、体积大、功耗高等缺点,无法实现快速布设,不具备机动性和灵活性,无法适应当今局部小范围冲突和反恐、防暴的需要[14]。基于以上现状和需求,有必要设计一种模块化、小型化的便携式射频通信干扰器,以满足各种军用与警用情境下的快速对抗需要。

文中提出了一种基于实时频谱分析和实时信号合成的模块化、小型化、便携式的射频通信干扰器的设计方法,并成功研制出干扰器样机,已被应用在某部队的通信训练中。

1 系统结构及原理

文中所设计的射频通信干扰器是基于现场可编程门阵列中间层板卡(FMC,FPGA mezzanine card)接口扩展的虚拟仪器(FXI,FMC extended instrument)规范进行设计的。FXI是一种模块化仪器设计规范,该规范在FMC信号定义的基础上,针对虚拟仪器领域的应用定义了FXI模块的结构尺寸和FXI接口的专有信号组。由于借鉴了FMC的模块化思想,该种设计提高了虚拟仪器模块的功能密度,从而时基于FXI规范设计出的射频通信干扰器具备便携性、模块化和轻量化的特点。文中射频通信干扰器主机结构为加固笔记本形式,单屏设备总重量不超过6公斤。另外在实际使用中,可针对短波通信、超短波通信和微波通信扩展不同的模块,来实现对短波、超短波和微波通信的干扰。

文中射频通信干扰器主要由主机、天线和功率放大器组成,如图1所示。其中主机为一台三屏加固笔记本,由侦测和干扰两部分组成,侦测和干扰组件分别位于设备的两侧。侦测部分的外围组件为多个接收天线,用于在短波、超短波和微波频段进行循环监测,发现频段内的频率使用情况。发送部分的外围组件由功放及发射天线组成,由主机产生的干扰信号经过功率放大器进行放大,然后通过发射天线发送出去,对跟踪到的信号进行干扰。

图1 射频通信干扰器组成

射频通信干扰器实物布设图如图2所示。

图2 射频通信干扰器布设图

2 设计方案

射频通信干扰器内部同时集成频谱仪和射频信号发生器,频谱仪和射频信号发生器通过FXI信号组紧密耦合,可实现对跳频信号的快速跟踪,从而实现对快速跳频信号的无缝跟踪干扰。

通常跳频信号的干扰有瞄准式、阻塞式和跟踪式等不同形式[16-21]。瞄准式干扰也叫单频干扰,是指干扰信号的中心频率与被干扰信号的频率重合,或干扰信号和被干扰信号频谱宽度基本一致。瞄准式干扰的频谱较窄,干扰功率相对比较集中,所有能量全部用来压制敌方的某一通讯信号,功率利用率高,干扰效果好[22]。但是此种干扰方式要求干扰信号与被干扰信号有较高的频率重合度,从而对干扰器的性能提出了较高要求,而且要有引导干扰频率的侦察部分。瞄准式干扰通常用来压制对方重要的指挥性通信。阻塞式干扰是一种宽频带干扰,它可以对某一频段内的全部信号进行干扰。其较宽的干扰信号频谱,通常能覆盖被干扰无线设备的整个工作频段,同时对该频段内的所有通信信号进行压制,因此,也叫多频干扰。这种干扰无需频率重合,也无需引导干扰的侦察设备,相对比较简单[23]。通常用于压制地方战术分队的无线电通信。跟踪式干扰通常是先对截获的信号进行分选、分析,确定要干扰的对象,引导干扰器发射出瞄准式干扰。此干扰方式对跳频通信产生的威胁很大,这就需要通信方能以尽可能高的速率进行跳频,以减少干扰方在每跳上的干扰时间百分比[24]。

文中所设计的射频通信干扰器可实现瞄准式、阻塞式和跟踪式三种干扰方式,其中瞄准式干扰和阻塞式干扰不需要频谱仪模块跟踪被干扰信号,而跟踪式干扰需要频谱仪模块来跟踪被干扰信号。针对瞄准式干扰,信号发生器模块在设定的频率点上产生指定模式的干扰信号;针对阻塞式干扰,信号发生器模块在两个频率点之间的频带内施加宽频带干扰信号。在跟踪干扰过程中,频谱仪需要实时跟踪被干扰信号的频频信号,并引导信号发生器在所跟踪的频率点上施加干扰信号。

2.1 系统框图

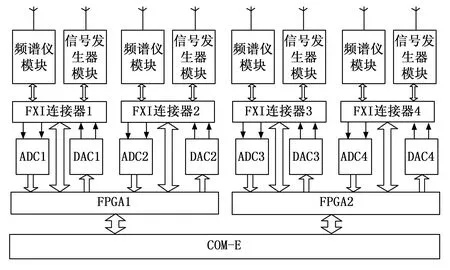

射频通信干扰器主机内部由载板和子板构成,系统框图如图3所示。载板上设计有大规模现场可编程门阵列(FPGA,field programmable gate array)、高速模数转换器(ADC,analog to digital converter)和高速数模转换器(DAC,digital to analog converter)。大规模FPGA用以通过快速傅里叶变换(FFT,fast fouriertransform)算法来跟踪射频信号,并通过反向快速傅里叶逆变换(IFFT,inverse fast fouriertransform)算法来合成各种模式的射频干扰信号,ADC用以采集频谱仪子板传送过来的模拟基带信号,DAC用以合成各种模式的基带干扰信号。频谱仪子板用以实现射频信号下变频,将射频信号变换到DC~40 MHz的基带信号,并将基带信号送至载板上的高速ADC。射频信号发生器子板用以实现射频信号上变频,将DAC输出的DC~40 MHz的基带干扰信号变换到指定频点上。

图3 干扰器硬件功能框图

2.2 FXI信号组

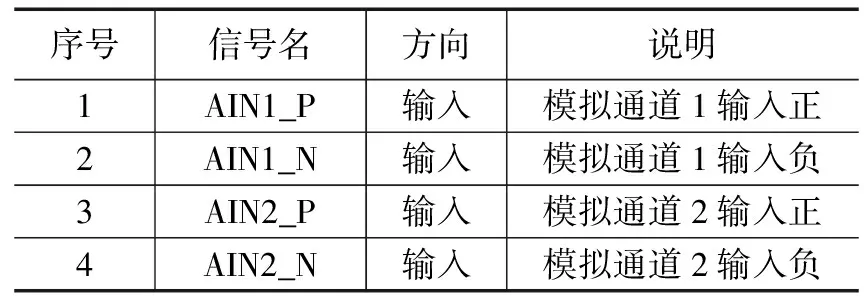

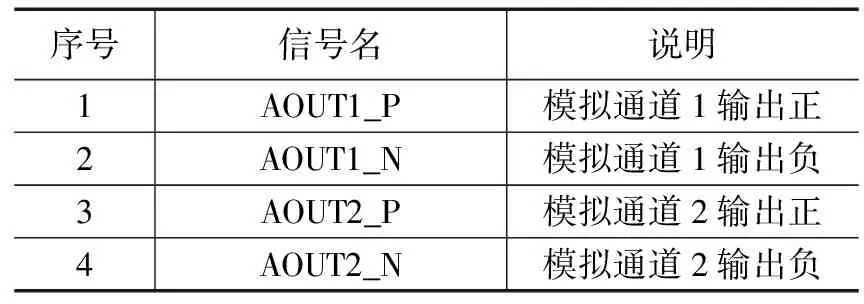

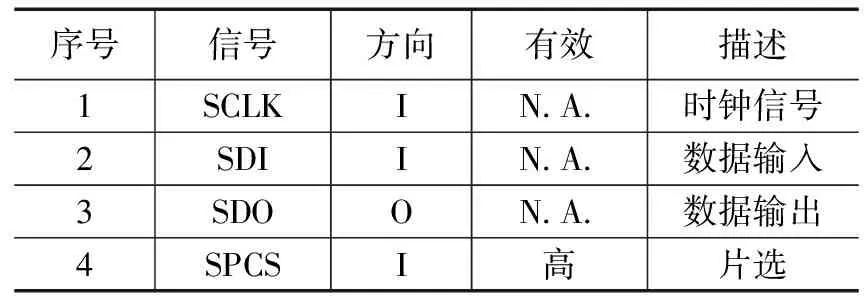

在文中射频通信干扰器的设计中,用到的FXI信号组定义如表1~表3所示。

表1 高带宽模拟量输入接口

表2 高带宽模拟量输出接口

表3 SPI接口信号

参考表1~3,载板上的ADC对FXI连接器上的两路高带宽模拟量输入信号采样,将采样数据送至FPGA,通过FPGA的算法逻辑对ADC的两路模拟量采样数据作时域或频域分析。载板上的DAC合成两路高带宽模拟量信号并送至FXI连接器,由射频信号发生器子板进行上变频,将基带信号加载到射频载波上。FXI连接器上的串口外设接口(SPI,serial peripheral interface)信号组用以配置频谱仪子板和信号发生器子板中的自动增益控制(AGC,automatic gain control)和可变增益控制(VGC,variablegain control)的工作参数。

3 系统硬件设计

3.1 系统硬件功能框图

射频通信干扰器硬件设计功能如图4所示。

3.2 载板设计

3.2.1 设计说明

图4中,射频通信干扰器载板采用基于X86系列处理器的计算机模块标准(COM-E,computer-on-module express)设计,在载板上集成2片大容量FPGA芯片、4片高速ADC和4片高速DAC。COM-E模块通过PCIe总线来控制FPGA、访问FPGA内部资源。FPGA通过低压差分信号(LVDS,low voltage differential signaling)接口连接ADC和DAC芯片,并通过串行外设接口(SPI,serial peripheral interface)总线来配置ADC和DAC。

载板上设计有3个低引脚数(LPC,low pin count)的FMC连接器和一个高引脚数(HPC,high pin count)的FMC连接器,每个FMC连接器可通过堆叠设计,连接两个FXI板卡。在设计中,每个FMC连接器上连接一个频谱仪模块和一个信号发生器模块,从而实现对40 MHz带宽的射频信号的干扰,4个模块总共实现对160 MHz射频信号的实时干扰。

3.2.2 COM_E模块

COM-E是一种集成度高并且结构紧凑的模块计算机,可以像集成电路组件一样用于设计和应用。每个COM-E模块都集成了核心CPU和内部存储功能、通用输入输出(I/O,input/output)、USB、音频、图形以及以太网等。COM-E采用基于夹层的方法,所有I/O信号都映射到模块底部的两个高密度、薄型连接器[25]。COM_E标准基于最新的总线技术,可以将传统通信接口与现在流行的LVDS接口平滑连接,可适用于当前大部分高性能处理器,同时它也提供了传统总线技术到当今最新总线技术的过渡和兼容。

文中设计选用的COM_E模块为施耐基科技的SNJ-C567型模块,该模块可提供1个千兆以太网接口、5个USB3.0、8个USB2.0接口、2个TTL串口、4路PCIe、2个SATA 接口,可满足硬件设计需求,并且其尺寸仅为84 mm*62 mm,节省了整体空间。

3.2.3 FPGA选型

在文章所述设计中,选用赛灵思公司(XILINX)的K7系列高性能FPGA,型号为XC7K325T。此系列 FPGA集成了丰富的可编程资源,功能强大、并能够灵活组合配置的,用于实现输入输出接口、通用数字逻辑、存储器、数字信号处理、时钟管理等多种功能,并且提供了强大的布线资源与专用时钟,适用于复杂、高速的数字逻辑电路的设计实现,在通讯、信息处理、工业控制、数据中心、仪表测量、医疗仪器、人工智能、自动驾驶等领域可广泛应用[26]。XC7K325T产品包含可用于实现常规数字逻辑和分布式运行内存(RAM,random access memory)的可配置逻辑模块(CLB,configurable logic block)。设备中内部CPU与FPGA的数据通信采用FPGA内嵌的“PCI Express Endpoint”模块,支持PCI Express 1/2/4/8Lane,符合PCI Expressv1.1/2.0标准,每个Lane的传输速率是2.5 Gbps。FPGA与ADC和DAC等器件之间I/O接口的标准有LVDS与低压互补金属氧化物半导体电平标准(LVCMOS,low voltage complementary metal oxide semiconductor)。外部晶振产生200 MHz系统时钟信号并被引入到FPGA的专用引脚。此外,还包含Block RAM、数字信号处理器(DSP,digital signal processor)、混合模式时钟管理器(MMCM,mixed-mode clock manager)、千兆收发器(GTX,gigabit transceiver)等可编程模块,可以方便地实现各类特定应用。

3.2.4 模数转换器ADC

在文章所述设计中,选用亚德诺半导体公司(ADI,analog devices)的AD9643作为模数转换器,AD9643是一款双通道、14位模数转换器(ADC),其最高采样速率可达250 MSPS的,具有尺寸小、功耗低、带宽宽、多功能通信应用的特点。这款ADC采用多级、差分流水线架构,内部集成了输出纠错逻辑。AD9643均具有宽带宽输入,支持额定范围内可选的不同输入范围。其集成的占空比稳定器可用来补偿ADC时钟占空比的波动,使得转换器始终保持优秀的性能。ADC输出数据直接路由至两个外部14位LVDS输出端口,格式化为交错式或通道复用式。芯片专用差分输入可在高达400 MHz的输入频率下保持优良的信噪比性能。其芯片内部设置与控制编程利用三线式SPI兼容型串行接口与FPGA连接来完成,且可通过SYNC引脚输入允许多个设备同步。AD9643采用64引脚LFCSP封装,额定温度范围为-40~+85 ℃工业温度。

3.2.5 数模转换器 DAC

在文章所述设计中,选用亚德诺半导体公司的AD9746作为数模转换器,AD9746是一款具有10/12/14/16位分辨率的高动态范围的双口DAC,采样率高达250 MHz。其可直接转换传输应用的特定功能,包括增益和偏移补偿,可以与模拟正交调制器(MAX2829)无缝连接。与AD9643类似,其串行的外部接口SPI端口可控制芯片内部设置与逻辑。此芯片还具有低噪声和互调失真(IMD,inter modulation distortion)专用开关输出,增强动态性能和可编程电流输出和双辅助DAC的特点可以实现高质量的宽带信号合成。

3.3 频谱仪和射频信号发生器接口模块设计

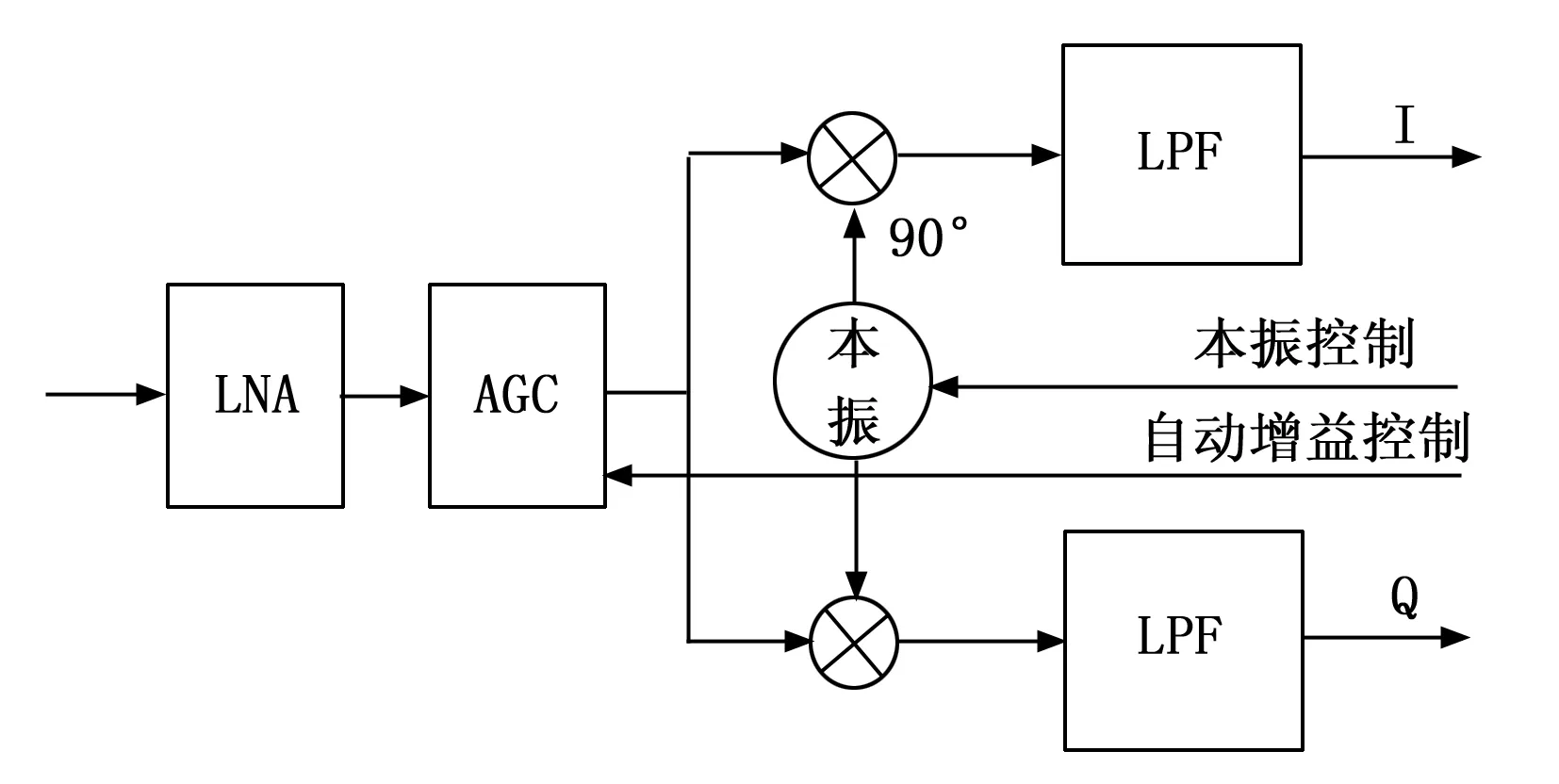

3.3.1 频谱仪接口模块设计

频谱仪接口模块功能如图5所示,射频输入信号先通过低噪声放大器(LNA,low noise amplifier)放大,然后进行自动增益控制(AGC,automatic gain control),稳定信号强度。调理后的信号经过下变频网络,同互为正交的本振信号相乘后,进入低通滤波器(LPF,low pass filter),滤除高频分量,产生基带的I分量和Q分量,送至载板上的高速ADC,由ADC采样后,送至FPGA中的FFT模块,进行信号的频谱分析。

图5中的本振信号源由FPGA控制,频率在100 kHz~6 GHz内连续可调。

图5 频谱仪接口模块功能框图

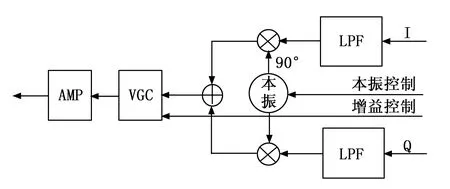

3.3.2 射频信号发生器接口模块设计

射频信号发生器接口模块功能如图6所示,DAC输出的两路互为正交的基带信号I和Q经过LPFl滤波后同相位相差90°的本振信号相乘,再经由加法器上变频至设定的频点。上变频后的射频信号经由可调增益放大器调理后送至功率放大器输出至发射天线。

图6 射频信号发生器接口模块功能框图

3.3.3 芯片选型

文中所述设计中采用的MAX2829是一款单芯片射频收发器芯片,专为正交频分多路复用技术(OFDM,orthogonal frequency division multiplexing)802.11无线局域网(WLAN,wireless local area network)应用设计。MAX2829用于双频802.11a/g应用,覆盖2.4~2.5 GHz以及4.9~5.875 GHz全波段范围。该芯片包括了实现无线射频(RF,radio frequency)收发功能所需要的全部电路,提供完全集成的接收通道、发送通道、压控振荡(VCO,voltage controlled oscillation)、频率合成器以及基带/控制接口。文中干扰器RF前端方案整体电路除MAX2829还加入了功率放大器(PA,power amplifier)、RF 开关、RF带通滤波器(BPF,bandpass filter)、RF非平衡变压器(balun)以及少量的无源器件,最终实现射频信号的收发。

此芯片在接收器/发送器内集成了滤波器,无需外部声表波(SAW,surface acoustic wave)SAW滤波器。基带滤波器和Rx/Tx信号通道经过优化,可满足802.11a/g IEEE标准,覆盖全范围的数据速率要求(OFDM的6 Mbps、9 Mbps、12 Mbps、18 Mbps、24 Mbps、36 Mbps、48 Mbps和54 Mbps;补码键控(CCK,complementary code keying)/直接序列扩频(DSSS,direct sequence spread spectrum)的1 Mbps、2 Mbps、5.5 Mbps和11 Mbps),灵敏度比802.11 a/g标准提高10 dB。MAX2829收发器采用小尺寸、56引脚、具有裸露焊盘的薄型QFN封装。

3.4 算法设计

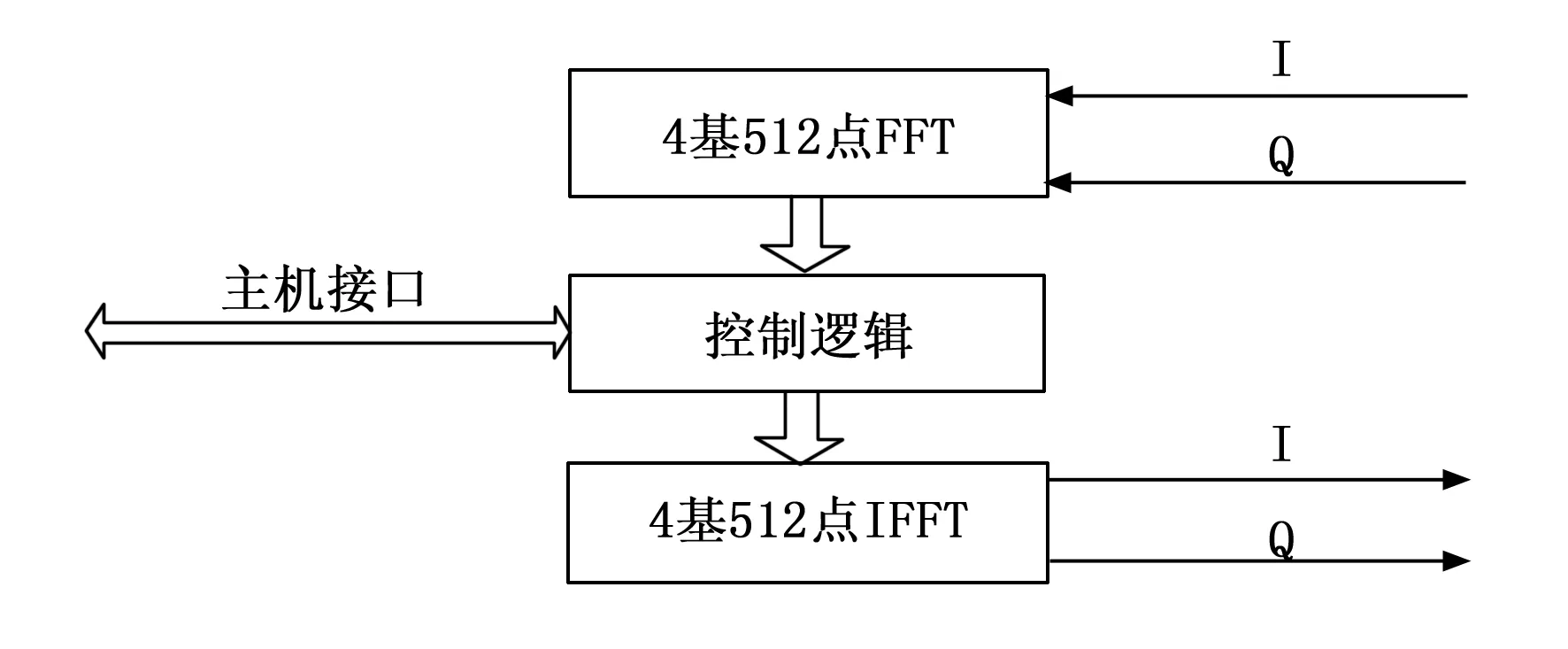

3.4.1 功能逻辑框图

干扰器控制及算法如图7所示,信号的频谱分析和干扰信号的合成均在FPGA中采用硬件逻辑实现,从而确保信号跟踪和干扰信号合成的实时性。频谱分析采用512点4基的FFT算法实现,信号合成采用512点4基的IFFT算法实现。频谱分析模块输出至控制逻辑,由控制逻辑根据频谱分析的结果来控制信号发生模块合成干扰信号。控制逻辑由软件通过主机接口控制,来设定干扰信号的模式。

图7 干扰器控制及算法框图

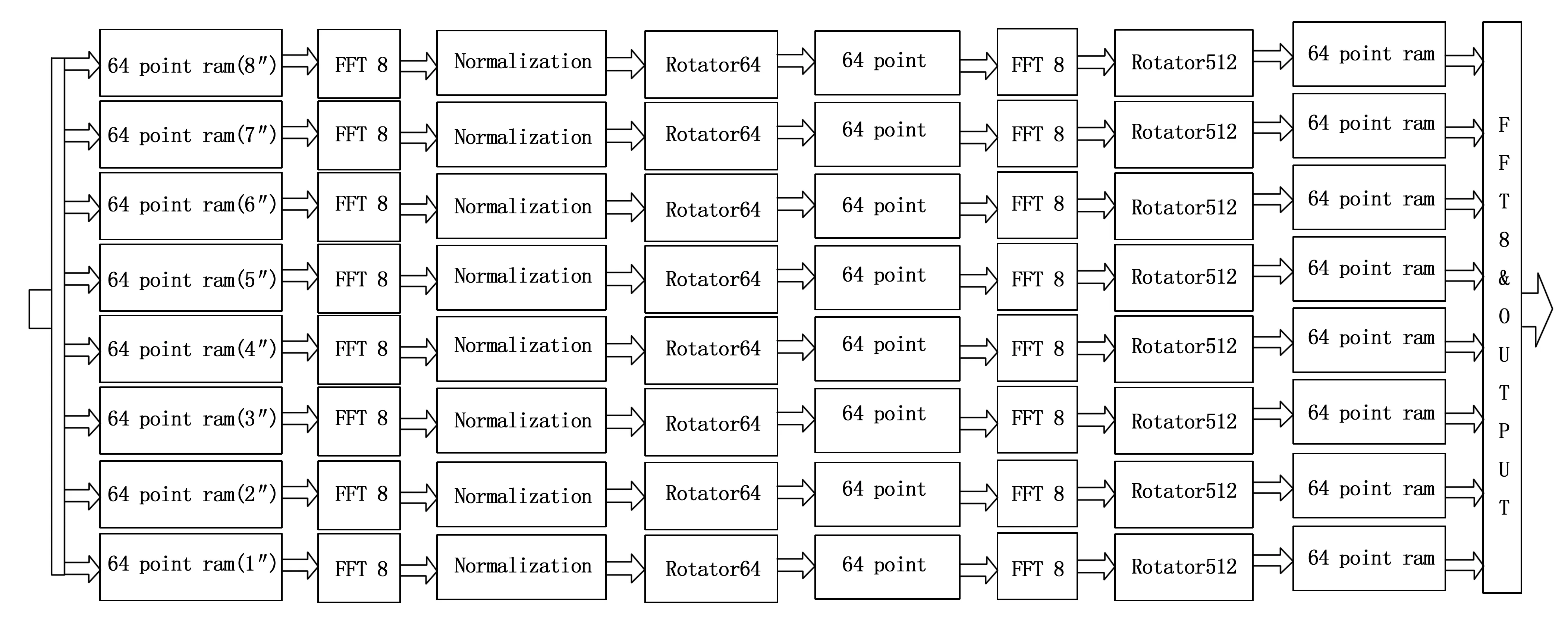

3.4.2 算法实现

512点的离散傅里叶变换表示为下式:

(1)

将上式中的求和项以8为间隔,分为8组,每组64点,重新组合后,上式等价为:

(2)

又变换为:

(3)

参见式(3),在做512点傅里叶变换前,先将其转换为8组64点的傅里叶变换,其逻辑实现如图8所示。

图8 512点FFT功能框图

FFT512和IFFT512可在256个时钟周期内完成512个谐波的分析和512个谐波的合成。图9为FFT512算法仿真结果,di与dr模拟的是ADC采集的时域输入基带信号,doi与dor模拟的是经过如图6所示算法变换后输出的频域信号。由图7信息可知,在采用256 M时钟采样时每一次采样与信号识别时间在2.5 μs以内,干扰信号的注入与合成时间也在2.5 μs以内,因此整体可在5 μs以内完成射频信号的跟踪和干扰信号的合成,从而实现最大10万次/秒的跳频信号的跟踪和干扰。

图9 FFT512算法仿真结果

4 系统软件设计

文中设计的射频通信干扰器的软件采用Visual C++语言开发,由于干扰器的算法和控制逻辑均在FPGA中通过硬件逻辑实现,所以干扰器的软件设计主要为人机交互界面,一方面用于干扰器工作过程中的工作参数设置,另一方面用于射频信号的监测和显示。

4.1 软件设计流程

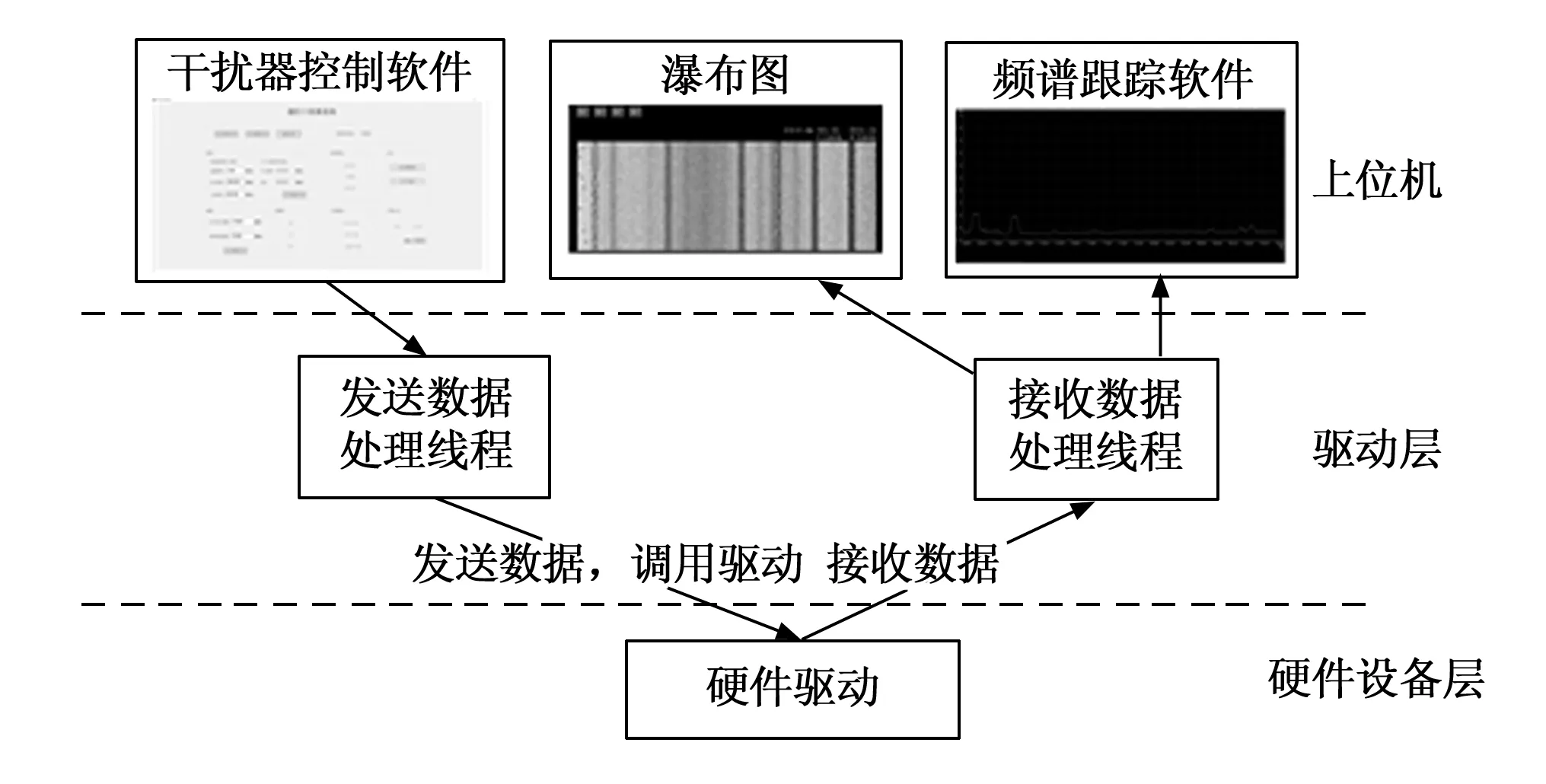

在设计实现上,射频通信干扰器软件由上位机软件、驱动软件两部分组成,其设计实现基本思路如图10所示。上位机软件由频谱跟踪软件、瀑布图软件、干扰器控制软件三部分构成,主要实现干扰器跟踪数据的曲线显示、干扰器跟踪频点抑制后的情况显示、频段内频点信号强度的显示,以及通过界面对干扰器设备的启停、干扰类型、干扰种类的控制。驱动层软件主要完成与干扰器硬件的交互,完成干扰器命令和数据的转发传递。

图10 干扰器软件设计实现

4.2 系统设置界面

射频通信干扰器系统设置界面如图11所示,系统配置界面由以下几个功能区域组成,可对干扰器设备的启停、干扰模式、干扰方式等的控制。

4.1.1 系统控制按键

用于打开/关闭频谱仪、功率放大器,波形起止、系统屏幕显示。

4.1.2 参数设置区域

1)频率设置:

(1)起始和终止频率:可手动改变起始和终止频率;

(2)中心频率和带宽:可手动改变中心频率和带宽;

(3)分屏频率:可以手动改变分屏的频率值。

2)阈值设置区域:

(1)信号电平阈值:可更改信号电平阈值;

(2)频率跳变阈值:可更改频率跳变阈值。

3)灵敏度设置区域:

点击“高”、“中”、“低”根据需要进行灵敏度设置。

4)采样模式设置区域:

(1)点击“最大值”,可出现干扰器工作期间的各段频率对应幅值的最大值;

(2)点击“最小值”,可出现干扰器工作期间的各段频率对应幅值的最小值;

(3)点击“平均值”,可出现干扰器工作期间的各段频率对应幅值的平均值。

5)干扰模式设置区域:

干扰模式调节点击“单音干扰”、“多音干扰”、“白噪声干扰”。

6)干扰方式:

(1)手动干扰:选择“手动”,输入目标干扰频率即可;

(2)自动干扰:双击屏幕目标干扰频率即可。

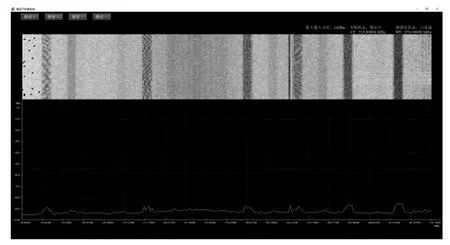

4.3 信号监测界面

图12为射频通信干扰器信号监测界面,信号监测界面由上到下分为控制按钮和数值信息显示区域、频谱瀑布图显示区域、频谱曲线显示区域三部分,用户可直观地通过数值、颜色、曲线等不同形式观察频谱信号的情况,可以实现干扰器跟踪数据的曲线显示、干扰器跟踪频点抑制后的情况显示、频段内频点信号强度的显示等。

图12 射频信号跟踪/干扰界面

信号监测界面主要包含以下控制按键:

1)频标X1按钮:打开频标X1会显示一条垂直虚线,在图表右上角会显示频标X1的位置信息,与X2配合可以测量一段波形的频率大小,数值显示在右上角。

2)频标X2按钮:打开频标X2会显示一条垂直虚线,在图表右上角会显示频标X2的位置信息,与X1配合可以测量一段波形的频率大小,数值显示在右上角。

3)频标Y1按钮:打开频标Y1会显示一条水平虚线,在图表右上角会显示频标Y1的位置信息,与Y2配合可以测量一段波形的信号强度大小,数值显示在右上角。

4)频标Y2按钮:打开频标Y2会显示一条水平虚线,在图表右上角会显示频标Y2的位置信息,与Y1配合可以测量一段波形的信号强度大小,数值显示在右上角。

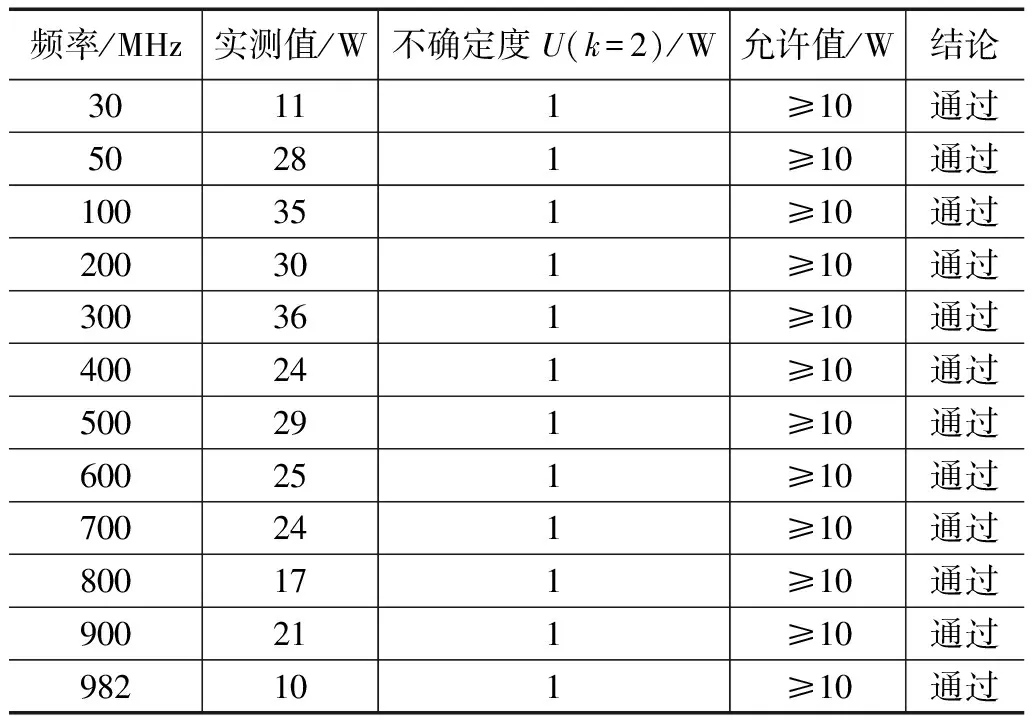

5 实验结果与分析

在室温环境下,通过使用双通道宽带功率计、频率计数器、衰减器、频谱分析仪等测试设备对射频通信干扰器输出的短波信号各项参数指标进行实际测量,以验证设备性能。

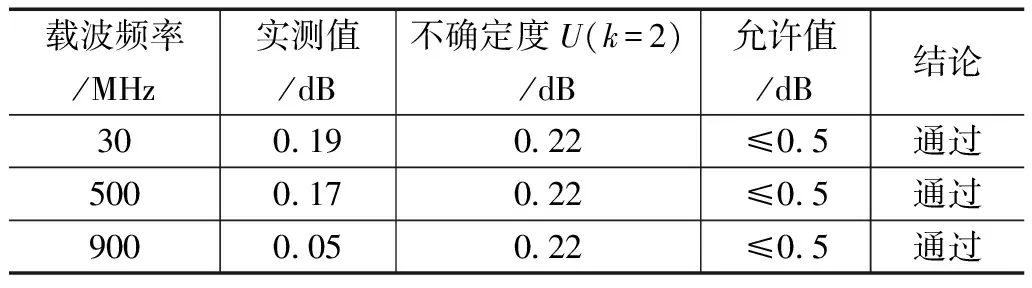

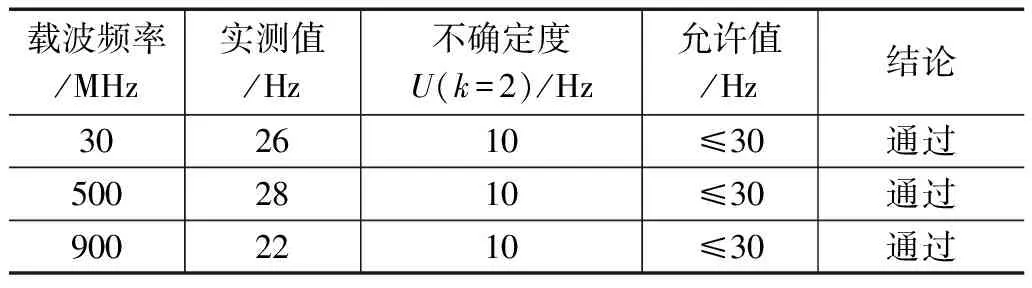

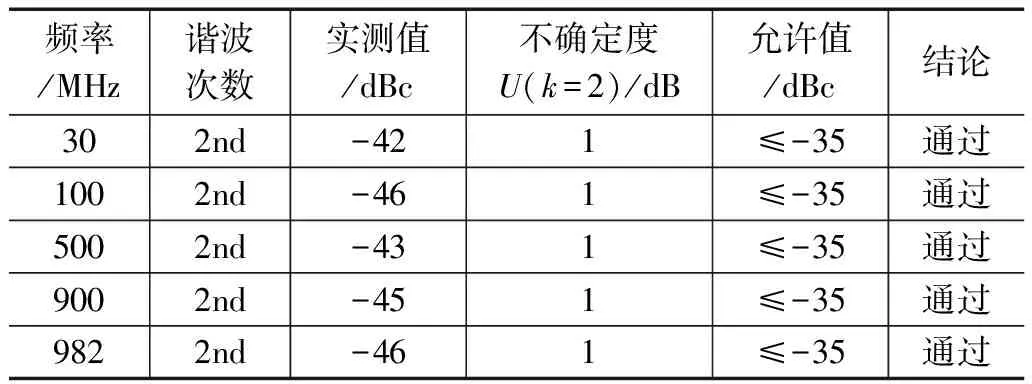

测量结果如表4~8所示。

表4 频率准确度

表5 输出功率

表6 输出功率稳定度@5分钟

表7 输出频率稳定度@5分钟

表8 干扰信号谐波

测试数据表明,文中所设计的射频通信干扰器的各项技术指标可满足实际使用要求。

6 结束语

本文所设计的射频通信干扰器主要用于电子对抗中对短波、超短波和射频微波信号的干扰。该干扰器采用FXI规范,实现了模块化、小型化和轻量化的设计,且符合单兵便携式使用要求。经过测试,所设计的射频通信干扰器的各项指标满使用足要求,并已应用于某部队通信训练中,并可进一步推广至电子对抗、无人机干扰等技术领域。