增强型GaN HEMT器件的实现方法与研究进展*

穆昌根,党 睿,袁 鹏,陈大正

(1.西安电子科技大学微电子学院,西安 710071;2.西安航天精密机电研究所,西安 710100)

1 引言

氮化镓(GaN)材料近年来发展势头迅猛,被业内人士誉为第三代半导体材料,因其具有宽带隙、高电子漂移速度、抗辐射、耐高温等优良的物理特性,逐渐成为高频、高温、高效率、抗辐射等领域的热门研究对象[1]。目前开发成熟的GaN基功率器件大多是GaN基高电子迁移率晶体管(HEMT)器件,良好的性能使其在消费类电子产品、轨道交通、工业设备及通信基站等领域的应用前景十分广阔。

对于GaN HEMT器件,由于AlGaN/GaN异质结界面处内部存在的压电极化和自发极化效应共同作用,产生了大量二维电子气(2DEG)[2],使得GaN HEMT器件在无外界偏置情况下仍然存在天然的导电沟道,使器件在零偏压下处于导通状态,所以一般的GaN HEMT器件为耗尽型(D型)器件。自1993年KHAN等人[3]成功制备第一个耗尽型GaN HEMT器件以来,由于该器件在无外加偏置电压情况下会引起较大的导通电阻和较高的开关损耗,同时还需要额外的负偏置电压来维持非工作状态而增加器件功耗,如今的耗尽型GaN HEMT器件的应用受到了极大的限制。反之,具有正向开启电压的增强型(E型)GaN HEMT器件因其本身所表现出的良好失效保护功能、快速开关速度和低反向导通损耗等显著性能[4],在应用上作为实现单片集成的GaN基互补逻辑(CL)的基本单元,日益成为研究者们关注的对象。实现增强型GaN HEMT器件的关键在于通过一定方法尽可能使栅下异质结界面处的2DEG耗尽。自相关研究者于1996年成功制备增强型的薄势垒AlGaN/GaN HEMT器件[5]以来,研究者们通过结构设计及改进工艺,提出了多种实现增强型GaN HEMT器件的方法,其中常见的有p型栅技术[6]、凹栅结构[7]、共源共栅(Cascode)结构[8]、氟离子处理法[9]、减薄势垒[10]及它们的改进结构等,这些技术大大改善了GaN HEMT器件的工作性能。

本文综述了使用以上方法制备的增强型GaN HEMT器件及它们的优势和缺陷,分别对增强型GaN HEMT器件的最新研究进展和业界最新的GaN器件解决方案进行了总结及介绍,探讨了未来增强型GaN HEMT器件的发展方向。

2 增强型GaN HEMT器件的实现方法

增强型GaN HEMT器件在应用中有着独特的性能优势,针对如何制造出性能优良的增强型GaN HEMT器件的问题,目前提出的几种常见解决方案中有些已成功应用于商业领域,以下分别对这几种方案进行综述。

2.1 p型栅技术

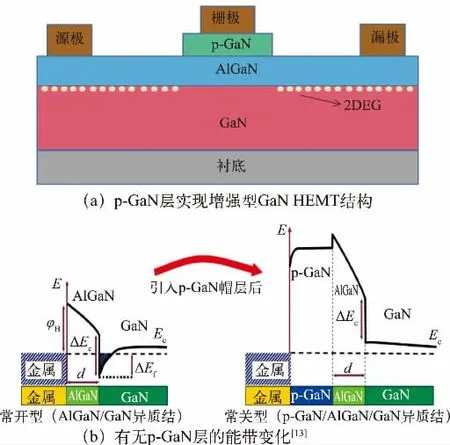

最具代表性的增强型GaN HEMT器件实现方法是p型栅技术[11]。该技术由丰田公司于2007年首次提出[12],后来逐渐发展成为商用主流技术之一。此类增强型器件通过在AlGaN势垒层上方淀积一层Mg离子掺杂的p-GaN帽层,再在该帽层上溅射金属栅极而成。其中,Mg离子掺杂的有效浓度及p型栅帽层的厚度等与器件的导通电阻及阈值电压等有着密切的联系。图1(a)为p-GaN帽层增强型GaN HEMT器件的结构。在零偏压的情况下,p-GaN帽层可以将AlGaN/GaN异质结界面处的导带能级提升至费米能级以上,耗尽异质结界面处的2DEG,导致栅下有效沟道夹断。当施加一定的正向偏置电压后,随着栅下2DEG的恢复,HEMT器件随之开启。使用p-GaN帽层前后异质结处能带的变化如图1(b)所示,图1(b)中E为能量,△Ec为AlGaN和GaN之间的导带底在交界面的带阶,△Ef为GaN内部和GaN表面的费米能级之差,d为AlGaN势垒厚度,φB为肖特基势垒高度,Ec为GaN的导带底。

图1 增强型p-GaN帽层HEMT结构及有无p-GaN层的能带变化

该技术实现的增强型器件阈值电压较稳定、导通电阻低、可靠性强,但同时也面临着栅控能力减弱、寄生电容增加等问题。

2.2 凹栅结构

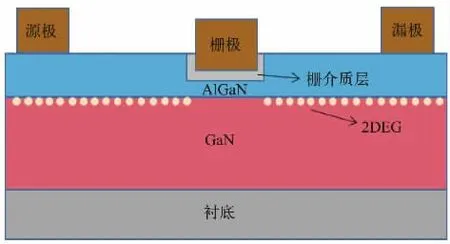

早在2003年,OKITA等人[14]就使用凹栅刻蚀的方法成功制备了增强型的AlGaN/GaN MIS-HEMT器件,其相关研究一直在进行,凹栅刻蚀实现增强型GaN HEMT器件的原理就是通过一定手段对栅下AlGaN/GaN异质结处一定厚度的势垒层进行部分刻蚀或完全刻蚀,其不仅降低了栅下的极化电荷密度,也减小了栅极金属和沟道的距离,同时利用肖特基接触产生的电场,共同耗尽栅下感应的2DEG,从而实现增强型GaN基器件的目的。从能带结构上看,则为势垒层导带能级下降不足导致二维势阱消失,进而使2DEG耗尽。图2为凹栅结构实现增强型GaN基器件的结构图。

图2 凹栅结构实现增强型GaN HEMT器件的结构

凹栅GaN HEMT器件不仅提高了器件的栅控能力,还大大改善了增强型器件的频率及跨导,但在刻蚀过程中引入的刻蚀损伤及界面态会严重影响此类器件的性能可靠性,尽管这种影响可通过淀积栅介质得到改善,但目前仍限制着其商业应用。

2.3 Cascode级联结构

采用Cascode级联结构实现增强型GaN HEMT器件的技术也已成功用于商业市场。作为一种Si基功率器件向纯GaN基功率器件的过渡技术,传统的Cascode FET采用Si基MOSFET和常开耗尽型GaN HEMT器件联接,然后将它们封装在一起,而对外整体呈现为增强型。图3是其相应级联的等效电路结构图,该图展现了其基本的连接形式,Si基晶体管的漏极与D型GaN HEMT器件的源极相联,而D型管的栅极与Si基晶体管的源极相联,同时Si基MOSFET的栅极阈值电压作为整个器件的阈值电压,控制着Cascode器件整体的导通与关断。

图3 Cascode结构等效电路

采用传统Cascode级联技术实现的增强型器件阈值电压高且稳定,并且能够和现有的Si电路匹配良好,但是由于其自身存在的电容失配问题,在耐高温和小型化设计方面远不及非级联的增强型GaN基HEMT器件,限制了其未来进一步的应用。

2.4 氟离子处理技术及减薄势垒层法

使用氟离子注入技术制备增强型GaN HEMT器件,通常是在栅极沉积前通过一定技术对栅下AlGaN势垒层注入一定剂量及能量的氟离子。由于氟离子对外整体呈现负电性,进入到AlGaN势垒层中的氟离子形成了带负电的固定电荷,从能带结构上看,其在提高势垒层势垒高度的同时,提高了异质结界面处的导带能级,当导带能级底部超过费米能级时,该异质结处的二维势阱消失,进而使栅下沟道中的2DEG耗尽,达到正向移动阈值电压的目的。图4(a)为使用氟离子处理技术实现增强型GaN HEMT器件的结构。采用氟注入法制成的增强型GaN HEMT器件通常能够达到很高的正向阈值栅电压,同时,结合栅介质层能够很好地抑制栅泄漏电流、提升栅摆幅,然而离子注入会形成大量的空态及界面态,对势垒层造成损伤,会使阈值电压的稳定性变差[15]。

减薄势垒层法通过改变AlGaN势垒层的厚度d,使势垒层的极化电荷密度降低,当降低至一定值时,沟道便不会感应生成2DEG;从导带结构上看,和凹栅刻蚀技术相似,减薄势垒层后,因势垒层的导带下降不足使得AlGaN/GaN异质结处导带上升或抬升到费米能级以上,使原本存在的二维势阱消失,从而耗尽2DEG,实现器件的增强型工作。减薄势垒前后异质结处能带结构如图4(b)所示,其中Ef代表费米能级,d1代表常规GaN HEMT器件中AlGaN势垒层的厚度,d2代表薄势垒GaN HEMT器件中AlGaN势垒层的厚度。虽然薄势垒形成的增强型器件避免了由凹栅刻蚀带来的损伤和界面态,但传统的薄势垒器件通常都面临着沟道中2DEG密度降低、导通电阻变大的问题。

图4 氟离子注入型器件结构及D型与薄势垒器件能带对比

3 增强型GaN HEMT器件的最新进展

近几年来,随着新技术及新结构的运用,增强型GaN HEMT器件的相关性能不断提高,各项性能指标都不断接近GaN基器件的理论水平,同时相关的商业产品也在不断推出,这里对最新的研究进展进行总结,并介绍相关制造商近几年推出的增强型GaN器件解决方案。

3.1 p型栅技术的最新进展

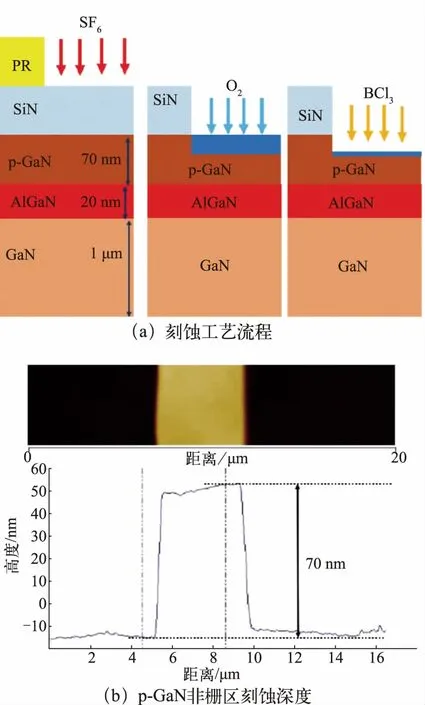

在p型栅技术中,使用p-GaN帽层是最成熟的,近年来,国内外研究者在该技术的基础上不断进行着工艺或结构上的优化和创新。2018年LIN等人[16]通过两步数字刻蚀(DE)工艺制备了p-GaN栅HEMT器件,在循环刻蚀过程中移除了不需要的p-GaN帽层,最大程度上减少了对材料的损伤,图5(a)所示为刻蚀工艺流程,图5(b)所示为p-GaN非栅区刻蚀深度。当源极和漏极的间距LSD=20 μm时,该器件实现了较大的阈值电压(2 V),漏电流密度达到了211 mA/mm,同时静态导通电阻降低至17.3 Ω·mm,其开关电流比及击穿电压分别达到1.2×106和426 V。

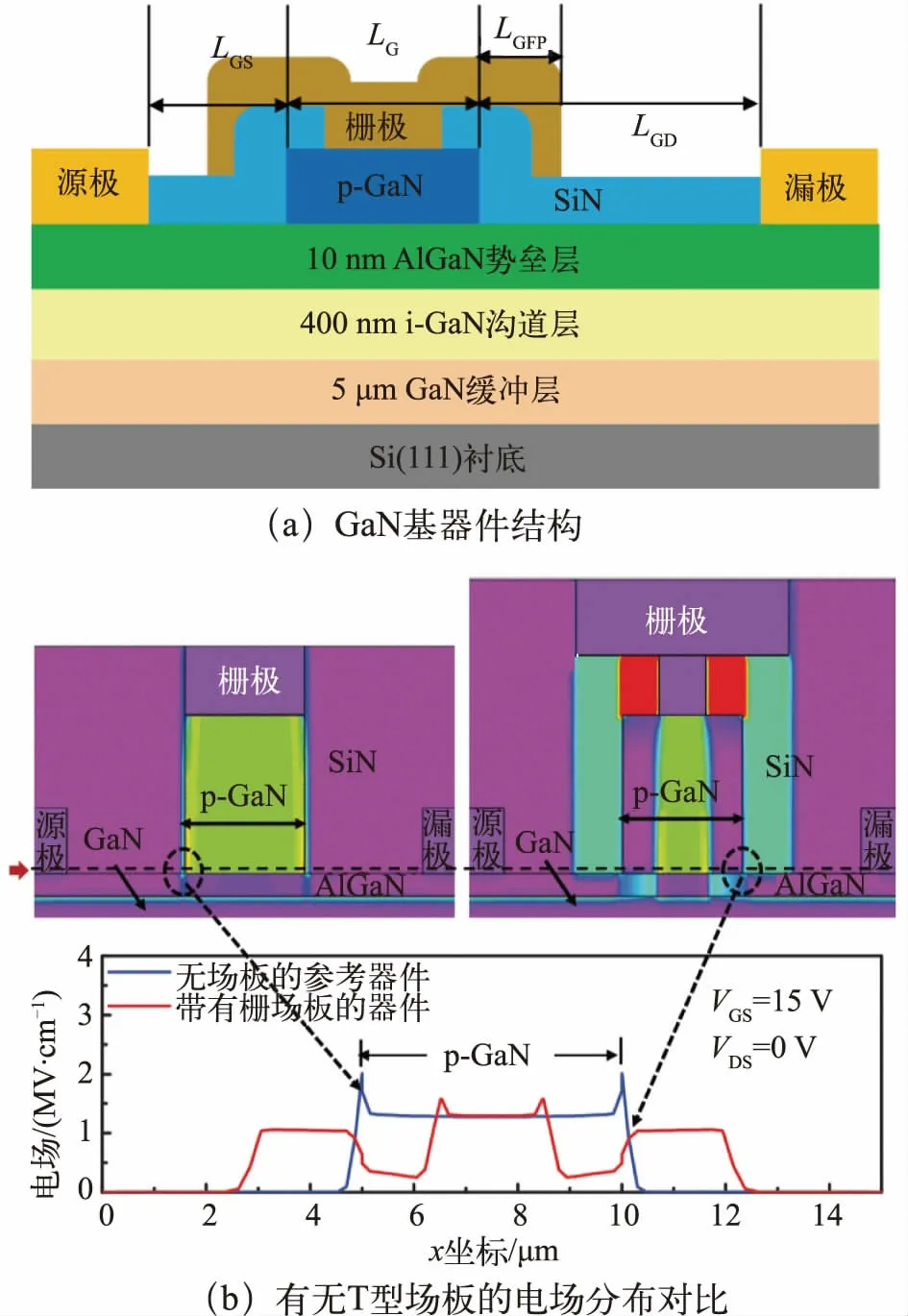

针对传统的p-GaN层形成的增强型器件击穿电压较低的问题,一般通过各种场板结构的设计来提高击穿电压。2019年JIANG等人[17]通过设计T型栅接触场板和减少金属/p-GaN接触外沿,使该器件不仅通过抑制AlGaN表面附近p-GaN边沿的电场峰值提高了器件的击穿电压,还保护了p-GaN/AlGaN/GaN结的完整性,从而在关断状态下,栅被击穿后仍然保存着对电压的阻断能力,使器件不受进一步的损坏。其击穿电压达到1100 V时,阈值电压可达2.3 V,最大漏电流为610 mA/mm,亚阈值摆幅(SS)及开关电流比分别达到66 mV/dec和5×108。图6(a)为该GaN器件的结构,其中LGS为栅源间距,LG为栅极长度,LGFP为漏极方向的栅场板长度,LGD为栅漏间距,图6(b)为有无T型场板的电场分布对比,其中VGS代表加在栅源间的电压,VDS代表加在漏源间的电压。

图5 数字刻蚀工艺流程及非栅区帽层刻蚀深度示意图

2020年HU等人[18]通过使用源场板和栅场板的双场板组合结构实现了电场的均匀分布,提高了击穿电压(600 V),减少了界面附近的电荷捕获效应,同时结合NH3等离子体处理还显著降低了该器件的动态导通电阻Ron,在200 V电压阻断后导通电阻仅增加了50%,从而有效抑制了电流崩溃效应,其阈值电压达到3.7 V,饱和电流为132 mA/mm。为了使器件的击穿电压和导通电阻实现良好的性能折中,2021年WEI等人[19]用选择性氢等离子体处理p-GaN,实现了一种横向耦合p-GaN栅HEMT器件,其器件结构如图7所示。当各p-GaN条的宽度Wp和相互间的间距WHR设计得足够小时,耗尽区的耦合效应可使器件击穿电压和导通电阻的折中良好,当p-GaN和漏极的间距LPD=10 μm时,器件性能达到最优,导通电阻低至11.54 Ω·mm的同时击穿电压可达到880 V。

图6 增强型器件结构及有无场板的电场分布对比[17]

图7 一种横向耦合p-GaN栅HEMT器件[19]

同年JIANG等人[20]通过改进上述增强型p-GaN HEMT器件工艺,用原子层沉积(ALD)技术沉积Al2O3代替等离子增强化学气相沉积(PECVD)技术沉积SiN作钝化层,并进行高电阻率缓冲层优化生长,在保持此前报道的阈值电压、亚阈值摆幅等性能参数的同时,进一步提高了器件的击穿电压(1344 V)及导通电阻(约14 Ω·mm)的折中关系,同时其峰值跨导达到135 mS/mm,表征功率特性的Baliga优值(BFOM)达到461 MW/cm2。尽管p-GaN HEMT器件是p型栅器件中最成熟的,但其固有的Mg掺杂难激活等问题始终限制着器件性能的大幅提升,因此p型金属氧化物帽层的研究一直在进行。2022年,西安电子科技大学的CHEN等人[21]通过磁控溅射沉积p-SnO代替p-GaN作为AlGaN/GaN HEMT的栅帽层,在未经优化的器件上实现了1 V的阈值电压及420 V的器件击穿电压,表明其拥有巨大的应用潜力。

3.2 使用凹栅结构的最新进展

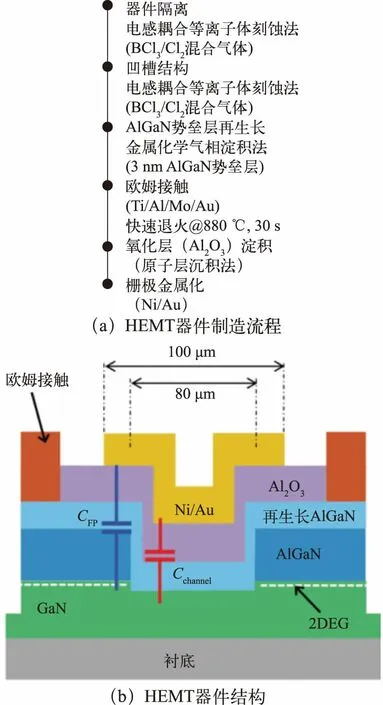

针对传统凹栅刻蚀形成的增强型器件出现大量的刻蚀损伤及界面态所导致的栅泄露等问题,一般都是通过沉积各种不同的栅介质及改进生长工艺来降低损伤及界面态带来的影响,提高器件阈值电压及频率特性等。2019年LI等人[22]通过将硅原子加入到原子层沉积的栅介质HfO2中改善了增强型GaN MOS-HEMT器件的相关性能,与传统的HfO2栅介质相比,其界面陷阱密度降低了一个数量级,内部的固定氧化层陷阱减少了一半,表现出很好的频率特性和器件可靠性,其阈值电压为1.5 V,SS低至65 mV/dec,电流开/关比高达1010以上,而最大击穿电压(742 V)比传统的HfO2栅介质的HEMT器件提高了30%。而在改进工艺方面,2020年,ASUBAR等人[23]提出了生长在SiC衬底上的凹栅刻蚀结合金属有机物气相外延(MOVPE)再生AlGaN势垒层技术的增强型MIS-HEMT器件结构,图8(a)为该GaN器件制造流程图,图8(b)为该器件的结构图。通过再生工艺形成一层新的半导体-绝缘体界面,极大地降低了干法刻蚀对2DEG密度和迁移率造成的影响,其阈值电压达到5 V,最大漏电流达到425 mA/mm,而关断状态下漏击穿电压为120 V。

此外,2021年,CAI等人[24]提出以在凹栅下沉积Al2O3/ZrOx/Al2O3电荷俘获介质层的方式降低刻蚀带来的影响,当栅漏间距LGD=5 μm时,其阈值电压为(1.55±0.4)V,最大漏电流密度为(730±6)mA/mm,导通电阻为(7.1±0.2)Ω·mm,同时,器件还表现出较高的稳定性击穿电压(1447 V)。尽管该器件在实际使用中需要进一步优化阈值电压的稳定性,但通过使用ZrOx电荷捕获层来实现高阈值电压和低导通电阻的方法显示出了巨大的应用潜力。

图8 增强型MIS-HEMT器件制造流程及结构[23]

3.3 Cascode结构的最新研究进展

Cascode结构作为比较成熟的技术,传统双芯片共封装的形式阻碍了性能的进一步提升,为了改善性能,2018年REN等人[25]利用外延生长的单片集成技术设计制成了适用于高电压功率转换的增强型Cascode FET器件,芯片间互联距离仅是传统双芯片共封装器件的2.5%,进而降低了寄生效应,经测试,该器件阈值电压和栅压摆幅分别为3.2 V和±20 V,而击穿电压达到了696 V。图9为该Cascode FET器件的结构图。

图9 Cascode FET器件结构[25]

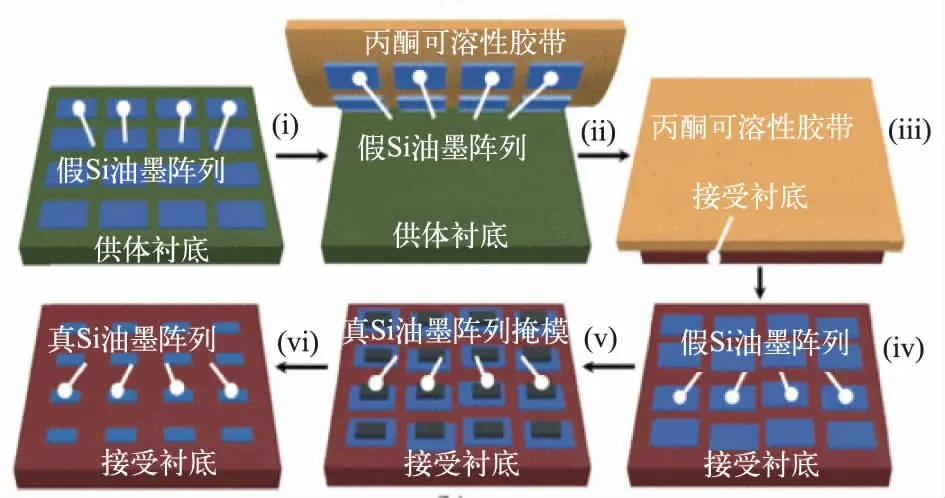

外延生长的方式对材料晶格匹配度及外延晶面选择性要求严格,且设备昂贵,2020年西安电子科技大学的ZHANG等人[26]采用转移印刷及自对准刻蚀技术制成了单片集成的增强型Cascode FET器件,降低了成本,解决了上述问题,相比传统Cascode FET器件,该器件不仅展现了极好的界面形貌、较小的开关损失及良好的阈值电压均匀性(2.0~2.2 V),同时栅压摆幅达到±18 V,栅漏电流也低于10-5mA/mm。图10展示了转移印刷和自对准刻蚀技术的关键步骤。

图10 转移印刷和自对准刻蚀技术的关键步骤[26]

此外,采用Si MOSFET和GaN HEMT联接的传统Cascode FET器件不可避免地会带来两者本征电容不匹配及增强寄生电感问题,2021年LIU等人[27]采用凹栅GaN MIS-FET替代Si基MOSFET与D型GaN基HEMT联接,较好地缓解了上述不良影响,同时其阈值电压达到3.6 V,硬击穿电压也高达883 V。

3.4 使用氟处理技术、减薄势垒层及其他方法

虽然用氟处理技术及减薄AlGaN势垒层的方式也可以实现增强型GaN HEMT器件,但它们都存在各自的缺点。通过改进工艺及结合其他技术使用氟处理技术及减薄势垒层形成增强型GaN HEMT器件的性能得到不断提高。2018年LING等人[28]通过淀积与源极相接触的TiN侧壁和TiN层,结合两步氟处理工艺制备增强型GaN HEMT器件,通过两步氟处理进一步提高了势垒层中的氟离子浓度,使得势垒层导带更大地向上弯曲,增大了背势垒高度,减少了栅泄漏电流,而沉积向栅极延伸一定长度(Lledge)的TiN层,改善了等效电路的拓扑结构,进而降低了源电阻,当Lledge=1 μm时,最大漏电流达到845 mA/mm,其峰值跨导(412 mS/mm)比传统器件峰值跨导(340 mS/mm)提高了21.2%。此外,该器件的电流增益截止频率(fT)和功率增益截止频率(fMAX)分别达到了61 GHz和130 GHz,其Johnson优值达到11.2 THz·V,表现出良好的高功率、高频率特性。

而2020年ZHENG等人[29]通过研究采用氟离子处理技术形成的增强型GaN HEMT器件在反向栅应力下阈值电压的退化机理及经退火恢复的机理时发现,氟离子碰撞电离阈值电压退化的主要原因是:在较大的反向栅应力下,栅下注入电子密度Qinj越大,与氟离子碰撞电离越激烈,阈值电压退化也越严重,但经栅应力后一定时间的退火,沟道中的电子会隧穿进入势垒层中栅应力所产生的中性陷阱中并被捕获,使阈值电压正向移动。这一研究为进一步采用氟处理实现高性能的GaN器件提供了参考。图11为栅下注入电子与阈值电压的漂移量ΔVth的关系及退火过程中电子隧穿进入沟道示意图,图11(a)中Vg为所加栅电压,Vd为所加漏电压,Vs为所加源电压,图11(b)中Ev代表价带顶。

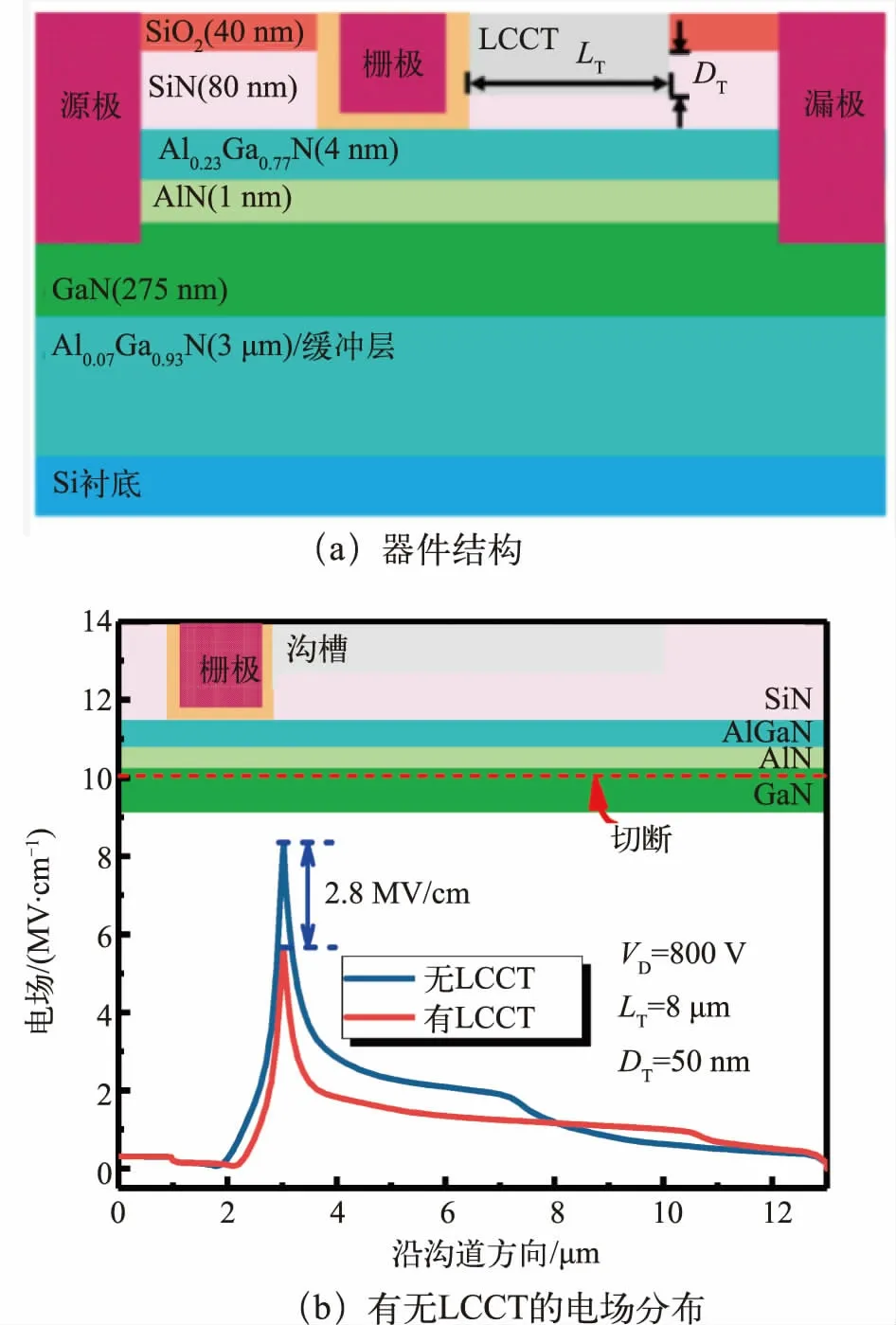

在薄势垒研究方面,2019年HAN等人[30]通过使用SiN作钝化层、AlOx作栅介质层及利用铁电电荷陷阱栅叠层制备出超薄势垒的增强型MIS-HEMT器件,相较于传统的凹栅增强型GaN HEMT器件,该器件不仅有更高的阈值电压及最大漏电流,还拥有更小的阈值迟滞和更好的阈值电压均匀性,其阈值电压达到3.19 V,最大漏电流达到716 mA/mm,并且击穿电压也高达906 V,在集成电路及电源开关应用领域表现出极好的应用前景。同年,WANG等人[31]则通过在增强型薄势垒GaN HEMT器件栅漏间刻蚀SiN钝化层引入局部电荷补偿沟道(LCCT)的方式优化电场分布和BFOM,经调整LCCT的刻蚀长度和宽度,与传统薄势垒GaN HEMT器件相比,其电场峰值降低了2.8 MV/mm,同时使LCCT下的电场分布更平坦,其BFOM更是传统薄势垒GaN基HEMT器件的2倍。图12(a)(b)分别为其器件结构及有无LCCT的电场分布,其中LT代表LCCT长度,DT代表刻蚀80 nm氮化硅层的刻蚀深度,VD代表器件所加漏极电压。

图12 引入LCCT的器件结构与有无LCCT的电场分布[31]

为了对文中提到的增强型GaN HEMT器件的性能有更直观的比较,将相关文献中部分增强型GaN HEMT器件的性能参数概括到表1。

通过对增强型GaN HEMT器件最新研究进展的总结可以发现,各增强型器件的相关性能得到不断提高,甚至某些性能指标已达到极高标准(如经过场板设计后的击穿电压),不难想象未来有望进一步加深其应用的程度。但在实际应用中,除了考虑器件良好的性能及可靠性,还应该使它与现有的或改进创新的电路拓扑结构、布局互联、散热性能的设计及先进封装设计等有良好的适配,所以在今后的研究中,进一步优化器件结构、提高工艺设计水准、提高器件可靠性及不断推进各类增强型器件的产品化设计等都是重要的方向。

表1 文献中的增强型GaN HEMT器件性能参数

3.5 产业界最新推出的GaN器件解决方案

在功率器件应用方面,目前,市场上已有很多性能良好的基于GaN HEMT器件的功率产品。2018年,GaN Systems公司推出了100 V/120 A GaN E-HEMT装置GS-010-120-1-T,良好的性能使其适合于汽车和可再生能源等行业48 V的应用;同年,日本松下也推出了基于MIS结构730 V/20 A的GaN功率器件,该产品可以在栅压高达10 V时稳定连续工作而阈值电压不会发生变化,其运用可进一步缩小各种功率转换电路的体积。2020年,Transphorm公司也推出了650V/72 mΩ常关型GaN产品TP65H070LDG,该产品易于驱动,且能与标准栅极驱动器兼容。2021年末,意法半导体宣布推出2个GaN功率半导体新产品系列“G-HEMT”和“G-FET”。“G-HEMT”系列的首款器件为650 V/15 A的SGT120R65AL,该产品拥有极低的传导损耗、高电流能力和极快的开关速度,能实现很高的功率密度及性能效率,而“G-FET”系列的首款器件则是Cascode型的GaN晶体管SGT250R65ALCS,这2个系列产品的推出将使消费类电子产品和车载装置等的电源实现更高效率和小型化的设计。

在数字电路领域,尽管ZHENG等人[32]通过在同一衬底上集成n沟道及p沟道FET构成GaN CL,并对由GaN CL组成的反相器、部分基本逻辑门及多级环形振荡器等进行了分析,表明了GaN CL拥有巨大的应用价值,但相比于GaN HEMT器件功率产品的不断推出,适于数字电路的性能优良的GaN CL现今却难以实现,主要原因在于其互补的增强型p沟道场效应晶体管面临着低迁移率、高接触电阻及栅控能力弱等挑战,而通过改进刻蚀工艺、运用再生长技术及研究新结构是改善这些问题的途径,BADER等人[33]的研究结果表明AlN/GaN/AlN的结构拥有巨大的潜力。

4 结束语

尽管业内提出了多种制备增强型GaN HEMT器件的技术,有些已商业化应用,但都存在各自的缺陷。此外,在设计增强型GaN HEMT器件时,还需要兼顾各项性能指标间的折中关系并提高器件可靠性,要想实现性能良好的增强型器件,需要研究者或进行结构和工艺上的改进,或提出新的结构。而在应用上,对性能良好的GaN基CL的研究也任重道远。本文通过对增强型GaN HEMT器件的实现方法和最新进展进行综述,为相关研究者研发高可靠性的、适于产品化的增强型GaN HEMT器件提供了有价值的参考。