基于精简指令集的内核验证参考模型设计

王镇道 姚小姣

摘要:功能验证能在芯片设计前期快速、低成本发现缺陷,对于保证设计质量具有重要意义.针对内核模块验证中指令序列随机性差、测试用例编写繁琐和验证平台重用性差等问题,设计了一款8位精简指令集内核验证参考模型,通过对指令集单独建模、可配置化参数设计等方法满足了指令序列随机组合的验证需求和重用性,且结合自动化脚本的使用解决上述相关问题.将参考模型搭载UVM平台对一款RISC架构的8位MCU内核进行验证.验证结果表明:集成了所设计参考模型的UVM平台具有很好的鲁棒性和重用性,缺陷数量收敛快,验证周期更短,内核模块的代码和功能覆盖率均达到100%.

关键词:内核验证;RISC-V;验证;System Verilog语言

中图分类号:TP332文献标志码:A

Design of Reference Model for Core’s Verification Based on Reduced Instruction Set

WANG Zhendao,YAO Xiaojiao

(College of Physics and Microelectronics Science,Hunan University,Changsha 410082,China)

Abstract:Functional verification can find defects quickly at a low cost in the early stage of chip design,which is 0f great significance to ensure design quality. In view of the problems of poor instruction sequence randomnes,cumbersome testcase writing and the verification platform ’s poor reusability in core module-level verification,an 8- bit RIS core verification reference model is designed. The model satisfies the verification requirements of the instruction sequences,random combination and reusability through independent modeling of the instruction set and configurable parameter design,and the use of automated scripts solves related problem above. The reference model equipped with the UVM platform is applied to verify an 8-bit MCU core with a RISC architecture. The results show that the UVM platform integrated with the designed reference model has good robustness and reusability,the number of defects converges quickly,and the verification cycle is shorter. The code coverage and function coverage of the core module reach 100%.

Key words:core verification;RISC-V;verification;System Verilog

随着半导体工艺不断突破新的极限,数字电路集成度和复杂度陡增,如何提升设计效率、缩短芯片设计周期、提高设计可靠性是IC设计急需解决的问题[1-2].功能验证能够在IC设计RTL阶段发现设计缺陷,是在芯片硅前流程提高设计质量的最有效方式. 在复杂的IC设计中,设计开发时间的70%用于验证[3],提高验证效率和完备性对降低设计成本、缩短设计周期十分重要[4].微处理器可以说是数字芯片的“头脑”,其性能和设计质量的好坏直接决定整个芯片的质量[5-6],而功能验证是微处理器设计验证的重中之重[7],如何优化微处理器的功能验证具有重要的现实意义.

模拟仿真方法是当前微处理器功能验证的主要方法[8],包括功能覆盖率驱动的基于UVM的RTL驗证[9]和FPGA硬件原型验证[10]等.为提高微处理器验证的效率和可靠性,研究者们提出了很多方案,如RTL动态仿真与FPGA硬件仿真相结合[11]、分阶段引入处理器局部建模[8]等.文献[9]采用功能覆盖率为导向的UVM验证方法对DUT进行验证,实现了内核验证所需的功能覆盖范围且验证平台可重用性好,但仿真速度存在局限性;文献[8]为提高验证收敛速度,在文献[9]方法的基础上对微处理器局部建模,在验证后期利用局部模型指导测试激励的生成,可快速完成对未覆盖功能点的验证,一定程度上加快了验证收敛,但平台的可重用性有所下降;文献[10]在FPGA上对微处理器进行硬件原型验证,仿真速度比文献[9]快且验证平台的搭建简单,但测试用例的随机性差、平台的可重用性差;文献[11]中RTL动态仿真与FPGA硬件仿真相结合的验证方式保证了验证平台的可重用性且极大地提升了验证收敛速度,但FPGA验证的可调试性差,对微处理器指令集的随机验证不够充分.综上,微处理器验证可以采取动态仿真与FPGA硬件验证相结合的方式,但需要对指令序列随机性做改进.

本文设计了一种适用于8bit RISC架构内核的验证参考模型,模拟内核指令集系统结构来满足指令的完全随机组合,同时实现内核存储空间的可参数化配置来提高可重用性.所设计参考模型集成到文献[11]所提方法的UVM平台中,应用到一款8位MCU的内核验证中,很好地保证了指令序列随机性,所有测试用例均仿真通过,代码和功能覆盖率均达100%.

1内核架构原理

精简指令集计算机(RISC)不同于复杂指令集计算机(CISC),其指令长度固定、指令数目精简.基于RISC架构的计算机结构更简化合理,且开发者可根据需求对指令集进行扩展[12].RISC-V是基于RISC原理建立的开源指令集架构,其架构简洁、指令集模块化且可扩展,是最具革命意义的开发处理器架构.RISC-V指令集大部分指令执行只需一个周期,配合流水线结构的实现使得内核程序执行速度更快[13-14].可由下面公式推导而得:

P=I·CPI·T(1)

其中,P为执行一段程序所需的总时间;I是这段程序所包含的总指令条数;CPI是每条指令执行所需的时钟周期数的平均值;T是内核参考时钟的周期.同一段程序,虽然RISC比CISC的总指令条数多,但CISC的CPI会比RISC大很多,且RISC的时钟周期比CISC小,所以程序总的执行时间RISC更短.且RISC-V架构对中断的响应速度更快.

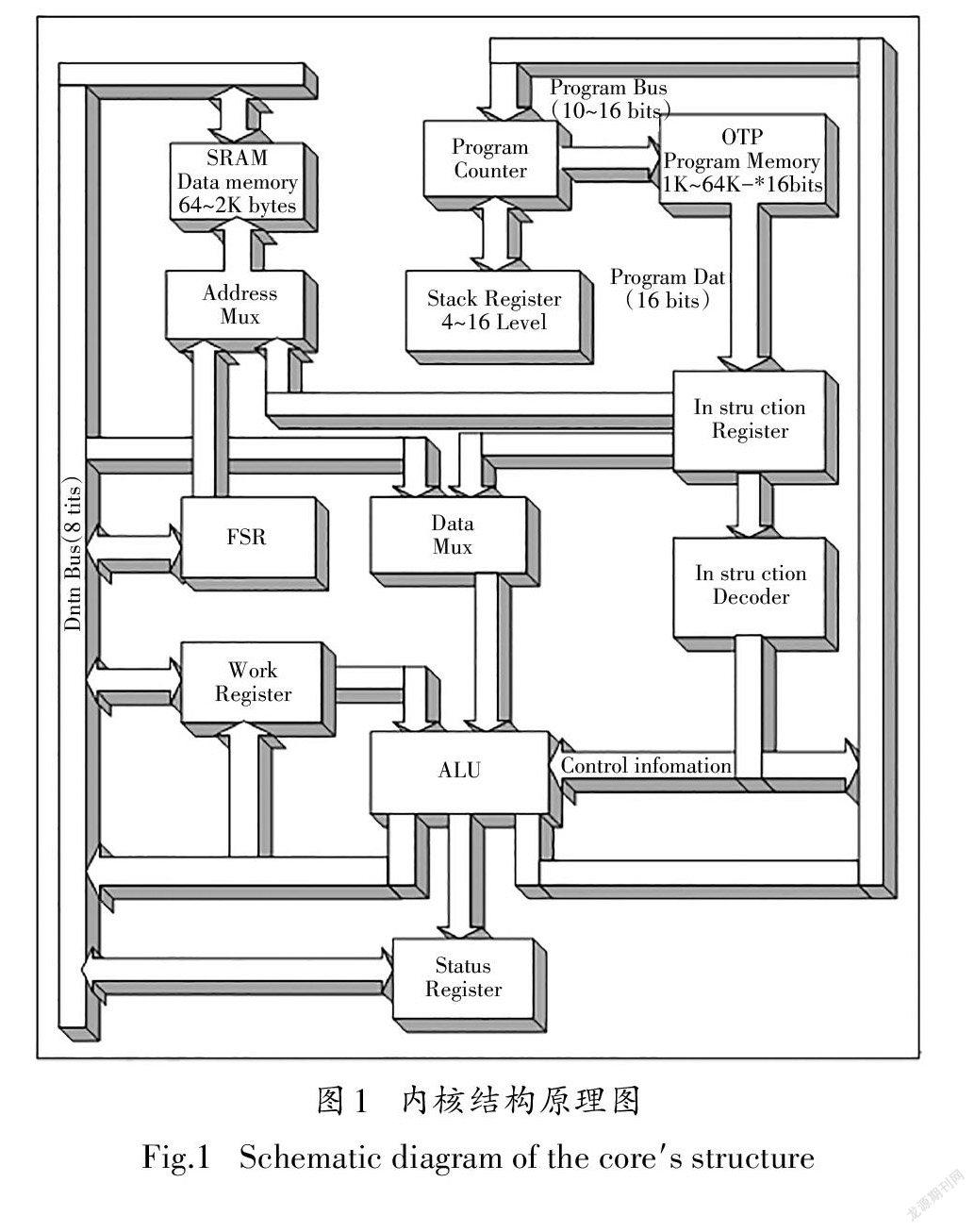

所研究内核是基于RISC-V架构的8位MCU,综合考虑芯片性能、成本及实际应用需求,其指令集在RISC-V指令集基础上进行了简化和删减,修改后的指令集仅有44条基础指令和6条扩展指令,大大简化了内核结构.图1所示为内核结构原理图.

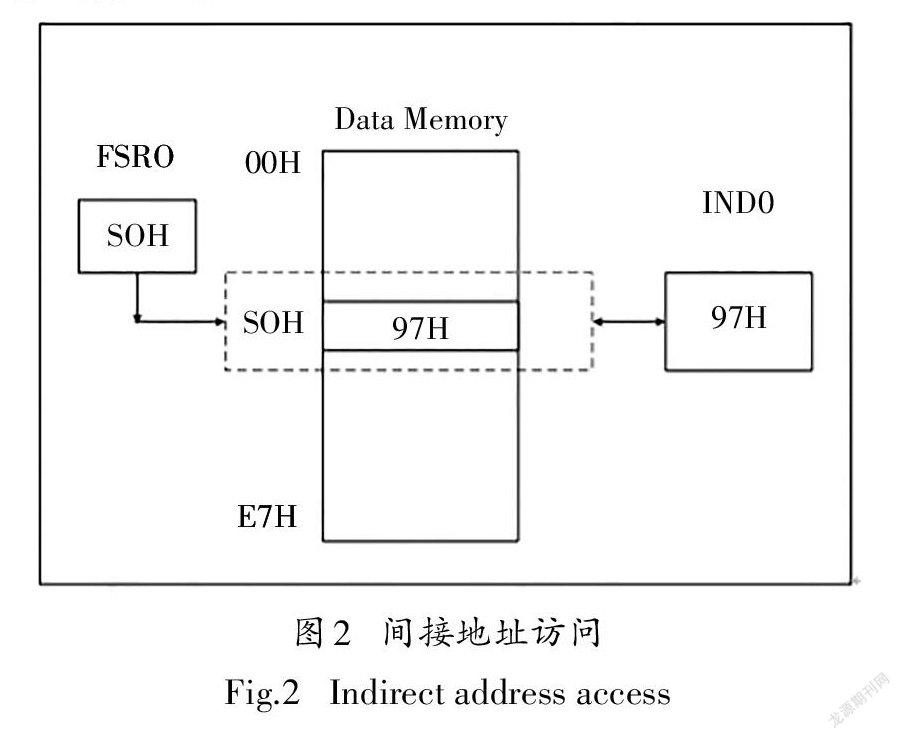

该内核有直接寻址和寄存器间接寻址两种访存方式,直接寻址即通过指令译码出的数据存储器地址进行读写操作,由于指令编码中数据存储器地址是9bits,所以寻址空间为512Byte,超出此范围的地址需通过切换PAGE进行访存.寄存器间接寻址是通过内核特殊寄存器IND/FSR对数据存储器间接访存,具体方式如图2所示.

由图2可知,内核从间接地址寄存器(IND)读数据,实际上是以FSR中的值为地址去读数据存储器;向IND写数据实际上是以FSR中的值为地址将数据写入数据存储器相应地址.

2验证参考模型设计

所设计参考模型的指令集是基于RISC-V构架基本指令集修改并扩展的,包括44条基本指令和6 条扩展指令,指令长度均为16bits,按操作分为位操作类、立即数操作类、字节操作类、跳转类和控制类五大类.表1给出了各类指令的编码方式.

为寻址方便,所研究内核设置了特殊功能寄存器,包括间接寻址寄存器(IND)、寄存器选择寄存器(FSR)、状态寄存器(STATUS)、工作寄存器(WORK)、全局中断使能寄存器(INTE)、PAGE选择寄存器(BSR)和PC加载寄存器(PCLOADL/PCLOADH).

2.1内核指令集的建模

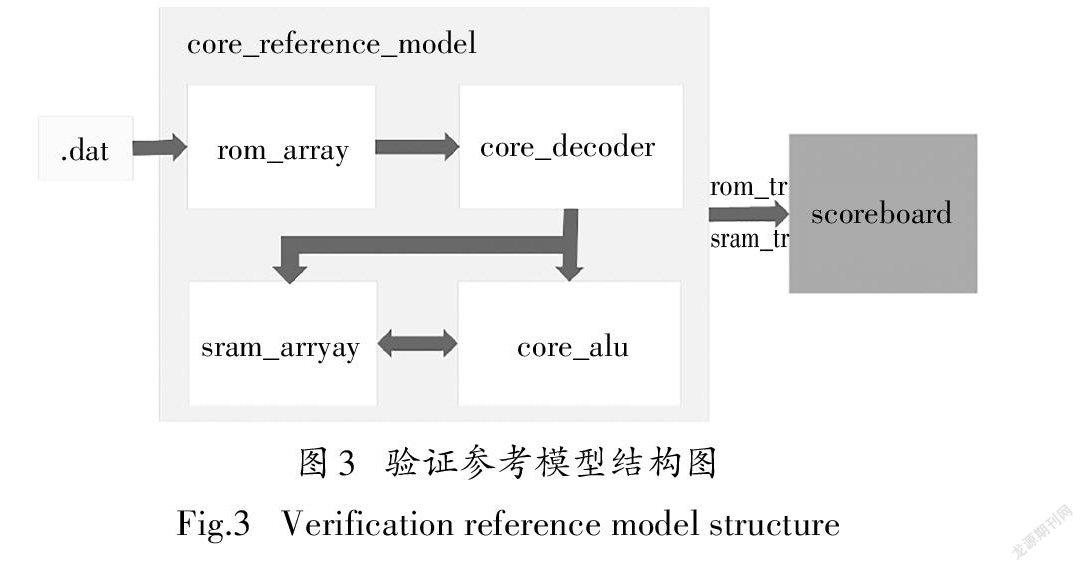

图3为本文所设计的8位内核验证参考模型的结构框图,为简化只给出主要组成部分和数据流通路.参考模型有四个主要的组件:程序存储器(flash_array)、数据存储器(sram_array)、指令译码器(core_decoder)和运算单元(core_alu),外部激励给到程序存储器,经过参考模型执行处理后改变相应地址的数据存储器数据并发送transaction(flash_tr/sram_tr)给UVM验证平台的计分板,作为DUT响应数据的期望值[15],实现原理后续展开讨论.

参考模型设计依据是内核指令集和指令执行流程即取指—译码—读取—执行/写回和,整个内部实现是按指令执行四个步骤来设计的.基于System Verilog语言,整个参考模型定义成一个派生自UVM基本类uvm_component的类.在设计实现前,首先对PC位宽、堆栈级数、堆栈起始地址等参数宏定义,并自定义了一个包含指令集所有指令的枚举类型供后续类的定义使用.

参考模型的类首先对变量进行定义,包括内核特殊寄存器、transaction、程序和数据存储器、PC堆栈和数据堆栈以及一些中间变量;接着声明、定义类的函数,主要是图3中参考模型组件对应的函数:取指、译码、读取、指令执行、写回函数.基于处理器结构原理,取指函数根据当前pc值从程序存储器取指存入IR寄存器,为配合跳转指令和长搬移指令执行还会预取指pc+1和pc+2;译码函数依据IR寄存器的数据,对照指令集编码将16位指令码译成具体指令确定后续执行内容;读取函数根据译码所得ram_addr访问数据空间获取指令操作数;指令执行函数根据译码结果执行操作或运算,并将要写回数据空间的数据加以缓存;写回函数依据具体指令是否需要写回,将指令执行后所得数据寫回相应地址.

参考模型模拟内核行为的整个过程是在main_phase函数中实现的,main_phase函数分别调用前述函数,模拟内核程序执行过程,并参照实际内核行为对异常情况加以处理,主要有非法指令复位和中断响应.

通过对内核指令集建模,参考模型实现了对内核指令集系统的模拟,可对内核指令集功能点黑盒验证,能够解决以往验证方法指令序列随机性差的问题,且结合perl脚本工具的使用,可自动化生成指令随机序列,减少了繁琐编写测试用例的工作量.

2.2存储指标可参数化配置的实现

为提高可复用性,参考模型对内核存储空间及堆栈级数等关键指标进行了可参数化配置设计.验证人员只需根据实际存储空间设置参考模型的相应参数,即可对目标类芯片不同存储配置进行验证.

利用UVM的cofig_db机制,在UVM验证平台顶层top_tb中执行set操作,根据内核存储指标配置相应参数的值;在验证参考模型中执行get操作,获取相应参数值,从而实现不修改参考模型即可满足不同存储空间的内核的验证.

验证参考模型中的代码实现如下所示:

uvm_config_db#(core_vif)::get(this,””,”core_vif”,pc_width);

uvm_config_db#(core_vif)::get(this,””,”core_vif”,sp_len);

uvm_config_db#(core_vif)::get(this,””,”core_vif”,RAM_addr);

3基于验证参考模型的内核模块级验证及结果

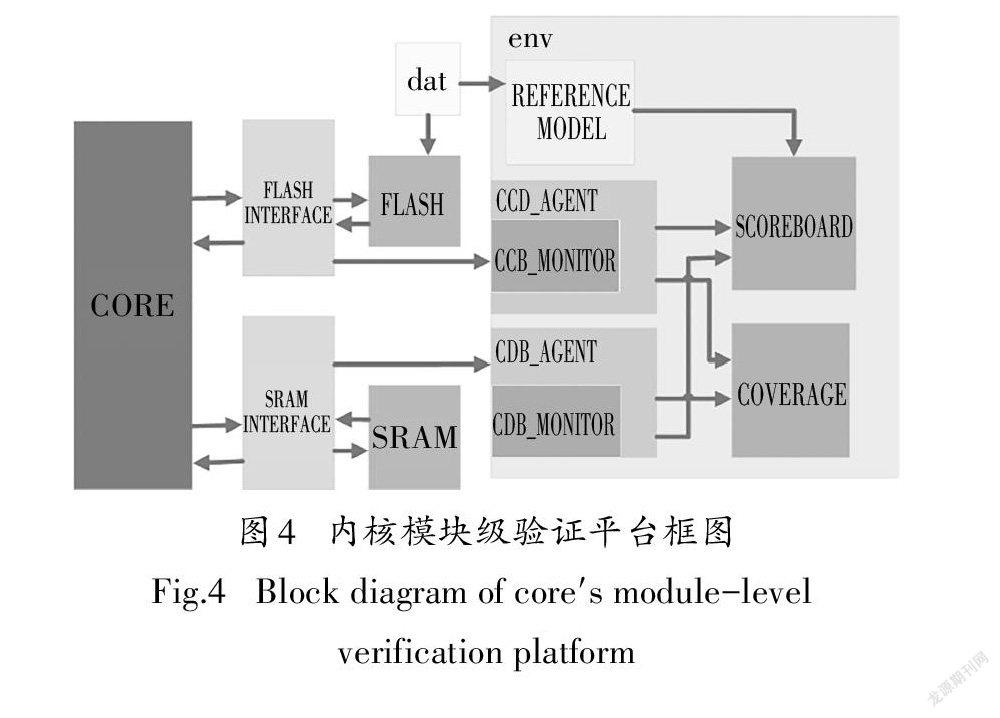

本文设计的内核验证参考模型已成功应用于一款基于RISC-V架构的8位MCU芯片的内核模块级验证中,该内核指令集包括44条基础指令和6条扩展指令,仿真验证是在Linux平台上用System Verilog 语言搭建的UVM验证平台上进行,所用仿真工具是synopsys公司的VCS,仿真波形和覆盖率的查看使用synopsys公司的Verdi,UVM驗证平台框图如图4所示[16].验证结果表明集成了本文所设计的内核验证参考模型的UVM仿真验证平台能够满足对8位内核的模块级验证需求,结合受约束随机激励生成技术对内核指令序列进行了完全随机组合验证.

图5为内核模块验证指令集随机测试用例的仿真波形图.

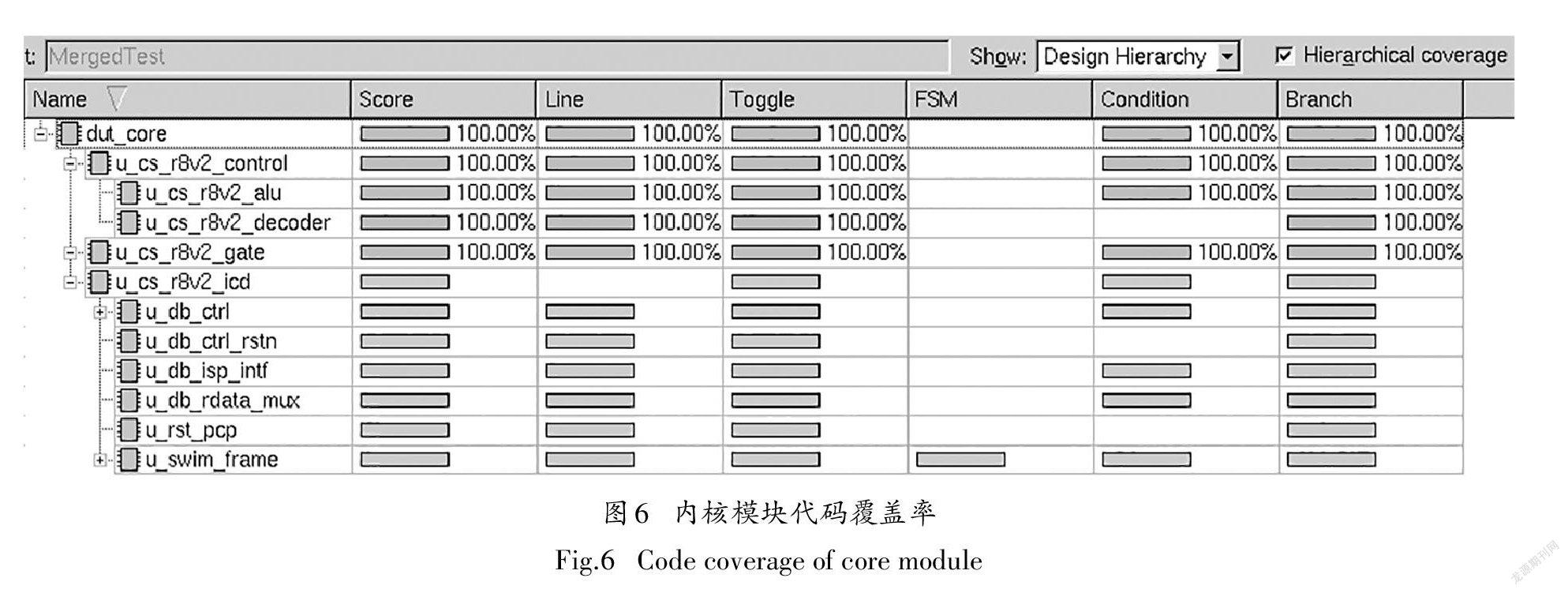

图6为内核模块验证用例回归后所收集到的加过滤文件的代码覆盖率,过滤部分均为与设计人员确认无法覆盖的,由图可知各项代码覆盖率均达100%,实现了内核验证所需的功能覆盖范围.

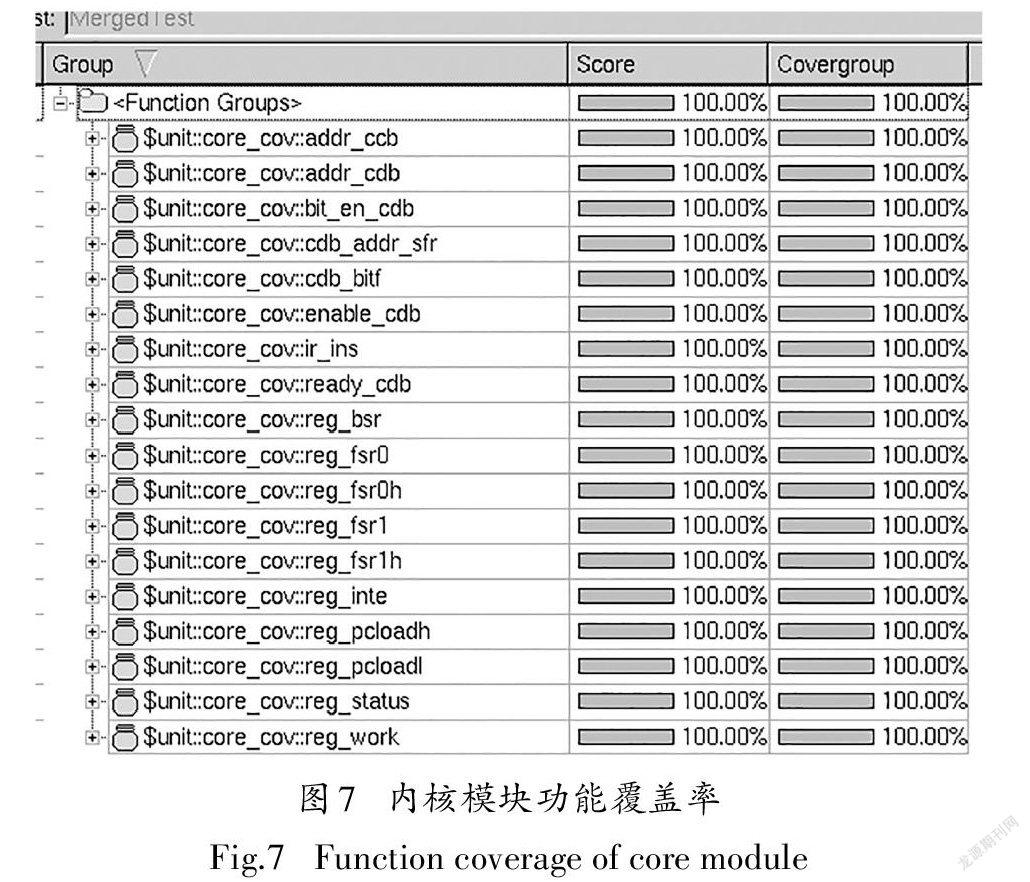

图7为内核模块验证的功能覆盖率,均达到100%.

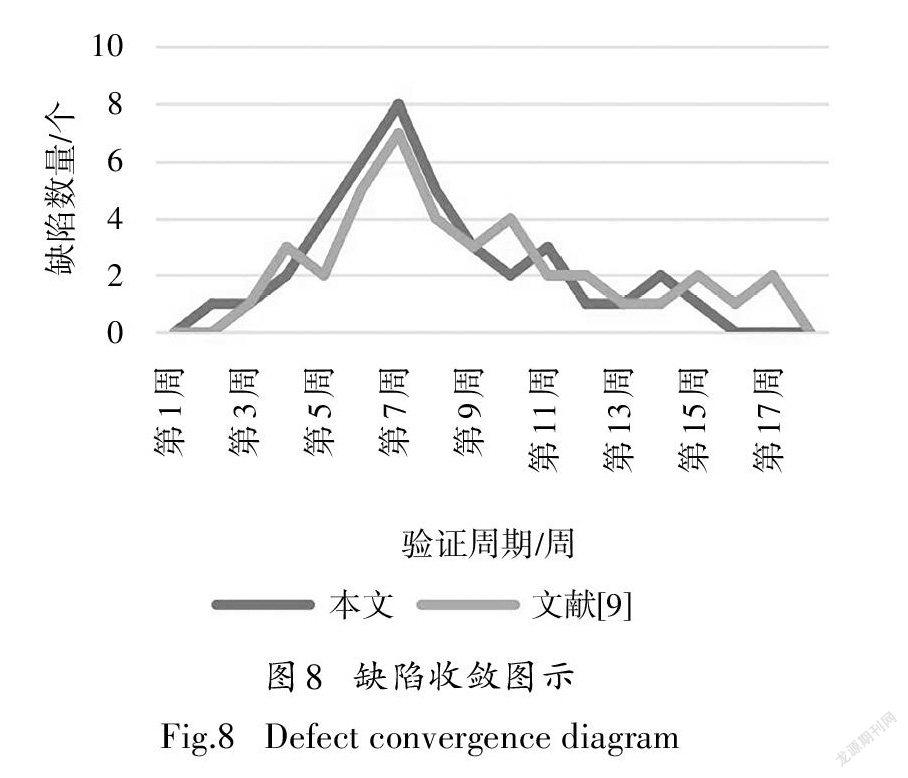

图8为本文所用验证方法和文献[9]的功能覆盖率为导向的验证方法分别对目标内核进行验证的缺陷收敛图示.

由图8可看到,随着验证工作的推进,内核模块的缺陷数量均呈现收敛状态,但本文曲线相比文献[9]的而言变化更平缓、收敛速度更快,且验证周期缩短了10%,说明集成了本文所设计参考模型的UVM验证平台具有更好的鲁棒性,且验证效率和完备性更好.

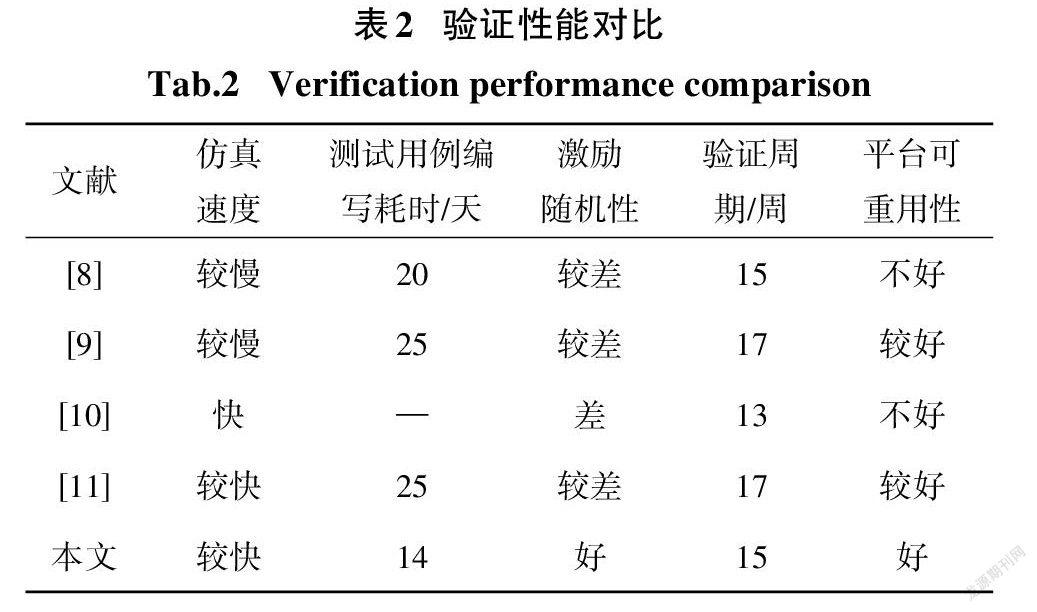

表2给出了基于本文验证参考模型和部分文献的方法,对同一DUT进行验证的性能对比结果,可以看出本文的验证方法仿真速度较快、激励随机性好、测试用例编写简单,且验证平台具有很好的可重用性.

图9为集成有本文验证内核的电源充电管理芯片的版图,采用华宏0.11μm工艺进行流片,芯片总面积为3.4 mm,系统时钟频率为24 MHz,流片测试结果表明,内核模块设计符合设计文档要求.

4结论

本文设计了一种适用于8位RISC架构内核验证的参考模型.对内核指令集验证建模提高了激励的可随机化程度,同时实现了内核存储指标的可参数化设置,使得参考模型可直接用于扩展或继承类芯片的内核验证.将验证参考模型应用到一款8位4级流水线的MCU芯片内核验证中,验证结果良好,最后所验证内核采用华宏0.11um工艺成功流片,证明了参考模型对内核验证的有效性.

参考文献

[1] CHUNG E S,HOE J C. High-level design and validation of the BlueSPARC multithreaded processor [J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2010,29(10):1459-1470.

[2] FAJCIK M,SMRZ P,ZACHARIASOVA M. Automation of processor verification using recurrent neural networks [C]//2017 18th International Workshop on Microprocessor and SOC Test and Verification (MTV). December 11-12,2017,Austin,TX,USA. IEEE,2017:15-20.

[3] LI Y Y,WU W C,HOU L G,et al. A study on the assertionbased verification of digital IC[C]//2009 Second International Conference on Information and Computing Science.May 21-22,2009,Manchester,UK.IEEE,2009:25-28.

[4] THALAIMALAI VANARAJ A,RAJ M,GOPALAKRISHNAN L. Functional Verification closure using Optimal Test scenarios for Digital designs[C]//2020 Third International Conference on Smart Systems and Inventive Technology (ICSSIT). August 20-22,2020,Tirunelveli,India.IEEE,2020:535-538.

[5]胡锦,谢立红,邹望辉,等.基于低功耗SoC的微型图像采集系统设计[J].湖南大学学报(自然科学版),2019,46(2):86-91.

HU J,XIE L H,ZOU W H,et al.Design of miniature image acquisition system based on low power system on chip [J]. Journalof Hunan University(Natural Sciences),2019,46(2):86-91.(In Chinese)

[6]DUTT N,JANTSCH A,SARMA S. Toward smart embedded systems:a self-aware system-on-chip(SoC)perspective[J].ACM Transactions on Embedded Computing Systems,2016,15(2):22.

[7]段青亚,黄士坦,靳荣利,等.SoC自动化验证方法的研究与实现[J].吉林大学学报(信息科学版),2010,28(3):231-237. DUAN Q Y,HUANG S T,JIN R L,et al. Study and implementation on method of SoC automatic verification[J] Journal of Jilin University(Information Science Edition),2010,28(3):231-237 (In Chinese)

[8]張良,易江芳,佟冬,等.使用局部建模的微处理器测试程序自动生成方法[J].电子学报,2011,39(7):1639-1644.

ZHANG L,YI J F,TONG D,et al Test program generation for microprocessor verification using local modeling strategy [J] Acta Electronica Sinica,2011,39(7):1639-1644 (In Chinese).

[9] WANG J Y,TAN N X,ZHOU Y F,et al. A UVM Verification Platform for RISC-V SoC from Module to System Level[C]//2020 IEEE 5th International Conference on Integrated Circuits and Microsystems (ICICM). Nanjing,China:IEEE,2020:242-246.

[10] PRASANNA K N,YELLAMPALLI S,CHETWANI R R Design and implementation of a Test Coverage Algorithm for verification and validation of a processor IP core[C]//2016 2nd International Conference on Applied and Theoretical Computing and Communication Technology(iCATccT)July 21-23,2016,Bangalore,India. IEEE,2016:652-656.

[11]张珩.通用处理器设计中硬件仿真验证[J].计算机工程与应用,2007,43(8):1-3

ZHANG H Hardware simulation for microprocessor verification [J]. Computer Engineering and Applications,2007,43(8):1-3 (In Chinese).

[12] WATERMAN A,LEE Y,PATTERSON,et al. The RISC-V Instruction Set Manual,Volume 1:User-level ISA[J]. EECS De- partment,2011,7(9):475.

[13] ZIMMER M,BROMAN D,SHAVER C,et al. FlexPRET:A processor platform for mixed-criticality systems [C]//2014 IEEE 19th Real-Time and Embedded Technology and Applications Symposium(RTAS). Berlin,Germany:IEEE,2014:101-110.

[14] GAUTSCHI M,DAVIDE SCHIAVONE P,TRABER A,et al. Near-Threshold RISC-V Core With DSP Extensions for Scalable IoT Endpoint Devices[J]. IEEE Transactions on Very Large Scale Integration (VLSI)Systems,2017,25(10):2700-2713.

[15] LI W,WANG X T. Functional coverage-driven UVM-based UART IP verification [C]//2015 IEEE 11th International Conference on ASIC. Chengdu,China:IEEE,2015:1-4.

[16] VINEETH B,TRIPURA SUNDARI B B. UVM Based Testbench Architecture for Coverage Driven Functional Verification of SPI Protocol [C]//2018 International Conference on Advances in Computing,Communications and Informatics. Bangalore,India:IEEE,2018:307-310.