SOI CMOS 电路稳态寿命试验后漏电失效分析

张宇隆 , 文 宇 , 郑广州

(国家新能源汽车技术创新中心,北京 100176)

0 引言

SOI CMOS 电路相对于体硅CMOS 电路,具有速度快、功耗低、集成度高、抗辐照能力强等优点,且彻底消除体硅CMOS 电路的寄生闩锁效应,在制备高性能ULSI、高压、高温、抗辐照、低压低功耗及三维集成电路等方面具有显著优势[1-3]。应用于航空、航天、汽车等高质量等级的电路,需要满足应用系统高可靠、长寿命的要求[4-6]。电路装机应用前,通常需要抽样进行包括稳态寿命试验在内的一系列可靠性试验,以验证电路的可靠性是否达到应用要求[7-8]。如果试验过程中电路发生失效,则需对其进行分析,确定失效原因并进行相应改进,从而确保电路的可靠应用。

针对集成电路或分立器件在可靠性试验后的失效问题,大量学者已开展过分析研究。如Liu等[9]针对VDMOS 在DC/DC 转换试验后的漏电失效进行了分析,推测导致该失效的原因为源极金属铝穿刺导致器件在高温偏置应力下发生漏电。Fu 等[10-12]分别针对或非门电路、功率MOSFET器件、电磁继电器在不同环境应力下存储后的失效进行了分析,确定了失效根本原因。席善斌等[13]对多模计数器老炼试验后失效进行了分析,认为静电损伤是导致其失效的原因,并对失效机理进行了剖析。

虽然学者们已经对分立器件和体硅工艺电路进行大量失效分析研究,但是针对SOI CMOS 电路在稳态寿命试验后的漏电失效探索研究较少。本研究针对SOI CMOS 电路在1000 h 稳态寿命试验后的漏电失效进行分析排查,确定失效根因,复现失效模式,并提出预防建议。对SOI CMOS 电路漏电失效提供的分析思路和方法,可为后续类似失效分析和预防提供借鉴和参考。

1 故障背景

针对一批SOI COMS 电路在稳态寿命试验后失效的样品开展失效分析。该样品采用DIP 陶瓷密封封装。稳态寿命试验条件依据GJB 548B 进行[7],试验温度为125 ℃,试验时间为1000 h。试验前各样品电参数测试全部合格。试验后,常温电参数测试发现2 样品发生输入端口漏电超标失效(>0.5 μA),其中1 件失效样品(编号为1#)输入端口漏电流为1.60 μA,另1 件失效样品(编号为2#)输入端口漏电流为0.97 μA。稳态寿命试验过程中曾发生试验室突然停电,导致试验设备异常掉电的情况,除此之外无其他异常情况发生。

2 原因分析

根据失效器件的失效模式,以“个别器件漏电流失效”为顶事件,从器件本身缺陷和外部应力异常两方面入手进行故障树分析,如图1 所示。共找出5 个可能导致顶事件发生的原因(底事件),即离子沾污、内部气氛不佳、芯片外表面污染、异常掉电致击穿和静电放电致失效。本失效分析基于先无损后有损的原则,先后进行异常掉电致击穿排查、离子沾污排查、内部气氛不佳排查、芯片外表面污染排查和ESD 致失效排查。

2.1 异常掉电致击穿排查

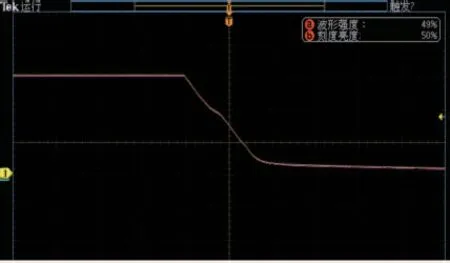

若1000 h 稳态寿命试验过程异常掉电是电源电压先断,信号电压后断,则样品有可能产生过电损伤,造成击穿失效。而该试验掉电是闪路过程,因稳态寿命试验设备电源和地之间有保护电容,瞬间掉电后信号电压先断,电源电压后断,因此不存在上述隐患。图2 给出工位掉电瞬间样品失效端口的电压波形情况,可以观察到电源电压掉电过程失效端口电压缓慢平稳下降,未出现尖峰等异常现象,因此,可以判定不是掉电过程导致样品漏电失效。

图2 工位掉电过程电压波形Fig.2 Voltage waveform during power off

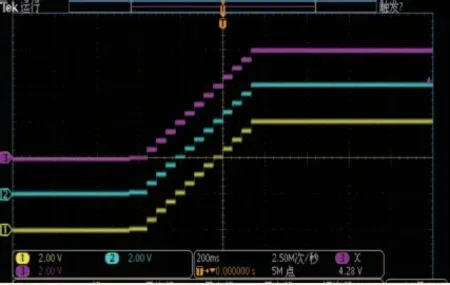

试验重新上电过程为电力恢复后手动正常上电。对2 件失效样品和1 件合格样品所在工位重新上电过程的电压波形进行捕捉,见图3。在重新上电过程中,样品所承受电压是缓慢上升的,上电过程未出现较大异常电压,因此可以判定上电过程不会导致样品漏电失效。

图3 工位重新上电过程电压波形Fig.3 Voltage waveform during power on again

2.2 离子沾污排查

芯片内部沾污离子(如Na+)在栅氧层中极易发生迁移,会造成表面反型或形成沟道,导致其输入漏电流增大。由于可动离子浓度极小,难以直接检测,因此采用模拟试验来识别离子沾污问题。若失效样品是由芯片内部存在离子沾污导致漏电增大,则高温存储后沾污离子会均匀扩散以致远离栅氧界面,失效样品漏电会减小,再经稳态寿命试验后,沾污离子在偏置电压作用下会重新迁移到栅氧界面,失效样品漏电流又会重新变大。

对1#样品进行28 h 的高温(125 ℃)存储,存储后其输入漏电流由1.60 μA 降低为0.47 μA。再对该样品进行96 h 的高温(125 ℃)稳态寿命试验,试验后样品输入漏电流并未变大,反而进一步降低为0.35 μA。可见,该失效样品输入漏电超标与芯片内部离子沾污无关。

2.3 内部气氛不佳排查

失效样品内部气氛不佳主要是由于样品内部存在含量超标的水汽。超标水汽在一定温度下会凝结成水膜,附着在芯片表面形成微漏电通道,导致样品输入漏电流增大。首先,取1#样品进行密封性测试,测试结果显示样品密封性合格,因此排除外部不良气氛进入样品内部导致漏电的可能。同时确保样品内部水汽等气体不会向外泄漏干扰后续试验判断。然后,对失效样品进行16 h/100 ℃高温烘烤后,测试其内部水汽含量,测试结果显示内部水汽含量为6.18×10-4,远低于规范要求值(<5×10-3)。可见,失效样品输入漏电流超标与器件内部气氛不佳无关。

2.4 芯片外表面污染排查

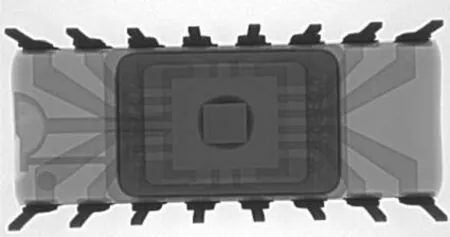

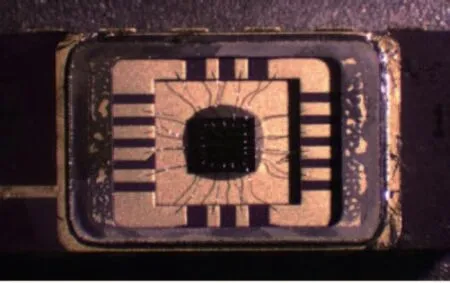

芯片外表面污染主要包括可动颗粒或任何其他封装过程中引入的杂质污染,各种污染物会使芯片及电极系统发生物理化学反应,进而可能导致样品输入漏电流超标失效。对2#样品用PTI4501 颗粒碰撞离子噪声检测仪进行检测,未发现样品内部存在可动多余物,排除可动多余物导致样品漏电的可能。利用X 射线探测样品内部结构(图4),样品内部结构完整,未发现芯片和封装存在材料或结构异常。采用机械法将样品开帽,通过光学显微镜检查样品内部形貌(图5),未发现样品内部结构及芯片表面存在可见沾污物等异常。综上所述,可以得出失效样品输入漏电流超标与芯片外表面污染无关。

图4 失效样品X-Ray 测试图Fig.4 X-ray test chart of the failed sample

图5 失效样品内部观察图Fig.5 Internal view of the failed sample

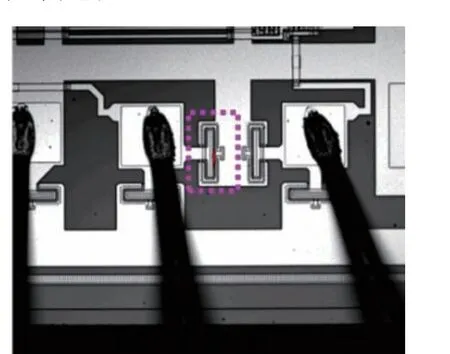

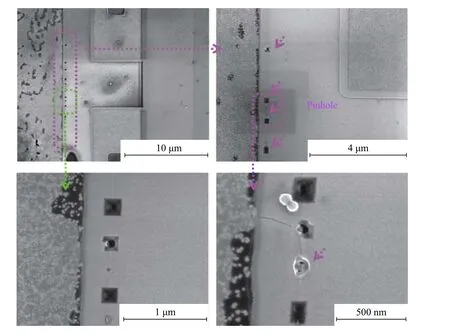

2.5 ESD 致失效排查

选取2#样品,通过光束诱导电阻变化(OBIRCH)对样品漏电点进行定位,定位结果见图6。由图可以看出,漏电位置为样品输入端接地侧二极管处。对失效样品进行去层处理,通过SEM 观察样品漏电点微观形貌见图7。可以看出,输入端二极管PN 结界面处存在明显的针孔损伤,这是比较典型的ESD 致损伤形貌[14]。ESD 可以产生几千伏甚至上万伏的电压,结合高温退火后漏电变化情况可以推测:一方面,形成的电场远远超过二极管临界击穿场强,PN 结发生雪崩倍增,部分元胞在PN 结拐角处等电场最强位置形成瞬间集中电流,集中电流导致局部温度瞬间升高,产生PN 结热击穿现象;另一方面,部分元胞在高压电场下仅发生雪崩倍增,产生大量电子空穴对,未进一步发生热击穿,这些电子空穴对在常温下并不会快速完全复合。因此,高温退火后二极管漏电流会有部分恢复,但不会完全恢复到试验前的正常状态。

图6 OBIRCH 漏电点定位结果Fig.6 Leakage location based on OBIRCH

图7 漏电点栅氧层SEM 形貌Fig.7 SEM image of gate oxide layer at leakage point

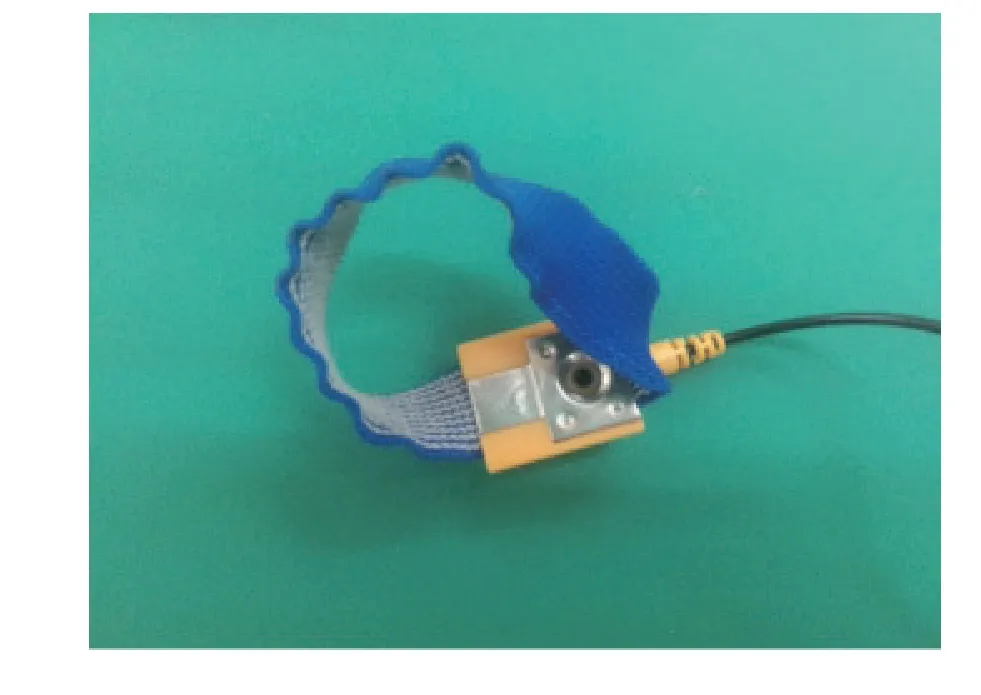

该批样品稳态寿命试验过程中,试验员佩戴防静电腕带和指套,且在离子风覆盖下完成。所用防静电腕带为尼龙编织材质,由于防静电腕带使用时间较长,产生应力松弛,在试验过程中存在与腕部接触不良的风险(图8)。

图8 防静电腕带Fig.8 Antistatic wrist strap

使用的指套为绝缘橡胶材质、非防静电专用指套,如图9 所示。该绝缘指套虽然电阻较高,但仍存在感应电压和充电电压,并且随着操作次数的增加,指套材料老化显著,绝缘性能下降,感应电、电阻漏电等很容易使接触的样品带电,存在ESD 隐患。综上所述,可以推断样品失效是ESD导致的。

图9 绝缘指套Fig.9 Insulated finger-cots

3 失效模式复现

ESD 导致的电路失效,漏电流通常较大,且伴有功能失效。而本研究显示ESD 也可以导致μA 级的局部漏电失效。分别通过ESD 专用测试设备模拟和原试验过程模拟复现上述ESD 失效模式,一方面印证上述失效分析结论,另一方面也证明该失效发生具有一定的普遍性。

3.1 ESD 测试设备模拟复现

取同批次合格样品1 件,该样品输入端漏电流小于0.5 μA。通过ESD 专用测试设备,模拟样品ESD 失效机理,依据MIL-STD-883 方法3015[15]对其进行3.3 kV 的人体模型静电放电试验,正负3 个脉冲,间隔时间为1 s。试验后测试样品电参数,发现样品输入端漏电流增大到4.50 μA,其他参数未见异常。对该样品进行48 h/125 ℃高温存储,存储后样品输入端漏电流降低到0.86 μA。再对该样品进行96 h/125 ℃高温稳态寿命试验,试验后样品输入端漏电流进一步降低到0.67 μA,与失效样品现象一致,失效模式得到复现。

3.2 原试验过程模拟复现

在稳态寿命试验过程中,可能引入ESD 损伤的环节主要为样品的装载和取下过程。取同批次合格样品6 件,各样品输入端漏电流均小于0.5 μA。在原稳态寿命试验场地,通过与失效样品相同的试验设备,模拟样品装载和取下过程,具体复现试验过程如下:

试验员佩戴接触不良的尼龙防静电腕带和非防静电专用指套,手持样品触碰金属桌面,模拟装载、取下样品时不小心将样品碰到金属桌面的情形。先通过摩擦或高压源对试验员人体充电,使其携带一定量值的静电,充电时试验员右手持样品;充电结束后,抓住样品一端,将样品另一端触碰桌面;取6 件样品进行试验,每件样品重复操作3 次。操作结束后,对各样品进行电参数测试,测试结果为:1 件样品发生输入端口漏电流超标失效,漏电流值为8.63 μA。对该样品进行48 h/125 ℃高温存储,存储后样品输入端漏电流降低到2.28 μA。再对该样品进行96 h/125 ℃高温稳态寿命试验,试验后样品输入端漏电流进一步降低到1.95 μA,与失效样品现象一致,失效模式得到复现。

4 结论

1)ESD 易使SOI CMOS 电路输入端二极管产生针孔损伤,导致电路产生较小电流的漏电,漏电等级通常为μA 级,且该漏电在高温退火后会有部分恢复。

2)SOI CMOS 电路为静电敏感型电路,在试验过程中,即使试验员按要求佩戴防静电腕带和指套,若防静电腕带或绝缘指套状态不佳,仍易引发样品ESD 失效。

3)建议试验过程中选用全金属防静电腕带和防静电专用指套,若选用尼龙编制腕带,必须定期更换。