基于FPGA的DDS信号发生器设计

董殿国,侯文

(中北大学 信息与通信工程学院,山西太原,030051)

0 引言

随着现代电子技术的飞速发展,直接数字频率合成DDS技术逐渐被广泛使用,从其技术理论上看,具有灵活性高、变频速度快、变频简单等优点。从实际效果来看,变频时分辨率高,相位噪声低,电路集成度高、频率稳定等优点。该技术已经逐渐被应用到现代雷达、导航、遥感、现代仪器仪表等关键领域。

使用DDS技术产生任意频率波形的方案主要有三种。第一种是直接使用高性能专用DDS集成电路芯片,比如AD9833,此种方案的优点是产生的波形频率准确,变频时分辨率高,直接使用通讯协议控制输入。缺点是,可以产生的波形类型受限,只有特定的几种,且内部配置灵活性很低。第二种是使用单片机实现DDS技术,此种方案在低频时配置较为简单,易于实现,在中高频时配置容易受到其他模块影响,严重影响波形频率精度。第三种是基于现场可编程门阵列FPGA来实现,此种方案灵活性较高,配置简单,易于实现,且变频范围广,分辨率高,唯一缺点就是,浪费FPGA内部未使用资源,造价高昂[1]。

1 DDS基本原理和核心设计

■1.1 DDS基本原理

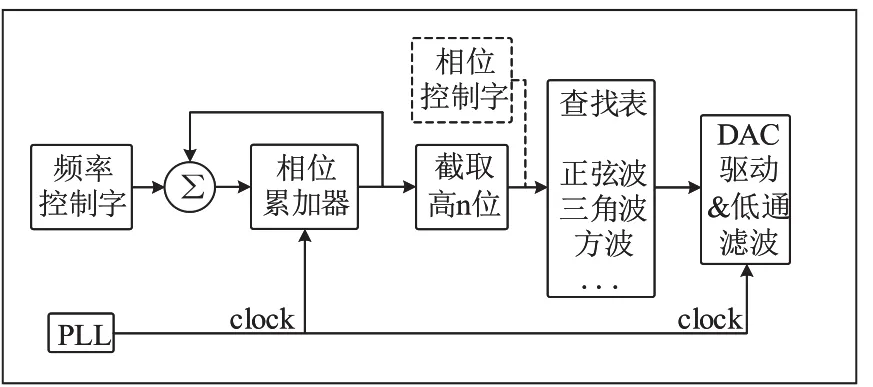

DDS技术原理框图如图1所示,主要有以下关键几部分组成,N位相位累加器、频率控制字、相位控制字、ROM查找表和时钟源等。

图1 DDS结构原理图

相位累加器在高频时钟下以频率控制字的字长K做累加。累加后的相位累加器值通过高位截取后变为相位控制字,相位控制字即为查找表的地址。在查找表中即可找到对应波形的多位数字输出值。这就是DDS基本工作原理。若要输出波形,将输出的多位二进制数字输出通过D/A转换输出对应的模拟电压信号,再通过一个低通滤波器输出平滑的曲线[2]。

■ 1.2 DDS核心设计

若要实现更高的频率分辨率和精度,共有两种方式,第一,将查找表中的波形数据取的分辨率更高,取样点的数据更多,这就意味着增加等倍的存储空间;第二,增加相位累加器的位数。事实上,典型的DDS系统会使用非常“长”位数的相位累加器,比如28位、32位甚至36位,来实现高精度和高分辨率的信号输出频率。在FPGA内部所使用的硬件资源来看,只是多使用几个寄存器,但是对其内部资源来讲,影响微乎其微。但是从其实际意义上看,可以大大提高其频率的精度和分辨率[3]。

表1中,f1为外部时钟输入经过倍频后的输出频率为120MHz,f2为外部时钟输入经过PLL倍频后的输出频率为500MHz,波形可调的最低频率即为频率的分辨率。

表1 不同情况下频率可调节范围和分辨率

如表1所示,相位累加器位数更高,其对应的频率分辨率越高,系统主频经过倍频后的频率越高,输出波形的上限频率越高。

需要注意的是,查找表地址为8位,比如当f1=120MHz时候,在不同累加器位数下,其可调的波形分辨率不同,但是120M/28=468 75kHz是一个临界值,当输出频率小于等于468 75kHz时候,输出的波形特征则可以完全还原查找表中的波形数据点;当输出的波形频率大于468 75kHz时候,频率越高,输出的波形无法还原查找表中的波形数据点,还原度越来越低,波形特征越来越不明显。同样的对于f2=500MHz时候,500M/28≈1 95MHz也是可以保持原查找表中波形数据点的最大频率[4]。

2 系统硬件设计

■2.1 硬件整体方案

函数信号发生器的硬件系统主要包括MCU控制电路,FPGA构成的DDS发生器、DAC转换和低通滤波电路,及一些用于输入输出的器件等。

按键输入和LCD输出显示主要由MCU负责控制,MCU然后将输入的信号运算处理后发送给FPGA,FPGA根据输入的各种参数在ROM表中寻址,同时输出对应控制的波形、频率和幅度的数字信号,最后经过DA转换为对应的模拟电压信号,在经过一个低通滤波器使得模拟电压信号变得平滑。

■ 2.2 硬件模块电路

系统的硬件电路主要分为两个部分,一是系统主控电路,二是DDS信号发生器电路。

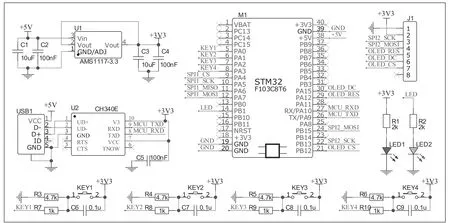

系统主控电路包括以STM32F103C8T6为主控的最小系统板、四路用户按键输入、OLED显示屏输出(SPI)、UART通信连接上位机、硬件SPI连接FPGA负责信号数据传输,如图2所示。

图2 系统主控电路

DDS信号发生器电路,其中的FPGA模块的核心芯片为Lattice LCMXO2-4000HC-4MG132,其模块上内置8路输出LED指示灯、4路按键输入、4路拨码输入和两位数码管输出灯资源。DAC芯片采用3PEAK的高速10位DAC芯片3PD5651E,采样速率125MSPS,CMOS数模转换器。本系统中采用12MHz的外部晶振经过PLL倍频为120MHz小于DAC芯片的最大采样速率,符合使用要求。

3 系统软件设计

■3.1 MCU程序流程设计

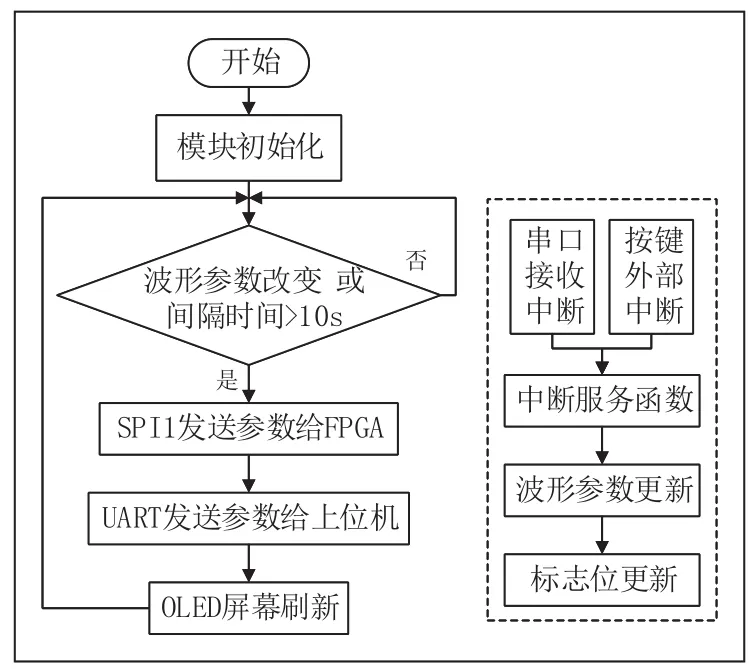

MCU主控制器主要负责系统中各个子任务的任务调度,系统的程序流程如图3所示,系统上电后先对各个模块进行初始化,包括串口初始化、OLED显示屏对应SPI1外设初始化、FPGA的SPI2外设初始化、按键和LED输入输出初始化等。

图3 MCU程序设计流程

程序中共有两个自定义的中断源,串口接收中断和按键的外部中断,按键的外部中断用于改变波形的相关参数对应的各个全局变量;而串口接收中断用于接收来自上位机中的信息,一类是波形参数对应的全局变量同步和参数显示,另一类是接收自定义波形数据表,并且通过SPI硬件通信接口实时存入FPGA的ROM模块中。此处有一个关键问题,上位机中波形参数的改变与显示,硬件上波形参数的改变和显示器的显示、程序内部波形参数对应的全局变量,以及波形的实际输出参数,在程序的运行过程中,需要时刻保证这四个模块中波形参数数据的同步。即先判定数据的输入输出属性,在每一个输入模块中添加波形参数更新标志位,实时更新程序中的全局变量,然后再根据参数对应的全局变量,随即更新参数更新来源模块之外的参数显示模块即可以实现四个模块的实时同步。

在MCU主程序的主函数中,主任务即为循环判断波形参数的全局变量是否改变,若改变则对串口传输上位机显示、SPI2对应的OLED显示屏显示、SPI1对应的FPGA三个模块做刷新处理;若未改变,则在间隔时间大于10s时候做刷新处理来降低容错率。

■3.2 FPGA模块设计

在整个系统中,FPGA模块主要负责DDS核心数字变频技术的实现。主要包括,PLL模块、SPI通讯接收模块、数据转换模块、DDS累加器模块、ROM查找表模块、幅度变换模块等。总共例化了四个波形数据的ROM,其mif文件通过MATLAB软件编写,然后调用IP读取。但是由于FPGA内部ROM资源限制,只能采用相位截断方法取高n为作为查询地址使用。

FPGA的DDS系统模块设计,主要由SPI通讯接收模块负责接收MCU传输的波形参数,包括波形类型、波形频率和波形幅度等。然后由数据转换模块负责将对应的波形类型,频率、相位、幅度转换为相应的频率控制字和相位控制字,最后将控制字直接输入DDS累加器模块中,相位累加器在120MHz的时钟信号下产生采样地址,通过波形类型选择选择对应的ROM查找表模块。在ROM模块中存储有正弦波、三角波、方波等常见波形的10位数字信号量,根据波形类型查找对应的10位数字信号值并输出到幅度变换模块。幅度变换模块同时根据输入的幅度设定值来输出对应的10为数字信号量。

FPGA不同于MCU的串行运行机制,FPGA内部是通过组合逻辑和时序逻辑所构成的并行运行机制的电路模块。所以在很多需要串行运行的模块中,就需要添加各种标志位或者状态机来实现。其中,SPI通信接收模块、数据转换模块、幅度变换模块都有关键的完成标志位,方便开启下一级模块使用。

■3.3 上位机软件设计

上位机软件使用NI公司的Labview软件开发,Labview以其使用简单、图形化的编程方式、功能模块封装度高、对各类硬件采集卡和常见的标准接口适配性高等优点而收到广大工程师和相关从业者使用。通讯方式使用串行通信UART串口连接,波特率115200,停止位1位,无奇偶校验位。为了提高调节各类参数和数据同步的响应时间,通讯协议使用自定义方式,第一位功能码,代表此时调节的参数类型,第二位到第九位为对应的参数值,使用ASCII字符传输,第十位为CRC校验位,校验数据传输。最后一位为结束字符,用于判断串口传输是否完成。

上位机软件主要分为两个模块构成,一是串口的发送和接收模块,主要在系统的串口控件处发送和接收相关数据;二是数据处理模块,主要将对应的信号参数数据实时转换到对应的控件显示上,或者将对应的控件显示数据编码准备发送。

由于在实际测试实验中所需的实验波形多种多样,且FPGA中数据存储资源有限,所以就需要在上位机软件中集成可以实时传输自定义波形数据的功能,这就是上位机软件中另一个主要功能,由于Labview软件可以直接与MATLAB脚本做混合程序设计,所以可以先通过在MATLAB中生成所需要波形的mif数据文件,直接在Labview上位机中导入生成所需的波形数据,完成自定义波形数据导入功能。

4 结果分析

■ 4.1 基本功能实现

信号发生器的幅度和频率等相关参数可以实现板载的手动调节,同样也可以连接计算机在上位机的视图中调节使用。需要注意的是,上位机调节和板载调节并不是简单孤立的,双方在不同参数的调节过程中是同步的。

■ 4.2 性能分析

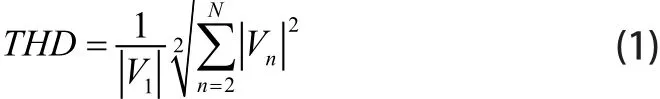

以信号发生器输出正弦波为例,输出不同频率的正弦波来分析其谐波失真(THD)。在此次测量实验中,使用泰克MDO32频谱分析仪(模拟通道带宽1GHz、采样率2 5GS/s)来测量信号发生器输出正弦波时,基波之外的高次谐波分量,来计算其谐波失真[5]:

在实验测量中,无法计算所有的高次谐波分量,只计算了8次谐波分量,所以在(1)式中N=8。实验测试结果如图4所示,横坐标为频率测试范围,从1Hz到10MHz。正弦波的THD值在局部上有所波动,但是在整体上趋于平稳。即该信号发生器的总谐波失真≤-10dB。

线性度是描述三角波的一个重要参数。在参数性能测试实验中,本文使用NI公司的PXI-6115多功能IO采集卡(最大采样率10MS/s)采集三角波在不同频率下的波形数据样点,并计算三角波在不同频率下的线性度。

在三角波的线性度性能测试实验中,标定了三角波的对称性为50%,幅值为3Vpp,频率从1Hz~1MHz范围,采集其样点数据,并做数据分析,计算其线性度。从增长趋势上来看,信号的频率越高,其线性度越差,但是从频率的整体范围上来看,其线性度一直保持在1%以下。符合系统预期的三角波线性度要求。

■ 4.3 性能总结

信号发生器的最高频率以正弦波输出的最高频率为12MHz;DAC芯片的采样率为125Msps,但是FPGA的内部主频经过PLL倍频后为120MHz,所以该信号发生器的采样率为120MSa/s;FPGA的数字信号量输出为10bits,且DAC芯片也为10bits,则信号发生器的垂直分辨率为10bits,系统内置常见的波形,正弦波、三角波、方波等,但是可以根据需要,重新生成任意波形数据样点保存后并输出。

5 结束语

本文基于DDS技术,使用MCU和FPGA联合设计的信号发生器,经过实验各种性能测试,结果表明,该信号发生器精度高,稳定可靠,噪声小,可以在各种实验室和工业场合使用。但是,也存在波形幅度较小和频率较高时,波形失真明显,需要进一步改进。