准分子激光低抖动延时同步系统

胡泽雄, 游利兵, 寸超, 王宏伟, 范军,王琪, 张艳琳, 方晓东,3

(1 中国科学技术大学环境科学与光电技术学院, 安徽 合肥 230026;2 中国科学院合肥物质科学研究院安徽光学精密机械研究所,安徽省光子器件与材料重点实验室, 安徽 合肥 230031;3 深圳技术大学新材料与新能源学院, 广东 深圳 518118;4 合肥工业大学电子科学与应用物理学院, 安徽 合肥 230009;5 深圳盛方科技有限公司, 广东 深圳 518173)

0 引 言

准分子激光器是目前紫外波段输出功率最大的激光器件,在工业、医疗、科研等领域均有广泛的应用。在科研领域中,准分子激光器可用于材料科学、表面科学和光谱学等学科的研究,如激光剥蚀、激光诱导荧光、脉冲激光沉积;在工业领域中,其主要集中应用于微加工和材料表面改性等方面,如半导体光刻、低温硅退火、高密度电路板制作以及布拉格光栅制作等;在医疗领域中,准分子激光器主要应用于眼科和皮肤病治疗[1]。准分子激光器具有宽频带和工作介质密度低等特性,在放大超短脉冲方面表现出独特的优势。固体掺钛蓝宝石激光器输出红外飞秒脉冲,将该脉冲直接进行频率转换或将其先进行放大再利用频率转换技术可得到紫外脉冲激光,将该紫外脉冲激光作为种子光,再利用准分子激光器实现放大,可将微焦量级飞秒紫外激光脉冲放大到毫焦级大能量输出。而准分子激光器作为放大器实现对种子光的放大,要求飞秒激光器和准分子激光器在时间上精确同步,即种子光与准分子激光的快放电同步,从而使种子光进入准分子激光器时处于最佳增益状态[2]。

目前国外的脉冲延时设备技术指标高且功能完善,应用普遍性强,如美国BNC 公司生产的745T 等产品,但这些设备没有涉及到温度等因素对元器件的影响,不具备反馈调节的功能。同时,这些设备一般是电信号输入输出,没有考虑在准分子激光器高电磁干扰环境下运行的情况,不能很好地满足准分子激光器与外部设备的同步需求。国内对于脉冲延时同步系统的研究基本是由高校和研究所等科研机构进行,多用于特定设备,如超高速分幅相机等[3]。对于准分子激光延时同步系统大多采用内触发方式,同时延时精度较低,最高为1 ns[4],目前针对准分子激光器与其他设备之间外触发脉冲的高精度延时同步系统的研发尚未有深入的研究。本文针对脉冲延时的精度和抖动问题展开分析和研究,设计和研制了一种低抖动的延时同步系统,以满足准分子激光器与飞秒激光器同步的要求。

1 准分子激光低抖动延时同步系统整体设计

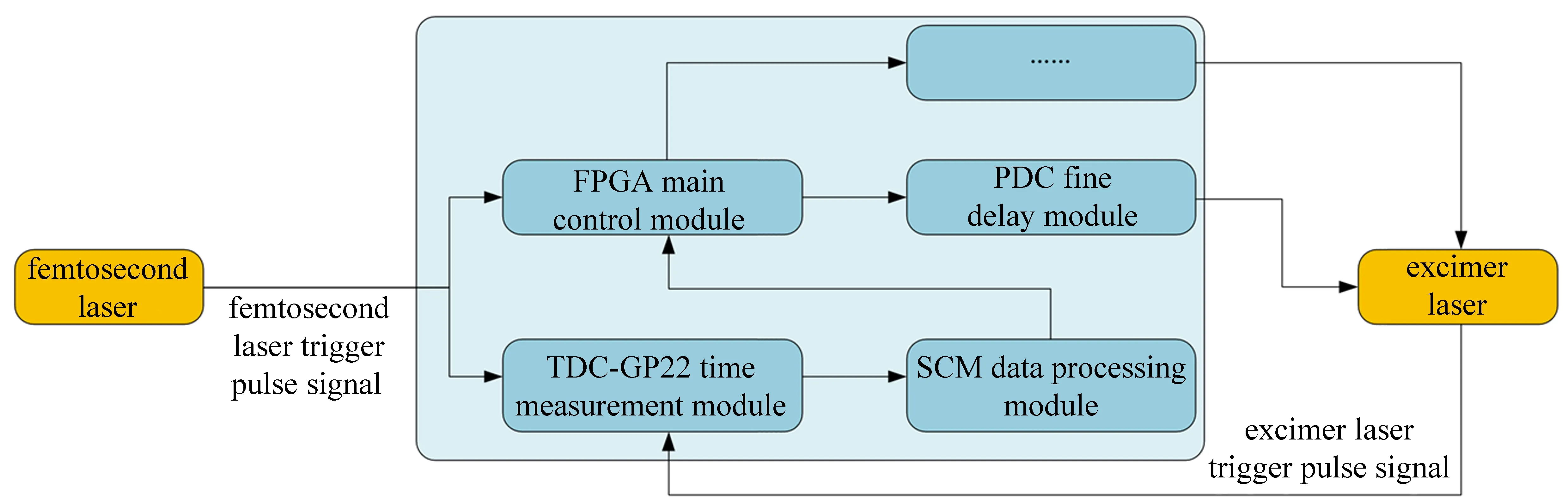

如图1 所示,准分子激光低抖动延时同步系统主要由FPGA 主控模块、可编程延时芯片(PDC)细延时模块、TDC-GP22 时间测量模块与单片机(SCM)数据处理模块组成。FPGA 主控模块用于捕获外部触发信号上升沿、对外部触发信号进行10 ns 步进的粗延时、处理PDC 细延时模块需要接收的数据、接收单片机处理后的时间差信号以及控制准分子激光器充放电等;PDC 细延时模块实现外部触发信号10 ps 步进的细延时,同时将延时后的准分子激光触发脉冲信号作为光信号输出;TDC-GP22 时间测量模块实现对飞秒激光器触发信号与准分子激光器触发信号时间差的测量,同时将时差数据通过串行外设接口(SPI)发送给单片机;单片机数据处理模块实现TDC-GP22 时间测量数据的读取并进行处理,再将处理后的数据发送给FPGA 主控模块。

图1 准分子激光低抖动延时同步系统框图Fig.1 Block diagram of time-delay synchronization system with low jitter for excimer

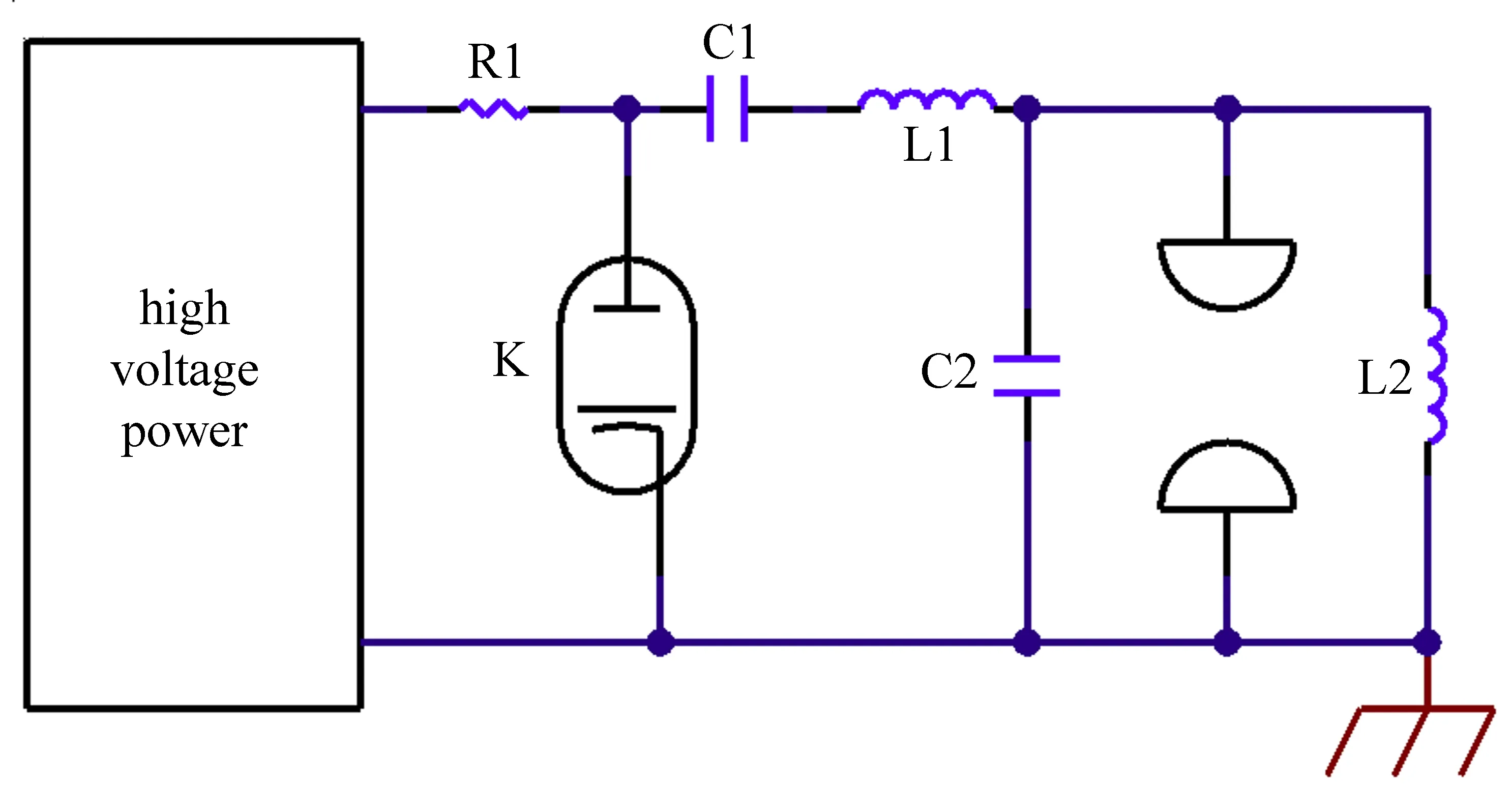

目前常见的准分子激光器放电回路如图2 所示。高压电源在充电使能信号作用下对储能电容C1 充电,当C1 上的电压值达到充电信号设定的电压值时,高压电源停止工作,此时储能电容C1 的电压保持不变;随后准分子激光触发脉冲信号控制闸流管K 导通,C1 上的电荷向放电电容C2 转移;当C2 两端电压上升到临界值时,放电腔的工作气体被击穿放电,产生准分子激光输出[5,6]。在这个过程中,当种子光进入准分子激光放大区时,准分子激光需要精确同步放电,而准分子激光放电是通过准分子激光触发脉冲信号控制闸流管K 导通来控制的,即需要控制种子光与准分子激光器触发脉冲信号的时序同步。由于气体击穿需要高电压、大电流,在准分子激光放电过程中会带来强电磁干扰[7],故而系统的输入输出信号均通过光纤进行信号传输,从而有效抑制准分子激光电磁干扰对系统的影响。

图2 准分子激光器的典型放电回路Fig.2 Typical discharge circuit for excimer lasers

2 FPGA 与可编程延时芯片模块设计

2.1 FPGA 主控模块设计

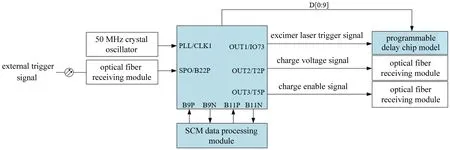

FPGA 主控模块的设计如图3 所示,其核心是处理芯片,处理芯片的外围电路包括光纤发送模块、光纤接收模块、电平接收模块等。FPGA 通过锁相环(PLL)电路将外围的50 MHz 的主频晶振倍频到200 MHz;FPGA 利用内部逻辑门产生不同频率的充电电压信号,通过OUT2 输出口发送给光纤发射器以完成电光转换,将充电电压信号以光信号形式发送给准分子激光器;FPGA 接收外部触发信号并捕获其上升沿,通过对外部触发信号频率的测算控制充电使能信号的频率,通过OUT3 输出口发送到光纤发射器完成电光转换以光信号形式发送给准分子激光器,使得准分子激光器在下一个脉冲触发信号到来前完成对充电电容C1 的充电,从而降低充电电容长时间处于充电状态对闸流管寿命的影响。通过200 MHz 的PLL 时钟,利用FPGA 内部的逻辑门计数器实现对10 ns 步进的粗延时[8],将粗延时后的准分子激光触发信号通过OUT1 输出口发送给可编程延时芯片模块,同时通过D[0:9]控制可编程延时芯片模块细延时时间。

图3 FPGA 主控模块设计框图Fig.3 Block diagram of FPGA main control module design

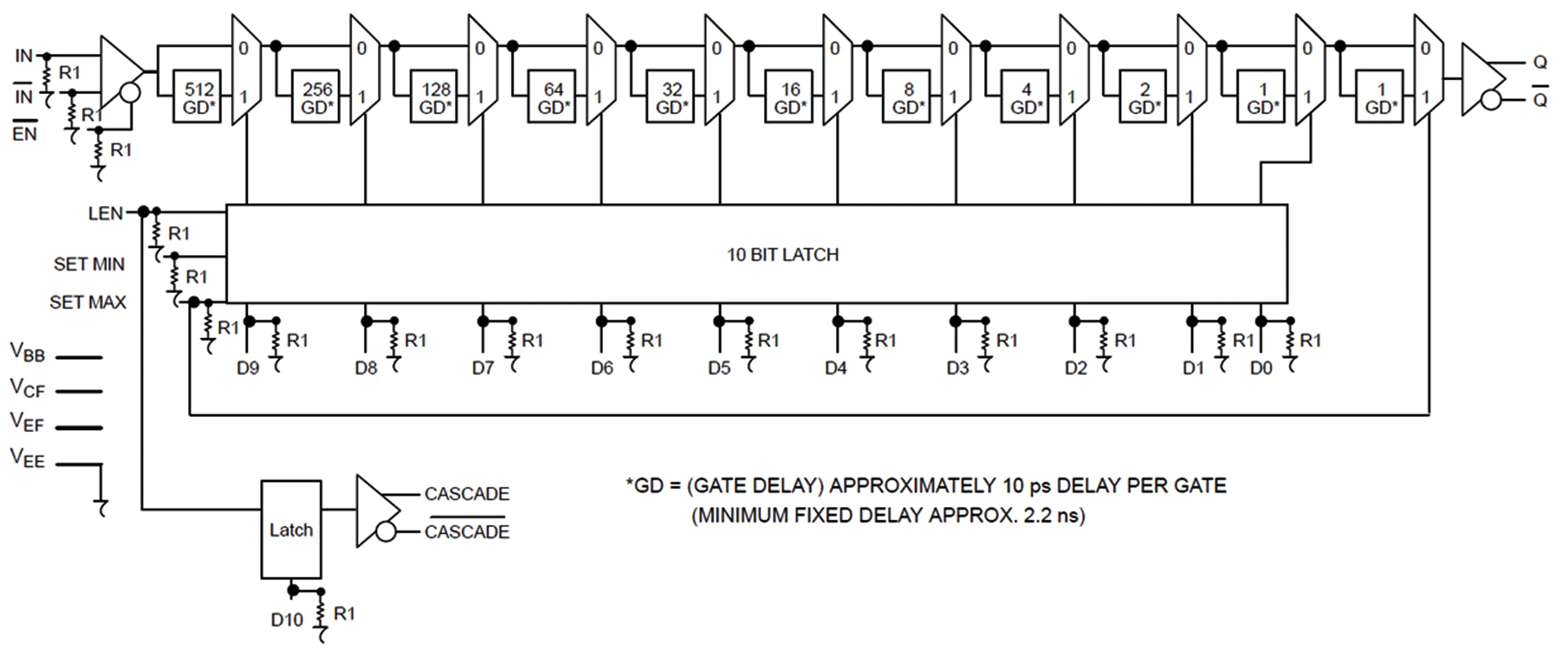

2.2 可编程延时芯片模块细延时设计

可编程延时芯片模块细延时部分通过安森美公司生产的MC100EP195 芯片完成10 ns 内的时间延时,该芯片可以实现在2.2∼12.4 ns 内以10 ps 步进精确调整延时时间,MC100EP195 的内部逻辑图如图4所示[9]。延迟单元包含一个可编程门阵列和一个多路复用器。借助控制信号LEN 在10 条输入数据线D9-D0 中设置所需的延迟时间,脉冲信号从输入端到输出端的延时时间为

图4 MC100EP195 可编程延迟芯片的逻辑图Fig.4 Logic diagram of the MC100EP195 programmable delay chip

式中:D为数据线D9-D0 的组合输入,其值为20∼210−1;ts为其延时步进;t′为固定初始延迟时间,这是芯片内置的多路复用器导致的,t′=2.4 ns。故而MC100EP195 的可编程延时时间约为2.2∼12.4 ns。若延时10 ps,则设置D9-D0 的值为0000000001;若延时1 ns,则设置D9-D0 的值为0001100100[10]。

MC100EP195 采用低压正发射极耦合(LVPECL) 电平传输信号, 使用安森美公司生产的MC100LVELT20 芯片, 将FPGA 粗延时后发送给可编程延时芯片模块的触发脉冲信号由LVCMOS 电平转换为LVPECL 电平,使用安森美公司生产的MC100ELT21 芯片将可编程延时芯片细延时后输出的触发脉冲信号由LVPECL 电平转换为TTL 电平,并发送给光纤发射器转换成光信号作为低抖动延时同步系统的输出信号[11,12]。

3 TDC-GP22 时间测量模块设计

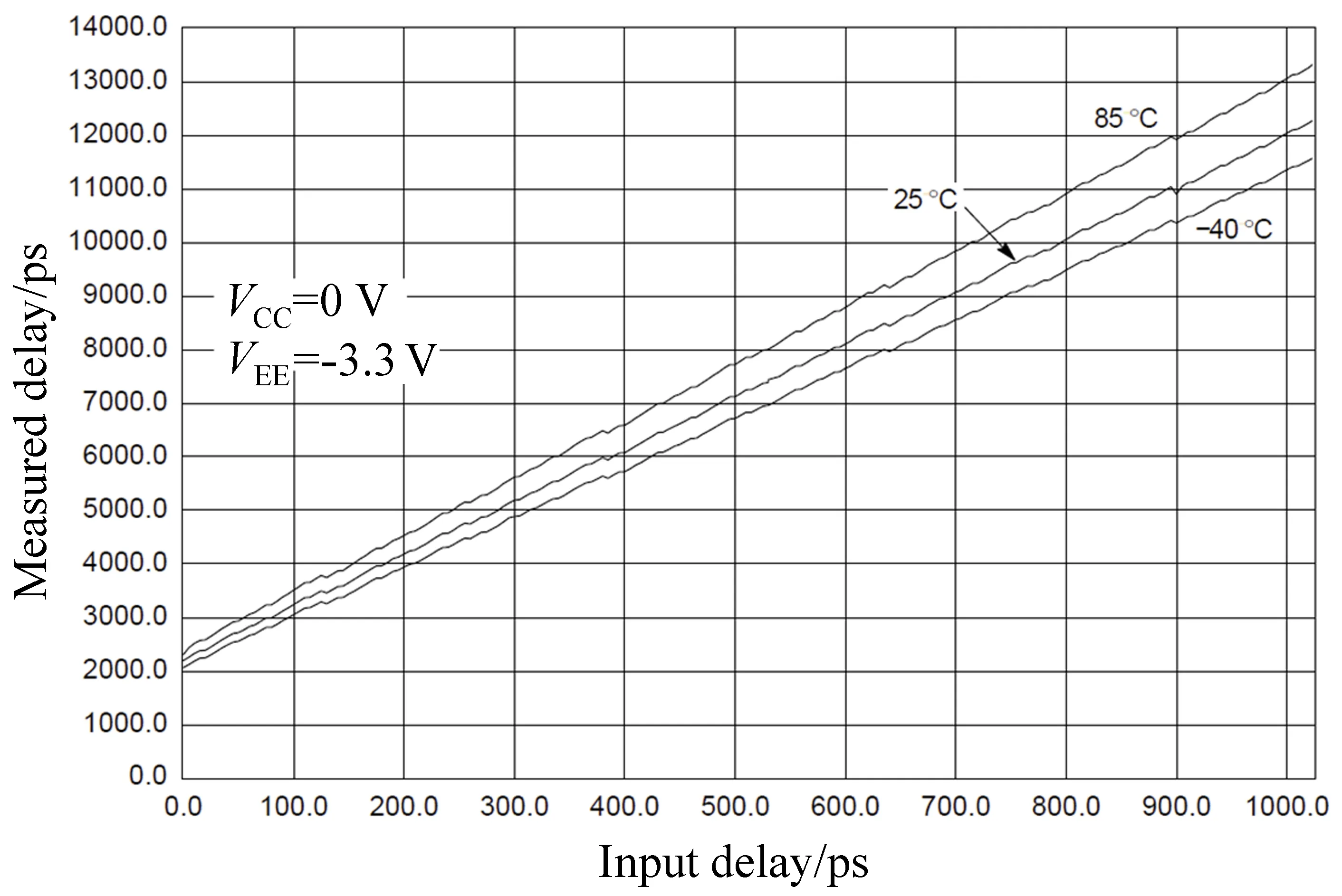

图5 为MC100EP195 实测延时与输入延时,温度对其延时时间的影响最大可以达到1.5 ns,而且随着延时时间的增大,温度对其影响越来越明显。同时整个系统的硬件固有延时等也对温度的变化比较敏感[13,14]。使用TDC-GP22 时间测量模块对输出脉冲信号与外部触发信号的时间差进行测量,将测得时间差数据通过单片机进行实时处理,用以在下次延时处理时对可编程延时芯片的细延时时间进行微调,实现对延时时间的闭环控制,从而提高延时稳定性[15]。

图5 MC100EP195 实测延时与输入延时Fig.5 Measured delay and input delay of MC100EP195

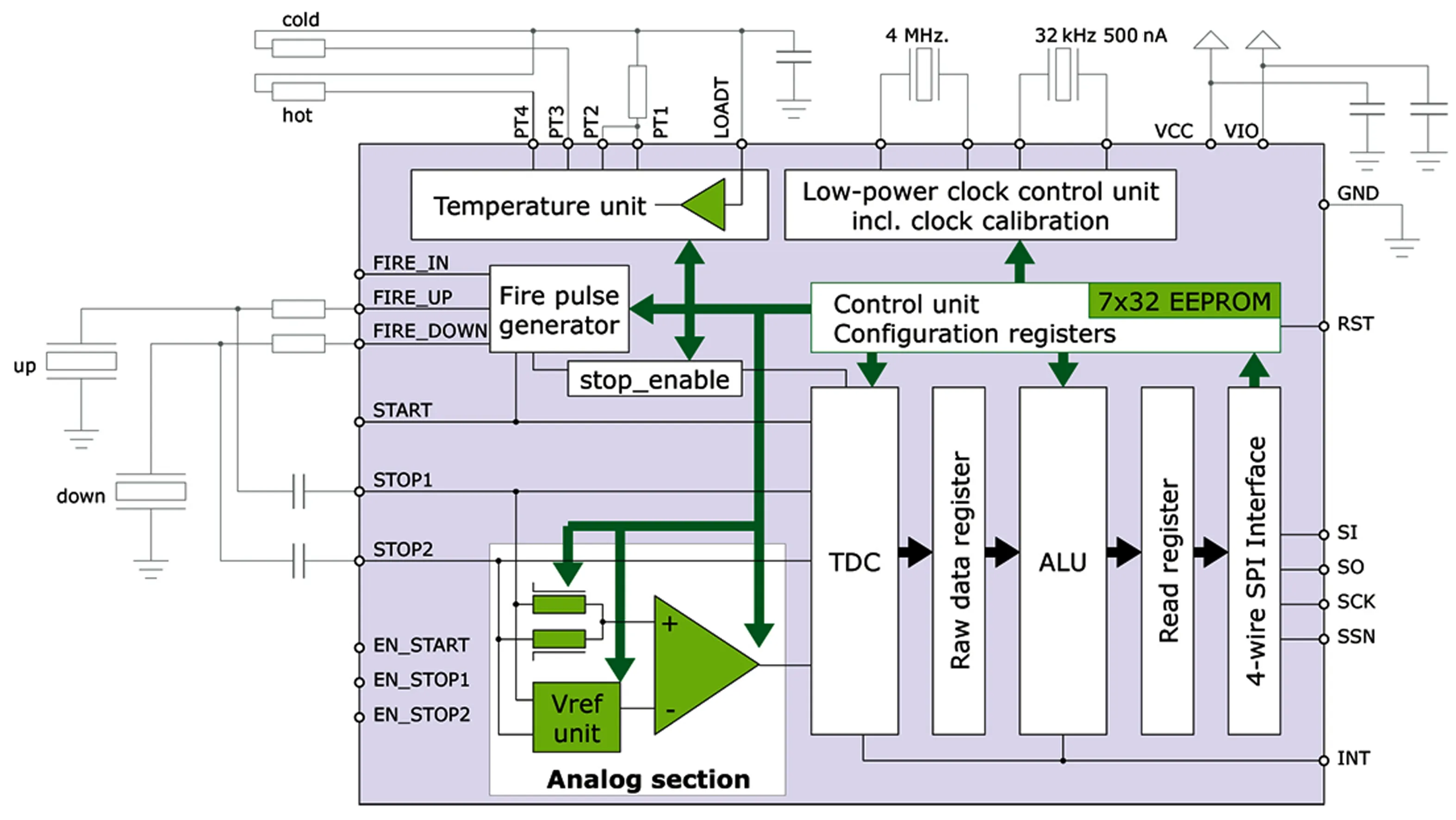

3.1 TDC-GP22 时间测量模块

TDC-GP22 是ACAM 公司生产的双通道时间数字转换器,用于测量两脉冲信号的时间差,捕获方式为上升沿捕获或者下降沿捕获,最多可以同时捕获4 个脉冲,其芯片内部逻辑图与外围电路图如图6 所示。TDC-GP22 芯片有两种测量模式及多种测量方式[16−18]。测量模式一可测量3.5 ns∼2.4µs 的时间范围,可选择2 个STOP 通道相对于1 个STA 通道或1 个STOP 通道相对于1 个STA 通道两种方式;测量模式二可测量500 ns∼4 ms 的时间范围,测量方式为1 个STOP 通道对应1 个STA 通道[19−21]。系统使用测量模式一中2 个STOP 通道相对于1 个STA 通道的方式,输入信号主要为起始触发信号STA、飞秒激光器触发脉冲信号(即系统输入触发脉冲信号)STOP1、准分子激光器触发脉冲信号(即系统输出触发脉冲信号)STOP2。该方式测量范围为3.5 ns∼2.4µs,典型精度为90 ps,测量方式为在捕获STA 信号上升沿后的2.4µs 内进行信号STOP1 与STOP2 上升沿的捕获,分别测量STOP1 与STA 之间的时间差t1、STOP2 与STA 之间的时间差t2,再计算两者之差,输出的则是STOP1 与STOP2 之间的相对时间差。

图6 TDC-GP22 芯片内部逻辑图与外围电路图Fig.6 Internal logic diagram and peripheral circuit diagram of TDC-GP22 chip

3.2 通信协议

TDC-GP22 通过四线SPI 控制,分别为片选(SSN)、时钟(SCK)、数据接收(SI)、数据发送(SO),通过SPI 通信对GP22 进行寄存器配置、数据读取、控制指令等操作。除了SPI 通信接口之外,还包括复位信号RTN 与中断信号INT,TDC-GP22 复位操作可通过单片机控制RTN 信号处于低电平复位,而中断信号在发出测量的指令后,信号处于高电平,当有信号被捕获成功后,信号拉低,通过这种方式单片机可以高效率地进行数据读取。

3.3 时差数据处理

使用STM32 单片机对TDC-GP22 的数据进行实时处理,具体型号为STM32F103CBT6。通过IO 口PB1、PB2、PB3、PB4 与TDC-GP22 模块的SSN、SCK、SI、SO 相连进行SPI 协议通信;通过IO 口PB0、PB5 与TDC-GP22 模块的RST、INT 相连接进行复位和中断控制。

首先单片机发送初始化指令,开始校准TDC 指令,等待中断。TDC 单元的每个通道可以测量4 次,通过TDC-GP22 中写寄存器1 的Bit16-19(HIT1)以及20-23(HIT2)自由定义算数逻辑单元(ALU)选择计算哪两个信号之间的时差。设定STOP1 为HIT2 通道1,STOP2 为HIT1 通道1;发送INIT 指令等待信号捕获;将STOP1 与STA 的时差数据以及STOP2 与STA 的时差数据作为THIT2和THIT1存储起来。测量的分辨率会随着温度和电压的改变而改变,所以TDC-GP22 的ALU 需要内部校正测量结果。TDC 测量一个和两个参考时钟周期,这两个数据作为TCal1和TCal2存储起来,两者相减之后为真实的一个时钟周期[22]。最终输出STOP2 与STOP1 的时差,其计算公式为

单片机上IO 口PA9、PA10 通过通用异步收发传输器(UART)将处理后的时间差信号数据发送给FPGA 进行处理,数据格式为6 位8 Byte,首位数据D1为正负标识,当数据大于0,为0x00,否则为0xFF,其他数据D2、D3、D4、D5、D6为时间差数据。

4 系统性能测试

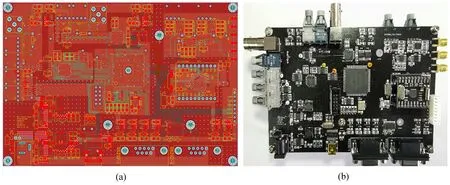

按照以上实现方案,利用AltiumDesinger 软件设计完成的硬件电路版图和焊接调试后的电路主体实物图如图7 所示。

图7 (a)硬件电路版图;(b)电路主体实物图Fig.7 (a)The hardware circuit layout;(b)The circuit main body

使用AFG3101 信号发生器作为外触发信号源,频率设置为100 Hz,脉宽为1µs,上升沿、下降沿均为5 ns,通过光纤接收器HFBR-1527 转换为光信号输入延时同步系统;使用光纤发射器HFBR-2526 将延时同步系统输出的光信号转换为电信号并作为示波器测试信号;使用LeCroy354A 示波器(带宽为500 MHz,采样率为2 G/S)测试系统延时后的输出信号,首先测试系统的粗细延时功能,其次测试输出信号的抖动性能,系统性能测试主要针对上述两方面进行。

4.1 系统粗细延时功能测试

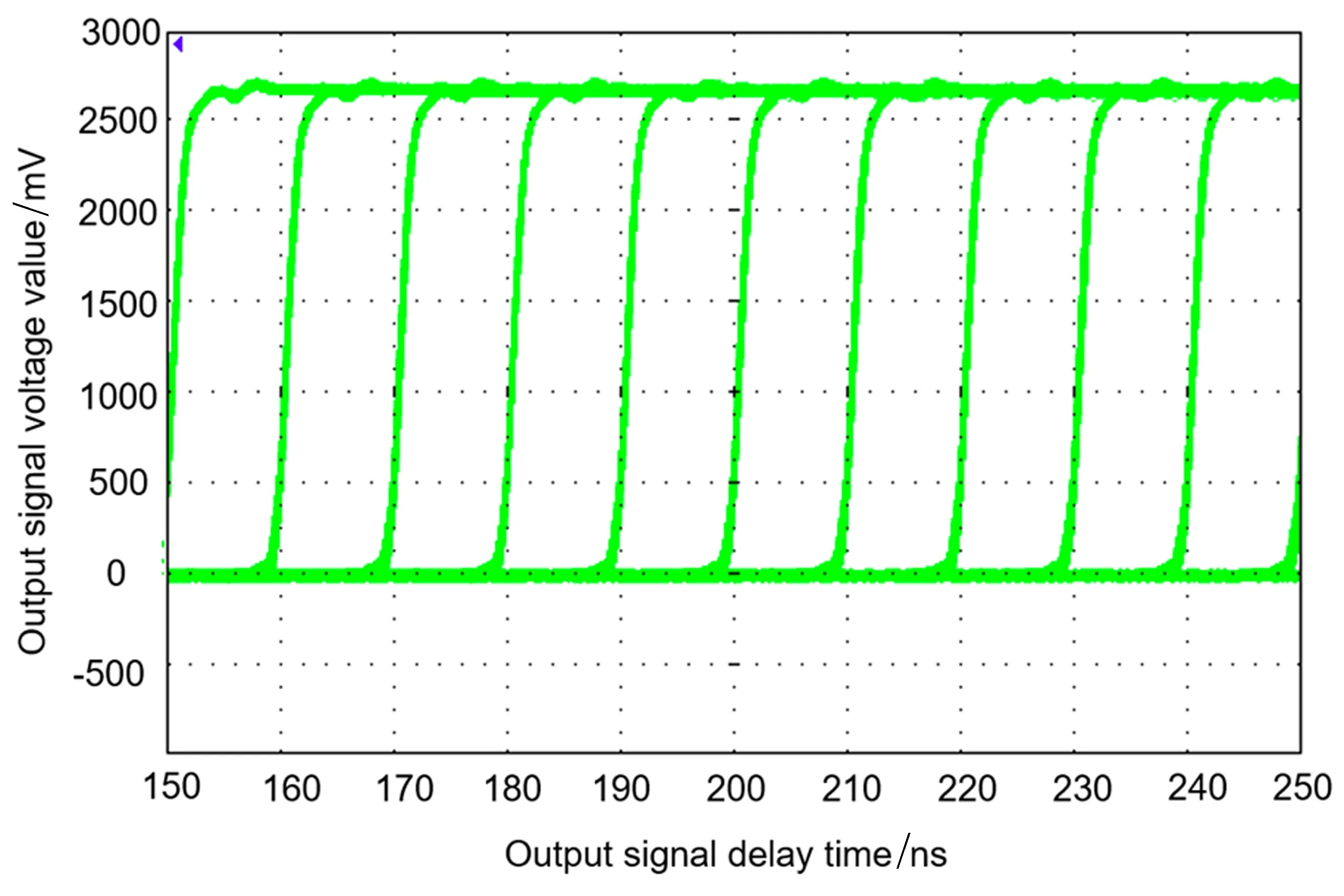

系统10 ns 步进的粗延时功能由FPGA 计数器实现,在延时时间150 ∼250 ns 之间以10 ns 为步进,每个步进输出100 个延时脉冲。图8 为延时输出信号以外触发信号为基准的波形余辉图,系统粗延时功能正常。

图8 10 ns 延时步进波形余辉图Fig.8 Persistence graph of 10 ns delay step waveform

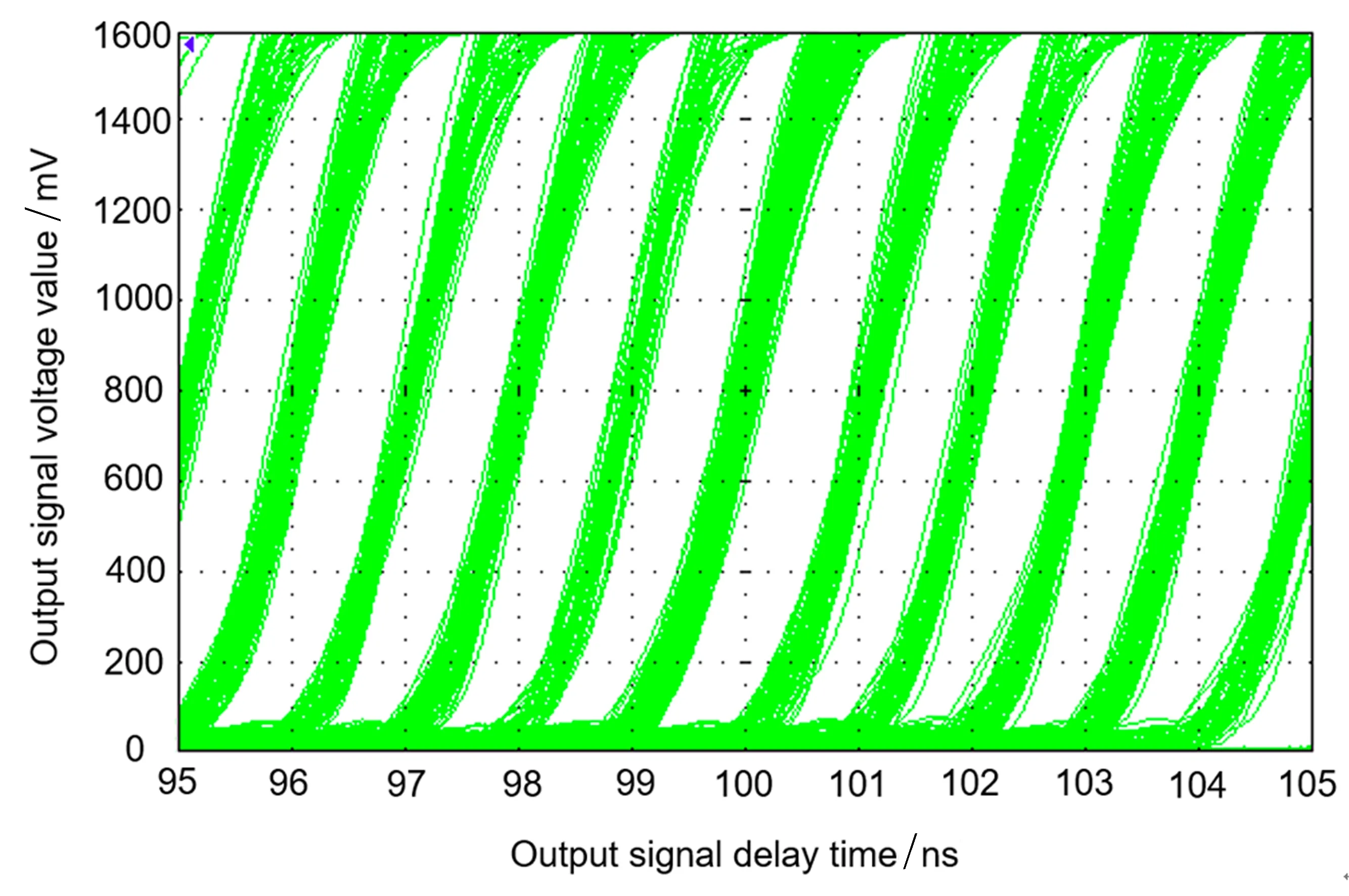

由于示波器带宽限制和输出信号抖动的影响,1 ns 以内延时示波器观测效果并不理想。10 ns 以内细延时均由可编程延时芯片完成,以1 ns 步进进行延时,也可验证细延时功能。在延时时间95∼105 ns 之间,以1 ns 为步进,每个步进输出100 个延时脉冲,输出波形余辉显示如图9 所示,系统细延时功能正常。

图9 1 ns 延时步进波形余辉图Fig.9 Persistence graph of 1 ns delay step waveform

4.2 系统输出信号抖动测试

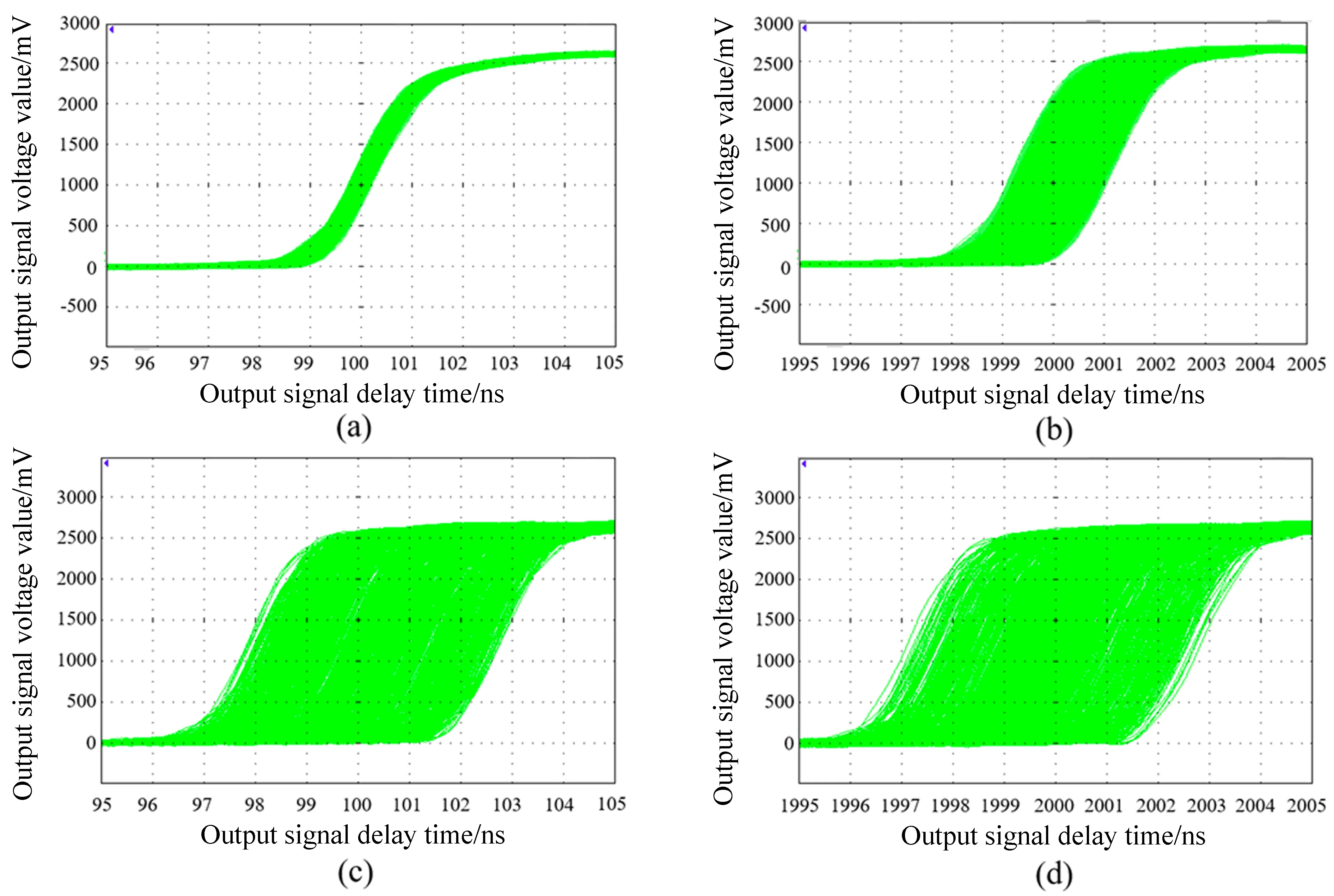

系统输出信号抖动也是延时同步系统的重要技术指标。将系统延时时间设置为不同值,系统持续输出5 min,通过示波器波形余辉图观察输出脉冲信号相较输入脉冲信号的抖动。如图10 所示,图10(a)、(b)分别为闭环控制下的100 ns、2000 ns 延时输出脉冲抖动,图10(c)、(d)分别为非闭环控制下的100 ns、2000 ns 延时输出脉冲抖动。很明显,时间测量模块对延时时间的闭环控制有效地控制了延时后的输出脉冲抖动。具体数据如表1 所示。

表1 不同延时时间设置下实际输出脉冲延时时间与抖动数据Table 1 The actual output pulse delay time and jitter data under different delay time settings

图10 (a)闭环控制下延时100 ns 的输出脉冲抖动;(b)闭环控制下延时2000 ns 的输出脉冲抖动;(c)非闭环控制下延时100 ns 的输出脉冲抖动;(d)非闭环控制下延时2000 ns 的输出脉冲抖动Fig.10 (a)The output pulse jitter with 100 ns delay under closed-loop control;(b)The output pulse jitter with 2000 ns delay under closed-loop control;(c)The output pulse jitter with 100 ns delay under non-closed loop control;(d)The output pulse jitter with 2000 ns delay under non-closed loop control

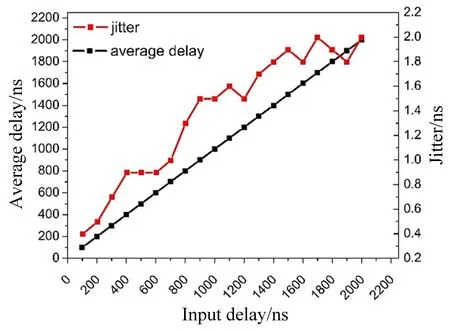

在100 ∼2000 ns,每隔100 ns 测试一次延时输出脉冲信号抖动。输出信号实际平均延时与抖动如图11 所示,输出脉冲触发信号的抖动随着延时时间的增加而逐渐增加,同时实际平均延时与设置延时基本一致。输出抖动增加的主要原因是随着延时时间的增加FPGA 计数器延时的计数值也会增加,计数值的增加导致FPGA 主时钟的抖动叠加到输出抖动上。

图11 不同延时时间设置下输出信号实际平均延时与抖动Fig.11 The actual average delay and jitter of the output signal under different delay time setting

5 结 论

设计了一种准分子激光低抖动延时同步系统, 基于FPGA、可编程延时芯片、单片机以及TDCGP22 时间测量芯片,采用FPGA 数字延时和可编程延时芯片延时相结合的方案,利用时间测量芯片实现对延时时间的闭环控制以提高系统延时的稳定性,利用单片机读取并处理时间测量数据。与现有延时装置相比,本系统能够对外触发脉冲信号进行高精度延时,延时范围为56 ns∼2.2µs,理论延时步进为10 ps,实现了对延时时间的闭环控制,输出脉冲信号抖动在±1 ns 内;同时,利用光信号作为输入输出能够有效屏蔽准分子激光放电时的电磁干扰。该系统满足飞秒激光器与准分子激光器同步工作的需要,为飞秒深紫外准分子激光系统硬件时序控制提供了参考。