L波段快速锁定频率合成器的设计与实现

刘长明,江飞

(同方电子科技有限公司,江西九江, 332000)

0 引言

跳频通信由于其具有抗干扰、抗截获的能力,在当前军事抗干扰通信系统中被广泛应用。跳频通信系统的一项重要参数是频率的跳变速度,它在很大程度上决定了系统抗跟踪式干扰的能力。因此,快速锁定频率合成器的设计就成为跳频通信的关键技术之一。本文采用自适应精确预置技术实现了一个L波段快速锁定频率合成器的工程设计。

1 自适应精确预置技术原理

频率合成器锁相环路在开始工作时,参考频率fR与压控振荡频率fV可能不相等,处于失锁状态。因而需要靠锁相环鉴相输出的相位误差电压控制系统进行调整,最后锁定在状态fR=fV,这一过程称为锁相环路的捕获过程。环路捕获过程包括频率捕获过程和相位捕获过程。

相位捕获与频率捕获只是用于区别环路运动状态的两种不同过程,表征环路捕获过程中的不同阶段,实际上并不能进行严格划分。当环路中的相差做较大范围变动时,环路处于频率捕获阶段;当环路中的相差不再超过2π而进入锁定时的捕获过程被称为相位捕获。

环路依靠自身的控制作用而捕获的方式称为自捕获,借助于辅助电路实现捕获的方式称为辅助捕获。自捕获的缺点:捕获速度慢、捕获范围小、可靠性差,通过改变环路参数的方法改善捕获性能时会严重影响环路的跟踪性能,实现时一般采用辅助捕获方法改善环路的捕获性能。

在实际的跳频系统应用中,既要提高环路自身的频率捕获性能,同时又保证锁相环路的相噪性能,单靠锁相环本身来说是很难实现的,必须采用一些频率辅助捕获技术。自适应精确预置技术就是一种提高环路捕获性能的方法,它是在粗调预置技术基础上进行完善的,其基本原理如下:

粗调预置技术的采用基本上避免了锁相环路的失锁和假锁现象,粗调预置技术的合理采用,可以使得锁相环路迅速进入快捕带,从而大大加大环路的锁定速度,减小压控振荡器的增益,减小压控振荡器输出相位的抖动噪声。但是在长期工作的跳频系统中,要求锁相环路始终能够满足一定的锁定速度要求,而粗调预置技术在某一频点始终都用同样的值去预置压控振荡器。由此可见,粗调预置技术缺乏灵活性,不能保证锁相环路始终都能得到比较准确地预置。

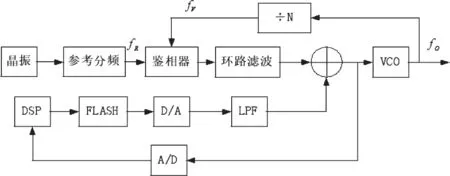

因此,对此粗调预置技术进行了改进。在粗调预置技术的基础上提出了自适应精确预置技术。在跳频系统的实际工作中,由于环境温度等因素的变化,VCO的压控特性会有所变化,原定的预置值可能会与实际所需值出现误差。为了及时修改频率码与预置电压的对应关系,可以用FLASH作为存储器(如图1所示)。当环路在某一频率锁定时,系统把鉴相器输出的电压值采样进入数字信号处理器(DSP),用该电压修正原来的预置值,修改后的值作为下一次跳入该频率时的预置值。由于环境变化速度相对于跳频周期慢得多,更新的预置值能准确、实时地跟踪任何环境条件的变化。这样,通过不断的精确预置,频率跳变时,VCO的输出频率与要实现的频率只有很小的相位偏差,锁相环基本上工作在相位跟踪状态,大大减小了频率转换时间,从而很好地满足快速跳频的要求。

图1 采用自适应精确预置技术的频率合成器原理框图

2 自适应精确预置技术的工程实现

■2.1 快速锁定频率合成器方案设计

以一个L波段快速锁定频率合成器为例,要求输出频率为1200~1600MHz,换频时间不大于100μs。

频率合成方案充分考虑数字直接频率合成(DDS)技术和锁相环频率合成技术优缺点互为补充的特点,采用DDS+PLL架构。由DDS提供快速跳频的小步进间隔,锁相环(PLL)工作在大步进间隔,这样可以提高鉴相频率,增大环路带宽,并抑制杂散分量。DDS相当于一个小数分频器。接收VCO输出的频率,通过改变频率控制字K,使其输出固定的频率。此方案的设计中体现出以下显著优点:

利用了DDS频率转换速度快,频率分辨率高的优点,并克服了其输出频率低和输出信号频率范围小的缺点。

利用了锁相环频率合成技术良好的跟踪特性和噪声特性。

本系统方案在相当程度上解决了锁相环中提高鉴相频率和降低频率间隔的矛盾。既实现了频率的快速跳变和精细步进,又实现了高的频率输出。

系统结构简单,容易实现,实现成本也较低。

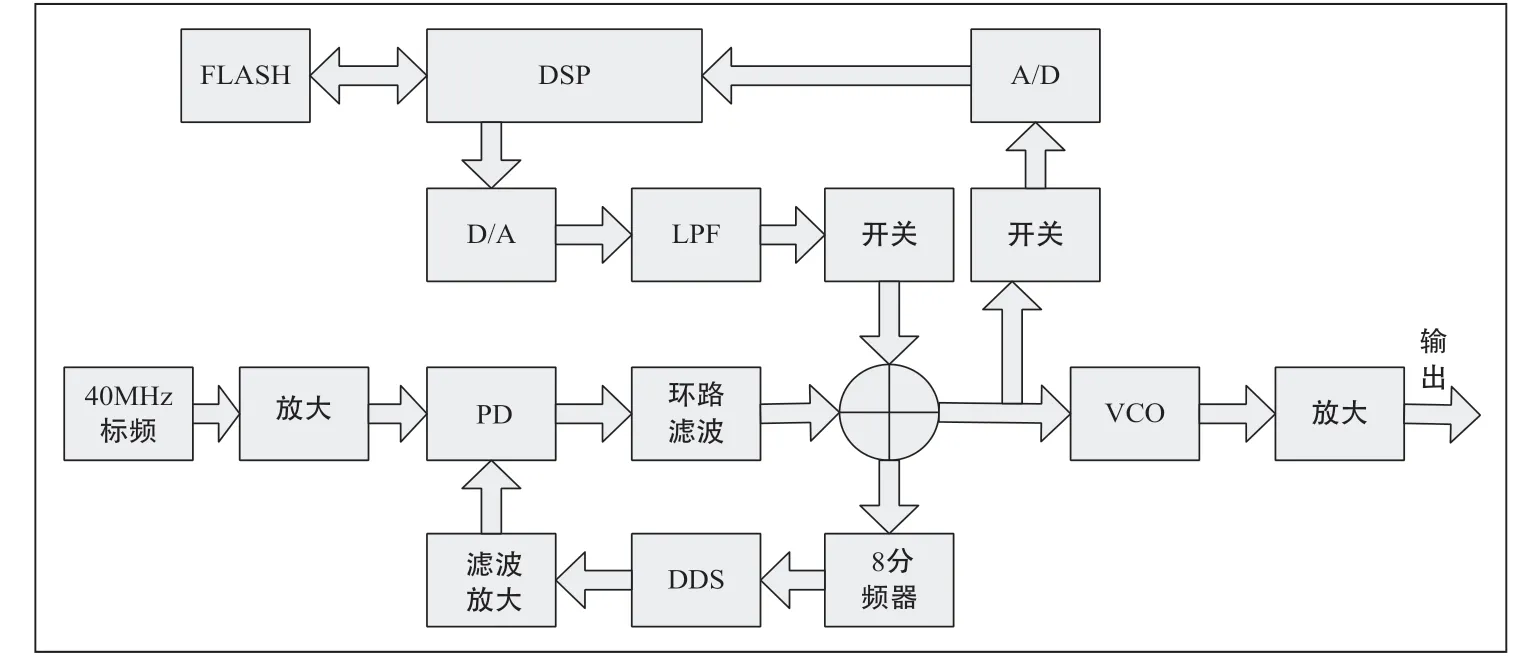

为了满足电台高速跳频的要求,在方案中同步采用了自适应精确预置技术,在环路辅助捕获电路上设计了对VCO的压控电压进行采样的A/D以及预置压控电压所需的D/A,其原理框图如图2所示。

图2 快锁锁定合成器原理框图

采用自适应精确预置技术的频率合成器快速锁定设计思路如下:

首先,开机先进行全频段扫描,把全频段锁相环锁定后的VCO调谐电压采样并存储起来,这样在下次换频时,可直接预置其相应压控电压,可省去锁相环频率捕获时间和A/D采样时间而让锁相环直接工作,完全避免了锁相环捕获时间过长的问题。这样,频率合成器实际需要的频率转换时间就只有D/A建立时间,锁相环捕获时间和送数时间。一般来说,前2种时间都很短,都在微秒量级,送数的时间相对要长一些一般在几十微秒。因此从原理上讲,可以实现锁相环的捷变频。

其次,为了保证频率合成器正式工作时每次频率转换,锁相环均能一次锁定。除了在开机及某些特定的时间利用锁相环工作对预置电压数据进行修正外,在每次锁相环锁定后仍同步对VCO调谐电压采样,并将此次采样得到的数据刷新原来的预置电压数据。这样,在跳频过程中VCO预置电压得到了实时修正,从而使辅助频率捕获电路自动跟踪了VCO特性的变化,对VCO的一致性及外界环境的要求降低。

■2.2 电路仿真

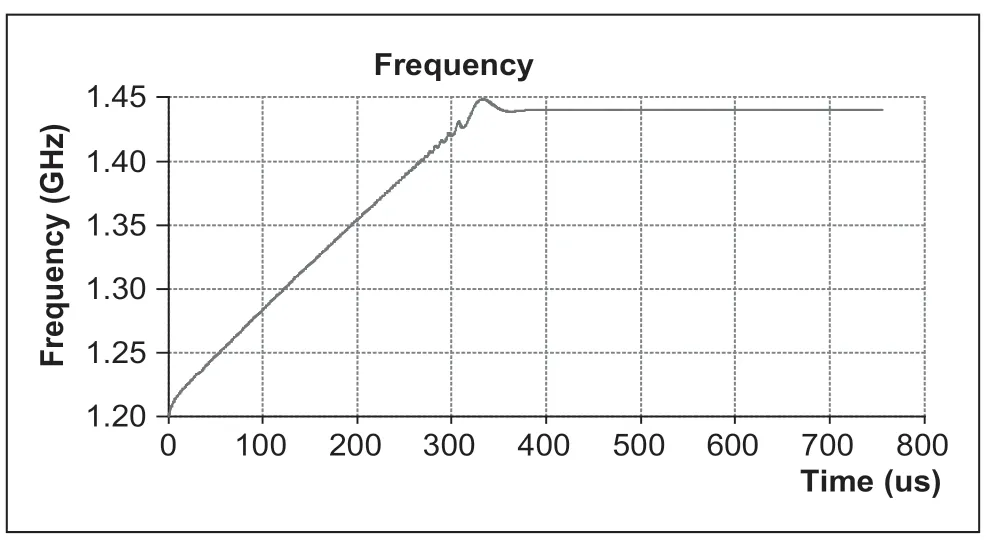

首先对锁相环路进行仿真以优化频率合成器的输出相噪及杂散抑制,同时可以对环路自身锁定时间有一个大概的了解,并可与加了辅助捕获电路以后的环路锁定时间进行对比。笔者用AD公司的ADIsimPLL进行了仿真,仿真参数设定鉴相频率8MHz,环路带宽20kHz,仿真结果见图3。

图3 环路特性仿真图

由图3可见如果不采用预置技术单靠环路自身锁定,由于要保证低相噪,所以要求鉴相频率不能太高,环路带宽比较窄,从仿真结果来看单环锁定时间在350μs以上,并且考虑到实际工作时各种器件及送数等相关方面的延时,实际锁定时间只会比理论估算时间要长。

■2.3 软件程序流程

软件程序流程需要分为对压控电压的采集过程和采集处理后对压控电压进行预置的正常工作过程。

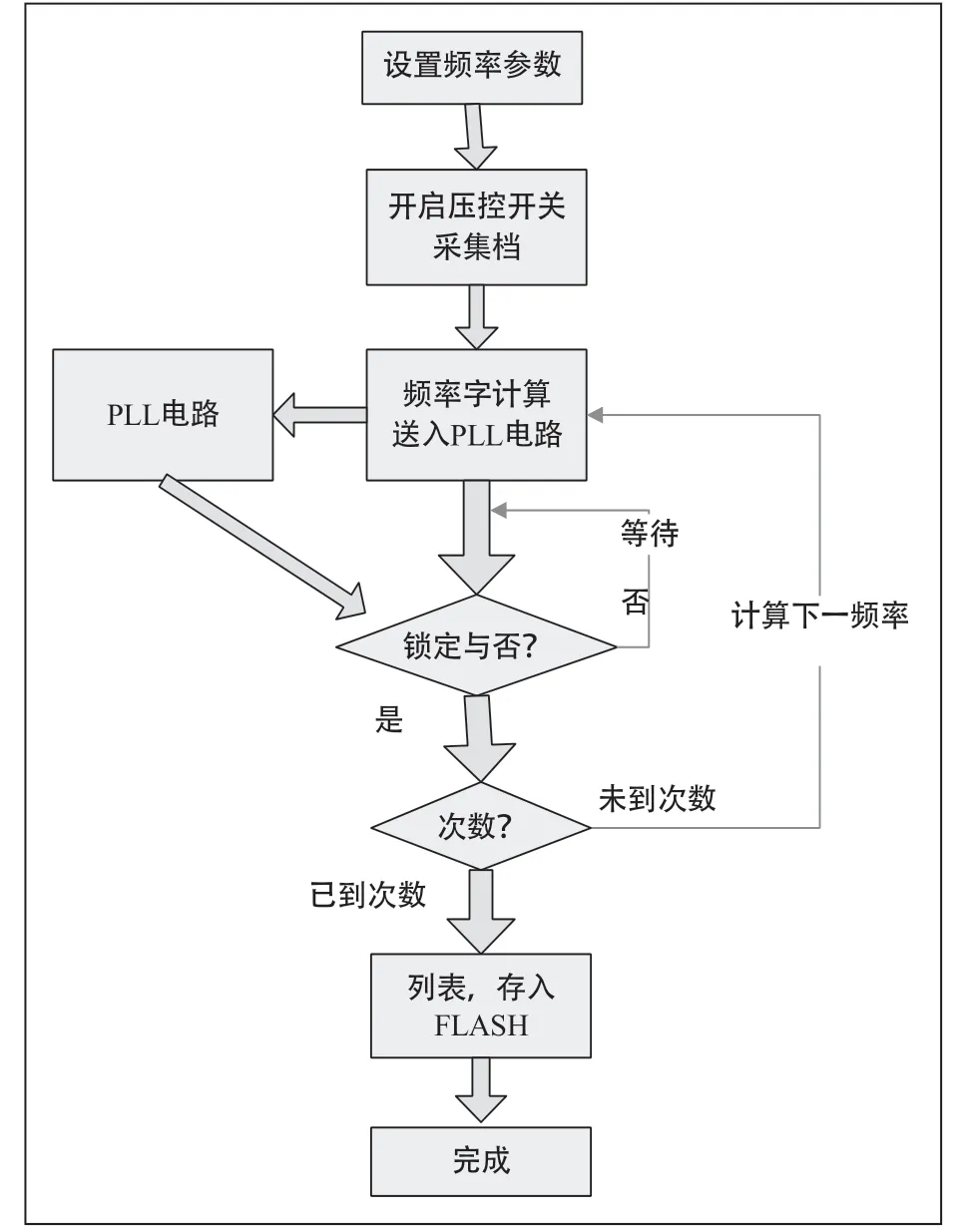

2.3.1 采集数据流程

设置起始频率1200MHz,频率步径为0.5MHz(即从1200MHz开始,每隔0.5MHz频率采集一次),次数为801次。然后将开关切换到采集状态,通过DSP进行预定频率点的频率控制字计算,将计算结果通过串口按时序将频率控制字送入PLL电路的相应芯片,等待PLL电路的锁定指示,这样就完成了一次频率送数工作。当DSP芯片收到锁定指示后便开始采集压控电压,该电压值通过A/D采集并输送到DSP中,DSP将这个数值多次累计后求其平均值,并将其平均值和相对应的频率点放入缓存,待到全部频率点的压控电压数值均已经采集完毕,将所有数值做成一个频率/压控电压的表格写入FLASH芯片中保存下来,这样则采集工作结束。图4为采集阶段的流程图。

图4 采集流程图

2.3.2 正常工作流程

设置需要的频率点,通过DSP对该频率点的频率控制字进行计算,并将计算出的频率控制字送入PLL电路的相对应的芯片内,送数的同时把开关切换到预置状态,从FLASH中将该频率对应的压控电压数值读出并写入DA芯片,其输出的模拟电压就是环路的预置电压,帮助PLL电路快速锁定频率。

需要注意的是,开关不能一直处于预置状态,不然由DA送出的电压一直存在就会干扰锁存芯片的正常工作,所以开关预置状态只能在送数时开启,在送数结束后就应该立刻将其断开以保证锁相环能正常锁定频率。

为了方便测量,可以在一个频率正常锁定后(取得锁定指示后)延迟一小段时间又开始输入另一个频率点。继续以上操作,再次锁定后再切回原先的频率,使得频率合成器在两个一定跨度的频率点之间来回循环切换,以方便使用仪器来测量这两个频率切换所需要的时间。

3 测试结果及结论

■3.1 测试结果

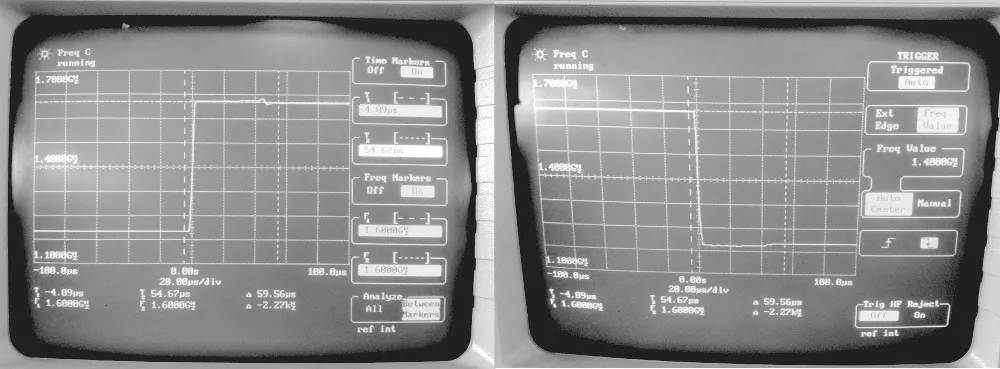

经过反复对电路进行指标优化以后,对换频时间测量后发现,在1200M和1600M两频率已可缩短至60μs以内(频率跨度400M,压控电压范围2~13V,这个时间里面包括了预置时间4μs,送数时间30μs,环路相位捕获时间20μs),测试结果如图5所示。

图5 加自适应精确预置技术的测试结果

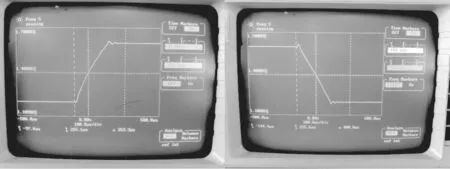

对PLL去除自适应精确预置技术相关电路,重新测试换频时间,两个频点间切换时间在400μs以上,测试结果如图6所示。

图6 不加自适应精确预置技术的测试结果

从上述测试结果来看,采用自适应精确预置技术的频率合成方案能达到非常好得快锁效果。

■3.2 结论

本文介绍了自适应精确预置技术的基本原理以及工程化实施方案,通过对实际样品的测试试验,证明了采用该快速方案的可行性,为以后高速跳频频率合成器的设计提供了一种新的参考思路。