分析集成电路电磁兼容测试PCB设计要点及应用

岳锟,李文杰

(无锡中微爱芯电子有限公司,江苏无锡, 214000)

0 引言

近年来集成电路的研制逐渐向着体积减小、响应速度加快以及工作频率提高的方向发展,虽然技术水平的提升,使得芯片电磁发射不断增加,但同时电路间受到干扰和影响的风险也在不断增加,为保障芯片可靠性,对于电磁兼容测试的精准度要求也在不断提高。而PCB设计作为集成电路电磁兼容测试当中的重要内容,因此,加强对其设计要点及应用的研究是十分有必要的。

1 现代集成电路发展对于电磁兼容的影响

集成电路对于电磁兼容而言,不仅是干扰源,同时也是被干扰的对象,随着近年来集成电路的不断发展,导致器件尺寸逐渐变小,集成电路复杂程度呈现出持续增长态势,封装内的集成度以及数据交换速率都在不断提升,更高的频率、更快的响应速度以及耕地的电源电压都极大地威胁着集成电路的可靠性,因此提高电磁兼容性能就成为当前研究工作的重点内容,尤其是在测试方面的研究,正在逐渐深入。现代集成电路发展对于电磁兼容的影响主要体现在电磁发射以及电磁敏感度两个方面。

■1.1 电磁发射方面

集成电路的电磁传导发射主要受到动态电流消耗以及集成电路内部互连和封装引脚提供的滤波两个参数的影响。其中前者与集成电路内部行为和I/O开关性能有着密切的关系,而后者则主要与电源和地线相关。除此之外,辐射发射也会受到互连线长度,以及外部去耦电容器之间距离的影响,互连长度的缩短影响着信号完整性的衰减情况,以及辐射发射问题,与此同时,互连长度的减小也能够有效降低近场或者基板耦合的风险。因此,为进一步保障集成电路设计的合理性,就需要提前对芯片的电磁兼容性能进行测试分析,以此保障芯片的可靠性。

■1.2 电磁敏感度方面

影响集成电路电磁干扰敏感度的参数主要包括以下三个:即互连和封装引脚对传导干扰的滤波、静电防护结构所带来的钳位干扰,以及芯片上电路模块固有的敏感度。电磁敏感度主要受芯片内部设计影响,小型化趋势,以及先进的封装使得混合信号的功能需要集中在小体积当中,而且随着研发的深入,集成电路的体积不断缩小,这就使得射频、模拟、数字以及电源等多个系统需要封装在同一衬底当中,极大地增加了系统内部的干扰风险[1]。

2 集成电路电磁兼容测试PCB设计要点

■2.1 PCB测试板要求

当前电磁兼容测试方法相对较多,而PCB设计作为电磁兼容测试过程中的重要环节,不同测试方法对于PCB设计的要求也是不同,因此,在进行PCB设计之前,就需要结合相应测试项目、方法进行全面梳理,并尽可能确保PCB的设计能够满足多种测试要求。例如,当前集成电路电磁兼容测试主要包括TEM小室法、带状线法、1Ω直接耦合法以及150Ω直接耦合法四种,其在PCB设计当中的要求各有不同:与TEM法相比,带状线法的PCB设计要求更加严格;在进行1Ω直接耦合法的PCB设计时,该方法需要进行RF电流的测量,因此要求在电路板的地以及IC的地之间进行断点设计;而150Ω耦合法则要求暴露受试IC引脚。对此,在实际进行PCB设计的过程中,就可以按照带状线法的要求,确定DUT的位置,并在DUT的地和PCB板间的地之间串联0Ω电阻,以此满足断点设计要求,同时还需要将受试IC引脚暴露出来,以此提升测试的便利性,共同满足四种不同测试方法的设计要求。在实际进行测试的过程中,需要将PCB放置在相应测试装置上,并根据集成电路自身的复杂程度,合理选用双层、四层、六层或者多层电路板进行测试,通常情况下,为保障地平面完整,至少设计为四层,在进行PCB布局设计的过程中,不仅要遵循常规布线布局原则,同时还需要加强对于屏蔽、电源滤波以及I/O负载匹配方面的设计研究。

■2.2 屏蔽设计要点

当采用TEM小室法以及带状法进行电磁兼容测试时,要求PCB安装在小室外壳开口位置,并确保焊接IC的一面朝里,以此确保其能够与小室外壳接地相连,以此达到将IC与外部有效隔离的效果,降低外部干扰对于测试结果的影响。在实际进行屏蔽设计的过程中,需要注意以下要点内容。

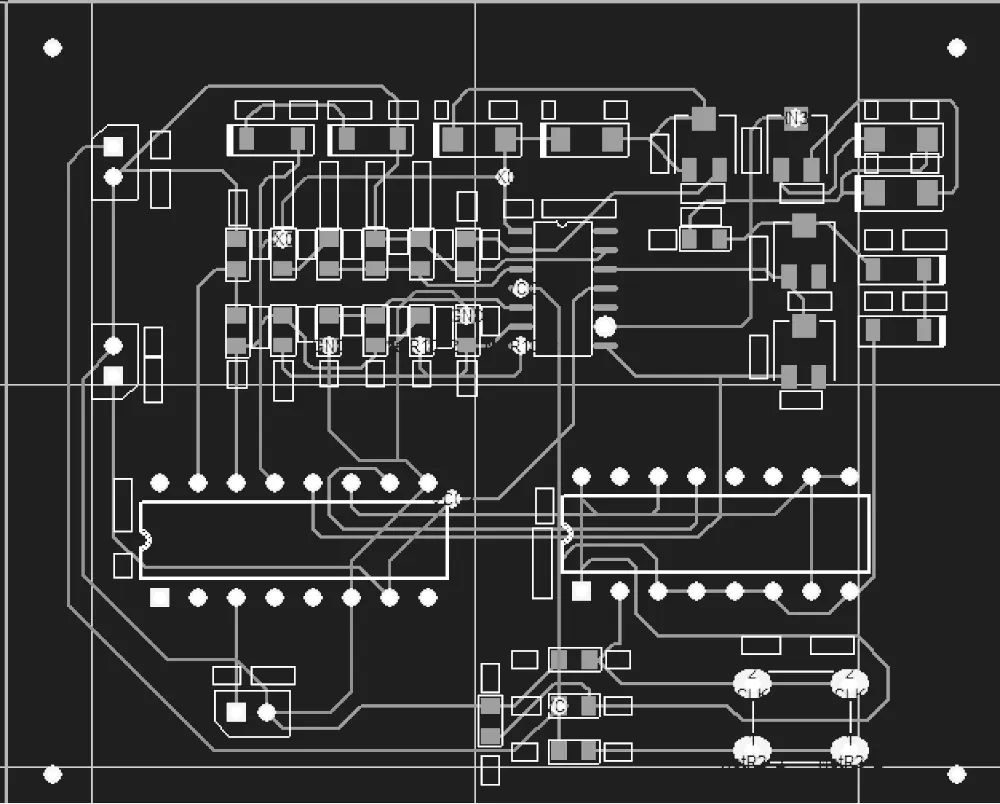

第一,地平面完整性设计。根据相关标准要求,层1为地层,在实际进行焊接的过程中,由于引脚焊盘的影响,导致芯片底部与外部地平面无法连通,导致地平面不完整。对此,可结合实际需求通过不同设计方式进行解决:其一,完成待IC放置之后,需要在芯片周围设置接地过孔带,并在PCB其他层面芯片引脚下方位置绘制回型地平面带,并将其外侧与接地过孔带相连,然后在地平面带内侧再设置第二个接地过孔带,在层1上将第二个接地过孔带进行连接铺地处理,并将层1下方进行接地处理,以此形成完整地平面。其二,当IC下方器件的布置密度较高时,仅通过设置接地过孔带难以满足实际过孔间距要求,对此,可借助内层地平面,将其与第一个接地过孔带相连,进而形成完整地平面。其三,若待测IC对于底部散热以及接地有着较高要求时,可将第二个接地过孔带设计成盲孔形式,进行接地处理,然后在层1下方铺铜,以此达到散热目的。相应设计方案如图1所示。

图1 地平面完整设计方案

第二,过孔间距设计。在PCB设计过程中过孔间距直接影响着测试结果,若间距过大则会导致电磁大幅泄漏,极大地降低了整体设计的屏蔽性能,因此科学合理地确定过孔间距也是十分重要的。在实际进行设计时,由于各方面因素影响,无法保障过孔间距始终保持最小,或者规则放置,需要结合外围电路等实际情况进行适当调整。根据相关电磁兼容技术标准要求,缝隙程度应小于其中λ表示波长,单位为m,λ计算公式为:

式中,c表示光速,为3×108m/s;f表示频率,单位为Hz。

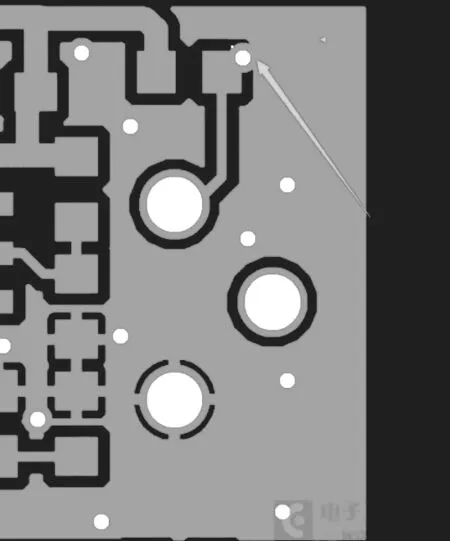

图2 过孔带设计

第三,边缘过孔带设计。在进行边缘过孔带设计的过程中,为确保PCB板接触良好,需要在层1四周边缘进行开窗设计,以此促使地平面铜皮暴露,实际开窗尺寸,需要根据工装边缘进行合理确定,值得注意的是,TEM小室法要求其尺寸应至少为5mm。同时,为避免开窗导致屏蔽效果不良,在设计时,可适当增加过孔带以此保障测量结果的准确性。除此之外,由于150Ω直接耦合法与其他测试法PCB板的放置方向不同,因此,为保障工装接地效果,在应用150Ω直接耦合法时,还需要在层4进行对地开窗设计[2]。

图3 边缘接地过孔带

■2.3 电源滤波设计

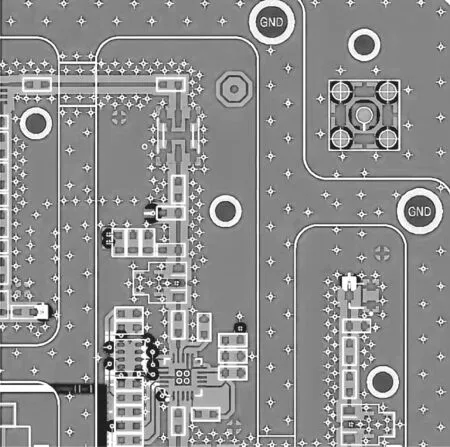

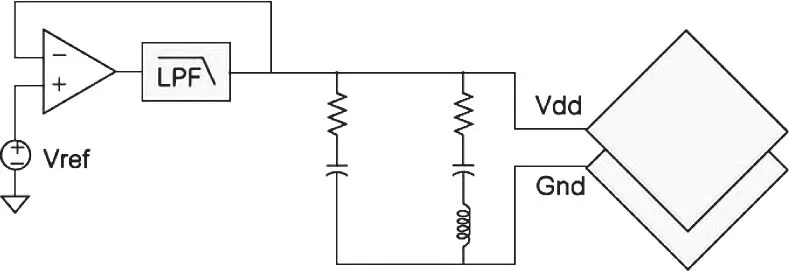

PCB板级电源以及IC电源的去耦对于测试结果的准确性以及可重复性有着较大的影响,因此在进行PCB设计的过程中,应加强对于这两部分电源设计的重视。在PCB板电源设计方面,影响测试结果的主要因素在于由于电源去耦设计问题,使得电源阻抗产生不良影响,对此,在实际进行设计的过程中,可着重从干扰源和滤波两个方面入手,因此可选择线性电源进行供电,以此减少电源纹波影响,同时还可以在PCB电源输入口增设去耦电容器,如图4所示,以此达到滤波目的。在IC电源设计方面,其去耦电容需要以电源引脚频率特点进行合理设计,并将去耦电容设置在IC下方,以此缩短阻抗路径,同时还需要按照先到电容焊盘,再连接IC引脚的顺序进行布线。

图4 去耦电容接入示例

值得注意的是,在进行去耦电容选型的过程中,要综合考虑电容容值以及电容自振谐频率,避免所选择的电容自振谐频率过低,使得在高频时电容阻抗最值增加,难以达到高频噪声滤波效果,进而导致测试结果不准确[3]。

■2.4 I/O负载匹配

在进行I/O负载匹配的过程中,应严格按照相应标准规范以及相应工况设计图进行负载匹配。除此之外,还需要注意以下两点:第一,严禁未使用的引脚为悬空状态,必须要确保负载匹配符合标准。第二,在进行PCB设计的过程中,可根据实际情况,借助程序实现对于引脚的上拉或者下拉调整,以此降低地层PCB器件的密度,进一步保障地平面的完整性。

3 集成电路电磁兼容测试PCB原理图设计要点及应用

为保障测试结果的准确性以及可靠性,在实际进行PCB设计的过程中,需要根据测试目的,以及待测器件实际情况合理确定相应测试方式。以某国产CPU芯片辐射发射以及辐射敏感度测试为例,设计思路包括以下三个步骤。

第一,结合实际要求针对PCB板测试功能展开设计,对此在设计过程中,需要将CPU的一组引脚引出,以此用于与辅助设备之间的通信,促使CPU处于运行状态。此外,根据敏感度测试功能,需要对芯片运行情况进行实时监测,对此可将芯片引脚与LED灯相连,以此观测芯片运行状态。最后,为避免辅助电路运行对于测试数据的影响,相应附加器件应采用贴片的方式进行封装。

第二,根据上述PCB设计要点以及相关规范要求,需要进行引脚负载配置。由于案例芯片的引脚为复用引脚,因此为保障地平面的完整性,可通过相应软件实现对于I/O引脚的设置,并内置上拉电阻。在进行PCB设计的过程中,对于输入引脚而言,可直接进行接地处理,若无法进行接地,则需要借助10kΩ的电阻器再与电源相连;对于输出引脚而言,则需要借助电容器再进行接地。

第三,去耦电容设计,此环节是PCB设计过程中的重要步骤,根据案例芯片实际情况,采用3.3V外部电源进行供电,并通过在PCB电源输入端增设去耦电容,对此,可事先在PCB板中预留去耦电容位置,其电容值可根据后续测试过程实际情况进行确定。对于IC去耦电容设计而言,其电容值需要根据芯片时钟频率进行选择,在必要情况,可采用两个甚至多个去耦电容[4]。

4 集成电路电磁兼容测试PCB结构设计要点及应用

■4.1 整体结构

集成电路电磁兼容测试PCB结构设计过程中的难点主要表现为电磁兼容PCB为单面板,因此等效面积受到的限制较大,若实际需求下所使用的附加器件较多,PCB板设计难度就会相对较高。对此,在实际进行结构设计的过程中,若附加器件较多、密度较大,可通过将附加器件分散放置在不同小板上,然后再将其与主板相连,以此降低PCB板设计密度。在实际应用这种方式进行PCB设计的过程中,为避免影响到地平面的完整性,或者造成电磁泄漏问题,应选用贴片方式进行封装处理。

此外,在进行集成电路兼容测试的过程中,还会存在被测IC不同,但是外围电路相同的情况,对此在常规PCB设计的过程中,为适应不同IC需求,通常会采用夹具将IC连接到主板上的方式,但是集成电路当中,这种方式对于测试结果将会产生较大的影响。在以某国产芯片为例,使用TEM小室法进行测试的过程中,发现使用夹具进行测试后,其得到的检测数据结果偏高,尤其在高频情况下,这种问题更为明显,严重影响了测试结果的准确性。经过分析发现,造成此情况的主要因素为使用夹具之后,隔板与待测IC之间的距离变小,在两个芯片偶极矩相同的情况之下,TEM小室输出的电压就会有所增加,进而对测试结果产生影响。因此,在实际进行结构设计的过程中,应将晶振直接焊接在PCB测试板当中。

■4.2 布局设计

基于集成电路电磁兼容测试功能需求,PCB结构布局设计与普通PCB板设计存在明显的差异,主要表现在以下三个方面:第一,待测IC需要放置在层1当中,并且为避免内部影响,应确保待测IC单独放置;第二,为达到电源滤波及I/O负载匹配效果,去耦电容需要设置在过孔带内部,并确保其位于IC下方,此外底层器件也应尽量放置在过孔带1内,若整个系统结构较为复杂时,可在过孔带1外侧布置相应器件,值得注意的是,应避免附加器件布置超过PCB板的边缘,并与边缘过孔带之间保持适当距离;第三,为保障PCB板后续固定工装的稳定性,即便器件数量较多,仍不应在PCB板四个角的位置放置器件。

■4.3 布线要求

在进行布线设计的过程中,不仅要符合常规PCB板布线设计原则,同时还需要,满足以下要求:其一,应避免在正面进行布线,在必要时若需要进行正面布线,应尽量确保线程较短,若正面布线过长,甚至存在回路等情况,将会对地平面完整性产生一定影响,进而导致电磁兼容测试结果可靠性下降。其二,严格按照相应检测方法要求,设置过孔带,避免过孔带位置随意、过孔间距不符合要求等,对PCB板设计质量产生不良影响,无法达到电磁兼容测试要求[5]。

5 结束语

综上所述,PCB设计作为集成电路电磁兼容测试过程中的重要步骤,其对于检测结果的可靠性以及精准性有着直接影响,本文结合集成电路电磁兼容测试内容以及相应测试方法,从屏蔽、电源滤波等方面详细探讨了PCB设计过程中的要点内容,并在具体案例当中,从原理图以及结构布局两个方面针对PCB设计要点的应用展开说明,对于IC研发以及电磁兼容检测工作有着重要的参考意义。相信随着对集成电路电磁兼容测试PCB设计的深入研究和实践探索,集成电路电磁兼容测试水平将会得到进一步提升。