基于GND 采样技术的逐次逼近型模数转换器设计

叶茂 ,楚银英 ,赵毅强 †

(1.天津大学 微电子学院,天津 300072;2.天津大学 天津市成像与感知微电子技术重点实验室,天津 300072)

随着仿生机器人和可穿戴电子设备的发展,柔性压力传感器得到了广泛的应用.柔性压力传感器从测量原理上可以分为压阻式、电容式和压电式等不同类型.柔性压阻式压力传感器利用压阻效应将施加在应变片上的压力变化转换为电阻的变化,并通过电桥电路产生与压力相关的输出电压.与其他类型的柔性压力传感器相比,柔性压阻式压力传感器结构简单、灵敏度高、制备流程少、测量电路简单、能耗低[1],因此成为电子皮肤[2]、健康监测[3]等领域的最佳选择.

通常而言,可穿戴电子设备所检测的信号频率较低[4-5],对于压力传感器的需求主要为高灵敏度和低功耗.而ADC 作为柔性压力传感器阵列读出电路的核心模块之一,是连接传感器阵列和后端数字处理电路的重要桥梁,其性能制约着整个传感器系统的功能和精度.所以,应用于电子皮肤、健康监测领域的柔性压阻式压力传感器阵列迫切需要高性能低功耗的ADC.

与其他ADC 相比,SAR ADC 具有结构简单、功耗低等优点,十分契合电子皮肤或健康监测的应用需求.因此,本文设计了一款低功耗SAR ADC 来实现柔性压阻式压力传感器传感信号的数字化,并且通过流片测试对该设计进行了性能测试和可行性验证.

1 SAR ADC整体架构

图1 为本文所设计的基于GND 采样[6]的SAR ADC 整体架构图,ADC 主要由采样保持电路、比较器、分段电容阵列以及SAR 逻辑控制单元组成.其中,分段电容阵列由一个6 位主DAC 和6 位子DAC组成,两部分由桥接电容Cb连接在一起.与传统架构相比,分段电容阵列整体只需130 个单位电容(单端)即可实现12 位DAC 的功能,大大降低了DAC 所需单位电容的数目,从而降低了电容阵列的切换功耗和版图面积[7].DAC 的前5bit MSB 采用温度计编码,并利用动态元件匹配技术降低电容失配对电路性能的影响.此外,采样开关使用栅压自举的结构来降低采样带来的失真,并且只采用MSB 部分进行采样,在MSB 部分增加一个单位电容代替LSB 部分进行采样.而比较器则采用带有两级预放大器的全差分比较器架构,以实现低失调和噪声.SAR 逻辑则使用了自定时同步时序,缓解了对DAC 建立时间的要求,并增加了预放大器复位相,以加快预放大器的响应速度.

图1 SAR ADC整体架构Fig.1 Overall structure of SAR ADC

1.1 基于GND采样的单调开关切换方案

本文所设计的SAR ADC 采用了基于GND 采样的单调开关切换方案,如图2所示.

图2 基于GND采样的单调开关切换方案的DAC输出Fig.2 DAC output voltage with ground sampling switching

传统的单调开关切换方案[8]是基于上极板采样,考虑上极板对地的寄生电容Cp,Cp上极板的电压在采样阶段时为输入信号,在转换结束后变为GND,因此Cp上存储的电荷量在转换阶段发生了改变,这会对ADC 的性能造成一定影响.而采用基于GND 下极板采样时,Cp上极板的电压在采样阶段和转换结束后都保持GND 不变,因此寄生电容不会给ADC造成非线性的问题.

本文所设计的SAR ADC 在采样阶段只有MSB部分进行采样,MSB部分正负两端上极板接GND,正端(P端)下极板接输入信号Vip,负端(N端)电容下极板接输入信号Vin,LSB 部分电容下极板接Vrefp.因此,电容阵列的总电荷为:

式中,CMt为MSB 部分总电容,CLt为LSB 部分等效总电容.

在采样阶段结束时,上极板开关先断开,所有电容的下极板接Vrefp,有:

式中,CTotal=CMt+CLt,为DAC阵列总电容.

根据电荷守恒:

式中,K=CMt/CTotal.

以图2为例,采样阶段结束后,VTOPP>VTOPN,比较器由CLK 下降沿触发,开始进行首位的比较,DP=1,Dn=0.因此,P 端最高位电容器下极板电压由Vrefp切换至Vrefn,N 端最高位电容器下极板电压保持Vrefp不变.由电荷守恒可知,

式中,C11为首位对应的电容值,大小为0.5CMt.

由此可见,虽然采样阶段仅采用了MSB 部分进行采样,使得采样电压乘以系数K,但在逐次逼近阶段,上极板的电压改变量0.5Vrefp也乘以了系数K,故不会影响ADC 的转换结果,但对比较器的最小分辨电压提出了高的要求.随后重复上述步骤,获得12bit的量化结果.

本文采用的改进的单调开关切换方案不需要共模电平,大大简化了开关的复杂度,而且在逐次逼近过程中仅存在由高电平向低电平的切换,而不存在由低电平向高电平的切换,因此缩短了电路的切换时间,有利于提高电路的响应速度.

1.2 失配误差校准

分段式SAR ADC 线性度取决于电容阵列的失配误差,可以通过校准技术进行补偿,然而这种方法会增大设计的难度,消耗大量的硬件成本[9].此外,ADC 的线性度还可以使用动态元件匹配技术(Dy⁃namic Element Match,DEM)来改善,但是这种方法的控制开销会随着位数的增加而呈指数式上升,因此所适宜的位数不应该太多.

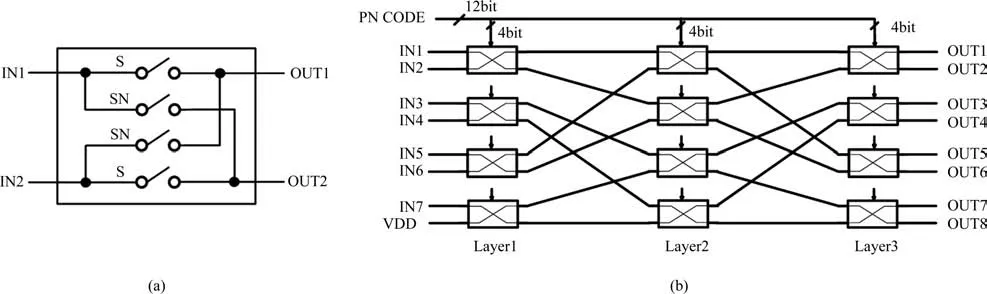

本文采用了由伪随机码控制的动态元件匹配技术[10],将5bit MSB 二进制数字码控制的DAC 阵列拆分成由32 个温度计码控制的最小单元,然后通过一个蝶形元件选择逻辑(Element Selection Logic,ESL)来对这些最小单元进行随机选择.以3bit 输入为例,本文采用的基于伪随机码控制的蝶形网络如图3 所示.通过这种方法,由于电容失配误差而引起的谐波失真将被随机化为白噪声,从而提高了ADC 的无杂散动态范围SFDR,而无需额外的数字处理电路.

图3 基于伪随机码的蝶形网络(3bit为例)Fig.3 Butterfly network based on pseudorandom code(example of 3-bit butterfly elements)

为了验证动态元件匹配技术对电容失配问题有良好的缓解作用,本文采用MATLAB 对于所设计的SAR ADC 建立了行为级模型,模型量化过程中只引入量化噪声.取输入频率为采样频率的43/(212),电容失配的标准差为0.5%时,有无DEM 时的输出频谱图如图4 所示.使用DEM 前后的无杂散动态范围SFDR 分别为76.9 dB 和92.6 dB.可以看出,当采用DEM时,谐波被打散,ADC性能得到提升.

图4 采用DEM技术前后ADC输出频谱图Fig.4 ADC output spectra with DEM on and off

本设计中,用伪随机序列控制最小单元电容,因此失配噪声将被转换为白噪声,如果选择其他的控制序列,例如数据加权平均算法DWA[11],则可以将失配误差进行一阶整形,ADC 的性能也可以得到进一步提升,但是算法和电路的复杂性将进一步增加.

2 具体电路设计

2.1 采样保持电路

采样保持电路是模数转换器设计的重要电路之一,其精度直接影响着ADC的转换精度,它的速度则决定了整体电路处理信号的速度.为了解决采样时的非线性问题,常采用栅压自举开关电路[12].

本文所采用的栅压自举开关电路结构如图5 所示,当CK 为低电平时,CKN 为高电平,NM0 导通,C0的下极板电压放电至GND.NM5 和NM6 导通,CK_BOOT 被置于GND,因此PM0 导通,C0的上极板电压充电至VDD,自举开关NM2 关断,电路处于保持阶段;当CK 为高电平时,CKN 为低电平,PM1 导通,CK_BOOT 被置于VDD,NM1 导通,C0下极板的电压从0 变为VI,由于C0两端电势差保持不变,所以C0上极板电压会相应提升到VDD+VI,从而NM2 管的栅源电压VGS不会随VI的变化而变化,即导通电阻与VI无关,因此采样信号不会产生高次谐波失真.

图5 栅压自举开关Fig.5 The bootstrapped switch

图6 为本文设计的栅压自举开关在不同阶段下的工作状态仿真图.从图中可以看出,当CK 为高电平时,电路处于自举阶段(或采样阶段),CK_BOOT被抬高为VDD+VI,VOUT始终跟随输入信号VI,此时CDAC 上极板电压VTOP保持为GND;当CK 为低电平时,CK_BOOT 同样也为低电平,CDAC 上极板电压VTOP将保持K×(Vrefp-VI)不变.

图6 栅压自举开关波形图Fig.6 Waveforms of bootstrapped switch

为了验证采样保持电路能否满足ADC线性度的要求,通过输入正弦信号对于采样开关进行功能验证,对VTOP取4 096 个点进行FFT 分析,结果如图7 所示.由图可知,采样保持电路的SFDR 为111.76 dB,SNDR 为104.24 dB,能够满足12 bit架构的SAR ADC对于采样保持电路的需求.

图7 采样保持电路输出频谱图Fig.7 S/H circuit output spectra

2.2 低失调电压比较器

比较器模块是ADC 电路中关键模块之一,它的精度和速度直接影响着整个SAR ADC 的精度和速度.为了降低比较器的失配所带来的直流失调,电路采用了全差分设计,并使用自动校零技术[13]来消除大部分失调电压.图8 是本文所设计的全差分比较器电路结构图,它采用二级预放大自动校零技术来消除失调电压.

图8 使用自动校零技术全差分比较器Fig.8 Differential comparator uzing auto-zero calibration

在失调电压校准阶段,开关S0~S5闭合,CDAC 上极板电压VIP和VIN置为0,电容阵列基于GND 进行采样.两个预放大器输入端短接,C0~C3的上极板被充电至VCM,被预放大器放大后的失调电压被存储在电容C0~C3上(大小都为C).C0~C3电容存储的电荷分别为:

其中,Av 是预放大器的增益,VOS为预放大器的输入失调电压.

在比较器工作阶段,开关S0~S5断开,比较器正常工作.此时,DAC 上极板由GND 变为输入信号,此时C0-C3电容上的电荷分别为:

其中,V0~V3分别为C0~C3电容上极板电压.

根据电荷守恒,并考虑到开关S2~S5的电荷注入效应,可得残余输入失调电压为:

其中,∆Q0为开关S2、S3向电容C2、C3的注入电荷失配量,∆Q1为开关S4、S5向电容C4、C5的注入电荷失配量.

由式(7)可以看出,二级预放大的输入等效失调电压VOS0、VOS1将被完全抵消,后级锁存器的输入等效失调电压VOSL会被除以预放大器的增益Av1×Av2,从而实现了比较器低失调电压和低噪声的设计.此外,在每一位比较完成后,预放大器输出节点短接,将预放大器输出复位,加快预放大器的响应速度.

为了验证比较器是否满足低失调电压的要求,本文对比较器的失调电压进行了200 次蒙特卡洛仿真,仿真结果如图9 所示.由图可知,自动校零技术显著降低了比较器输入失调电压的范围,失调电压的均值μ=-156.966 μV,方差δ=453.674 μV.

图9 比较器输入失调电压蒙特卡洛仿真图Fig.9 Monte Carlo simulation diagram of comparator input offset

2.3 SAR逻辑控制及寄存器电路设计

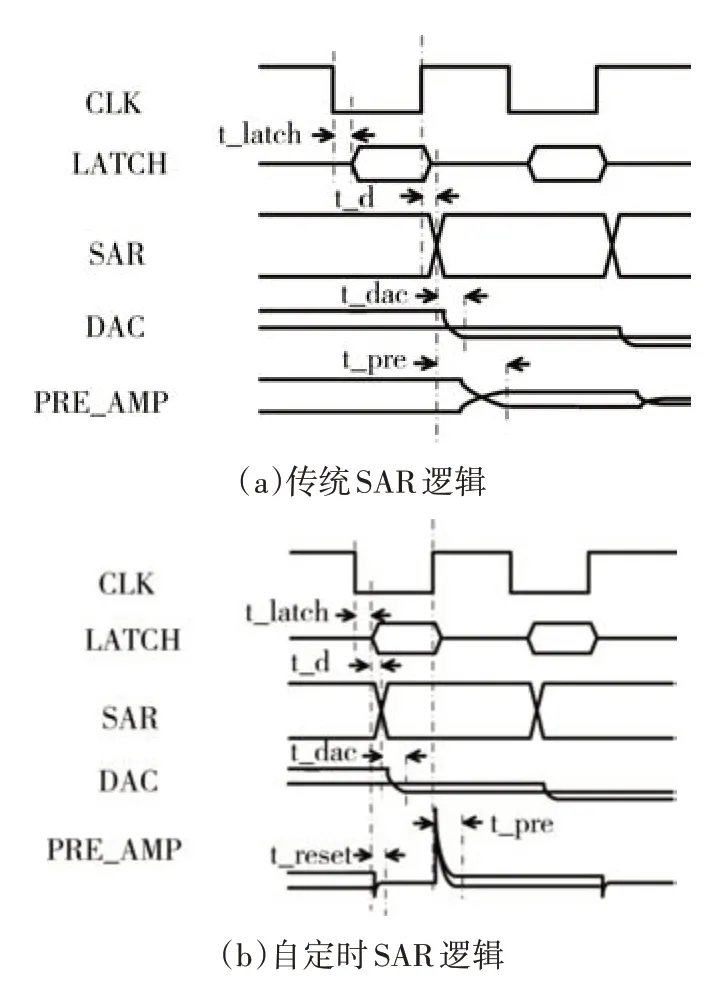

本文中ADC 采用自定时同步时序[14],与传统同步时序相比,自定时逻辑能够更好地提高DAC 和预放大器的效能,降低动态功耗.传统的同步时序每位的位转换如图10(a)所示,比较器由CLK 下降沿触发,锁存比较器经过t_latch得到稳定判决,而SAR 逻辑控制电路则工作在下半个周期,DAC 和预放大器随后开始建立.为了保证下一位的位转换能够正确判决,DAC 和预放大器的建立时间t_dac 和t_pre 均应小于半个时钟周期,增加了设计难度.而本文使用的自定时同步时序图如图10(b)所示,比较器得到稳定的输出结果后,SAR 逻辑立即开始工作,经过一定的逻辑延时DAC 也开始建立,此时预放大器输出端进行复位,并在下半个周期来临时开始工作.与传统的同步时序相比,自定时同步时序控制放宽了对逻辑电路的延迟和 DAC 建立时间的要求,并加快了预放大器的响应速度,有利于实现高速SAR ADC.

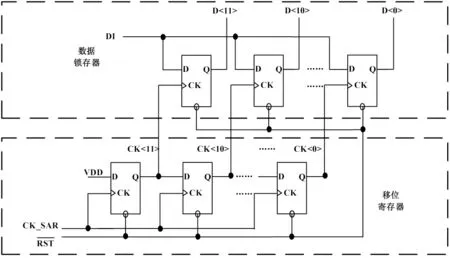

图10 传统和自定时SAR逻辑时序图Fig.10 Timing diagram of conventional and self-timed SAR logic

逐次逼近寄存器SAR 电路是SAR ADC 时序控制电路的核心部分,主要由移位寄存器和数据锁存器构成,如图11 所示.当采样时钟为高电平时,--------RST 置1,将锁存器复位.在转换阶段,当比较器稳定输出后,CK_SAR 置为高电平,移位寄存器产生时钟控制信号CK<11:0>,控制数据锁存器接受比较器结果DI,并将其锁存为D<11:0>,并控制DAC下极板开关切换.其中,D<11:7>经过译码器转换为温度计编码,控制32 个MSB 最小单元电容,D<6:0>则直接经过两级反相器控制LSB部分电容下极板接Vrefp/Vrefn.

图11 SAR电路原理图Fig.11 SAR schematic diagram

2.4 电容阵列

本文采用MIM电容,单位电容的尺寸为10 μm ×10 μm,单位电容值约为96.9 fF.对于采用本文分段结构的12 bit 差分SAR ADC 每端的电容阵列均需要130 个单位电容和一个桥接电容.包括dummy 电容在内,该SAR ADC 两端的电容阵列版图共占用了2 × 240 μm × 245 μm 的有效面积,约占据整个核心版图面积的32%,DAC电容布局示意图如图12所示.其中,d 为dummy 电容;Cb 为桥接电容;数字0~6 为LSB 部分7 位电容,由二进制码控制;T0~T31 为MSB部分电容,由温度计码控制.

图12 DAC电容布局示意图Fig.12 The diagram of DAC capacitors layout

3 仿真及测试结果

本文所设计的SAR ADC 基于SMIC 0.18 μm 的 CMOS 工艺环境完成了流片,图13 为芯片的显微镜照片,整个ADC 版图面积约为630 μm × 575 μm.由于内核面积较小,所以在剩余空间内对模拟电源和地、数字电源和地、正参考和负参考间加入大量耦合电容来抑制共模耦合噪声.由于电容失配对ADC 性能影响较大,综合对静态指标和动态指标的考量,ADC 在实际使用中舍去了最后一位的量化结果,仅作为11bit进行输出.

图13 SAR ADC显微镜照片Fig.13 Microscope photos of SAR ADC

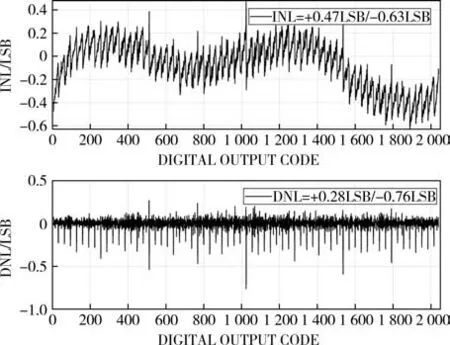

图14 为芯片DNL/INL 实测图,使用DEM 后INL=+0.47LSB/-0.63LSB,DNL=+0.28LSB/-0.76LSB.从图中可以看出,ADC 的INL 和DNL 每隔32 个码字就会发生一个较大的跳变,这可能是子DAC 的电容失配造成的.当输入信号为2 639.77 Hz时,使用逻辑分析仪采样214个点,并对结果进行FFT分析,结果如图15所示.芯片的信噪失真比SNDR 为65.0 dB,无杂散动态范围为77.8 dB,有效位数达到了10.51 bit.从图中可以看出,ADC 仍存在较明显的谐波失真,DEM对于电容失配的校准功能仍需要进一步改良.图 16 为不同输入信号幅度下ADC的信噪失真比对比.

图14 芯片DNL/INL实测图Fig.14 Measured diagram of DNL/ INL

图15 芯片在输入信号为2 639.77 Hz 时输出频谱图Fig.15 Chip output spectra with 2 639.77 Hz input signal

图16 不同输入信号幅度下SNDR测量结果图Fig.16 SNDR versus different input amplitude

在1.8 V电源电压下,本文设计的SAR ADC整体功耗为25.7 μW,FoMs为164.88 dB,FoMw为70.5 fj/step.其中,功耗占比最高的模块是比较器,主要是由于比较器的预放大级有直流功耗,在整个工作过程中都不会关闭.输入信号采样阶段,比较器需要做失调校准,而在转换阶段,比较器一直处于比较和复位过程中.SAR ADC的功耗分布图如图17所示.

图17 SAR ADC功耗分布图Fig.17 Distribution of SAR ADC power consumption

表1 对本文设计的SAR ADC 的性能进行了总结,并与近五年相关文献所提出的SAR ADC 性能进行对比.从表中可以看出,本文设计的SAR ADC 性能较好,在线性度、功耗、带宽、面积等方面具有良好的折中.

表1 SAR ADC性能总结及对比Tab.1 Summary and comparison of SAR ADC performance

4 结论

本文基于柔性皮肤压力传感器对于后端处理ADC 的要求,设计了一款基于GND 采样的SAR ADC,在DAC阵列采用分段式电容结构,以降低电容阵列的切换功耗,并减小芯片面积.此外,动态元件匹配技术的使用缓解了电容阵列失配对于ADC线性度的影响.最后,对芯片进行流片测试,测试结果证明,所设计的SAR ADC 基本上达到了预期目标,但是仍需进一步优化.可以进一步优化版图布局,改善因电容呈单调排列而可能引起的谐波失真[20];减小主DAC 和子DAC 之间的dummy 电容宽度,有益于降低LSB 部分上极板金属走线到dummy 的寄生,从而优化LSB 部分线性度.此外,还可以使用单位电容代替分数型桥接电容,改善桥接电容失配对于ADC 线性度的影响.