SerDes链路中的过孔设计

刘婷婷 张子春

摘要:随着SerDes链路信号传输速率的提升,PCB复杂度增加,信号越高走线和过孔设计对其正确传输的影响就越大,因此走线和过孔设计的研究就越发重要。文章通过搭建SerDes链路四级过孔走线模型,通过仿真得出,过孔的引入导致SerDes链路阻抗突变,码间串扰严重,设计中应尽量避免过孔的使用,如无法避免可以采用背钻和消盘处理,在一定范围内提高SerDes链路阻抗一致性,提升信号质量。

关键词:过孔;阻抗;眼图

中图分类号:U285.7文献标志码:A

0 引言

电子设备发展趋于小型化和功能化,印刷电路板 PCB(印刷电路板)上信号传输速率越来越高,走线密度和PCB层数不断增加。特别是在SerDes链路设计中,链路结构复杂,信号经多级PCB板传输,层数多达20层,链路传输信号速率高,常用的PCIE3.0达到了8 Gbps。此外,SerDes链路走线距离长,通常跨越3级连接器。针对SerDes链路设计的复杂性,在PCB走线过程中经常需要引入大量的过孔,这使得SerDes链路过孔设计成为影响信号完整性的重要因素。对于低速电路,PCB板的过孔可以看作是简单的金属孔,仅起着电气连通的作用。但是,在SerDes链路中,过孔就不能仅当作金属孔,必须考虑过孔的焊盘、反焊盘以及桩线等带来的寄生效应影响以及损耗。因此,SerDes链路系统设计,尤其是PCB进行板级和系统级设计时,必须考虑过孔的寄生效应引起的信号完整性问题。本文主要针对SerDes链路中过孔进行寄生参数的分析,并在此基础上对SerDes链路中的过孔进行优化设计。

1 SerDes链路过孔寄生参数分析

过孔是指PCB板上钻的小孔,用于连接PCB板的不同叠层。在SerDes链路PCB的设计中,由于布局布线空间的限制,经常会用到过孔。典型的过孔由金属柱、焊盘和反焊盘组成。由于过孔的不连续性结构,当其在低频情况下,人们完全可以将其看作一条普通的导线。然而,在高频的情况下,过孔则会产生寄生电容和电感[1]。随着信号频率的升高,过孔的寄生参数影响越来越明显[2]。如果处理不当就可能引起严重的SI、PI以及EMI问题。本研究进一步说明在高速信号的走线过程中过孔寄生参数对信号质量的影响。

过孔主要包括金属柱、焊盘和反焊盘,本文采用1个14 层的PCB板,过孔直径是10mil,焊盘半径是20mil,反焊盘半径是30mil,过孔的组成如图1所示。

在SerDes链路中,过孔设计较低速链路更加复杂,例如:差分信号本身的扇出孔以及周边的回流地孔。过孔焊盘、非功能性焊盘、反焊盘以及桩线[3]等物理结构产生的寄生效应对信号质量影响非常显著。因此,本文针对SerDes链路中的过孔开展深入的研究。

2 SerDes链路过孔设计及仿真分析

本文对差分过孔进行优化设计以及仿真分析,通过建立高速信号经过4对差分过孔的SerDes链路的走线模型,对过孔进行背钻以及消盘设计,得到SerDes链路插入损耗以及回波损耗的曲线,通过TDR时域反射计观察不同设计下的SerDes链路阻抗特性。

2.1 过孔设计及建模

在软件中建立4级过孔的SerDes链路走线模型。该模型是1个16层的PCB 板,板材采用TU-752,走线层分别3层、5层和12层,相邻参考层均为地层,与相邻层介电常数分别为4和4.07,差分线线宽4mil,差分线线间距12mil,过孔孔径10mil,焊盘孔径18mil,反焊盘孔径30mil。

在差分过孔走线模型基础上,本研究结合过孔寄生参数分析,对影响SerDes链路阻抗特性的过孔进行背钻和消盘设计。在常规PCB板制造中,按照钻孔文件对PCB板进行钻孔处理,之后对PCB板进行沉铜工艺,使得过孔金属柱连通导电。在SerDes链路走线过程中除走线层外,其他层无用的过孔因为其自身的寄生参数效应,会影响链路的阻抗一致性,采用背钻方法钻掉过孔无用的孔层,可以减少信号传输过程中的分叉。过孔除金属柱外,焊盘也会影响SerDes链路阻抗一致性,在背钻基础上对过孔多余焊盘进行消盘处理,去除非功能焊盘的存在,减少高速信号传输路径上的阻抗分叉,进一步提高SerDes链路传输一致性。

2.2 无源链路仿真

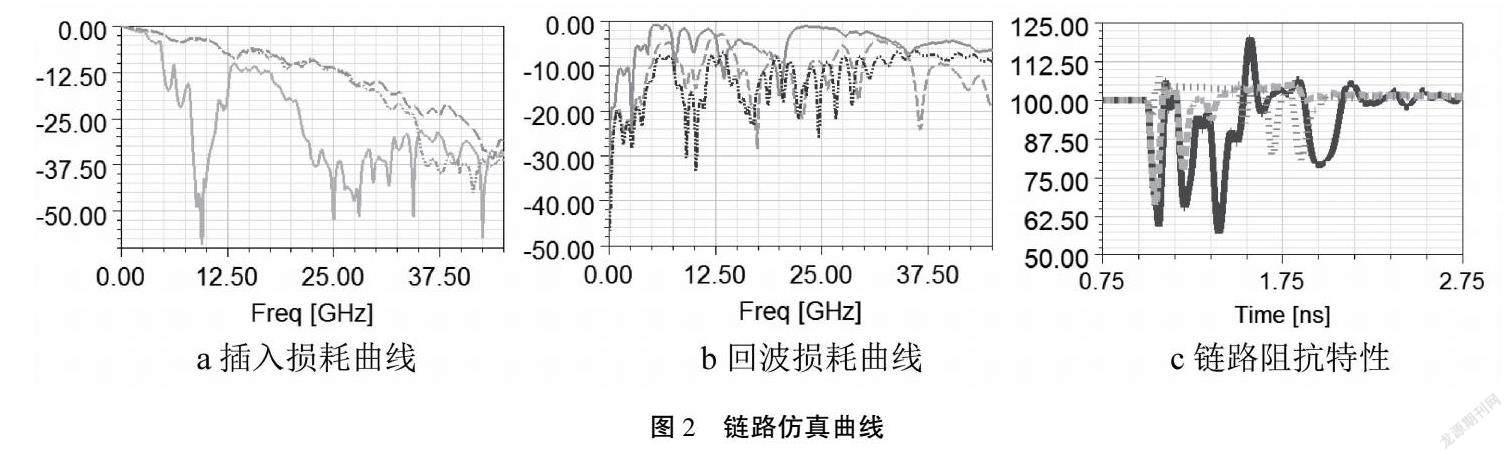

本文仿真得到4级过孔的SerDes链路走线模型下,1MHz~45 GHz频段SerDes链路插入损耗曲线如图2a所示,回波损耗曲线如图2b所示,链路的阻抗特性如图2c所示。

在图2a中,实线为差分信号线经过4级过孔后的插入损耗曲线图,长虚线为采用背钻处理后的插入损耗曲线图,短虚线为采用背钻和消盘处理后的插入损耗曲线图。从图2a可以看出,随着信号频率的不断提升,过孔插入损耗也越小,采用背钻处理可以有效增大插入损耗,利于信号高质量传输。

在图2b中,实线为差分信号线经过4级过孔后的回波损耗曲线图,长虚线为采用背钻处理后的回波损耗曲线图,短虚线为采用背钻和消盘处理后的回波损耗曲线图。从图2b可以看出,随着信号频率的不断提升,过孔回波损耗也越大,采用背钻和消盘处理可以有效降低回波损耗,利于信号高质量传输。

图2c实线为经过4级过孔SerDes链路的阻抗特性图,长虚线为采用背钻处理后的SerDes链路的阻抗特性图,短虚线为采用背钻和消盘处理后的SerDes 链路的阻抗特性图。从图2c中可以看出,差分过孔对SerDes链路设计中的信号传输影响较大,它会导致链路阻抗的突变。采用背钻处理后,链路阻抗突变位置和幅度减少。采用背钻处理可以进一步减少因SerDes链路过孔而引起的阻抗突变。

2.3 电气特性仿真

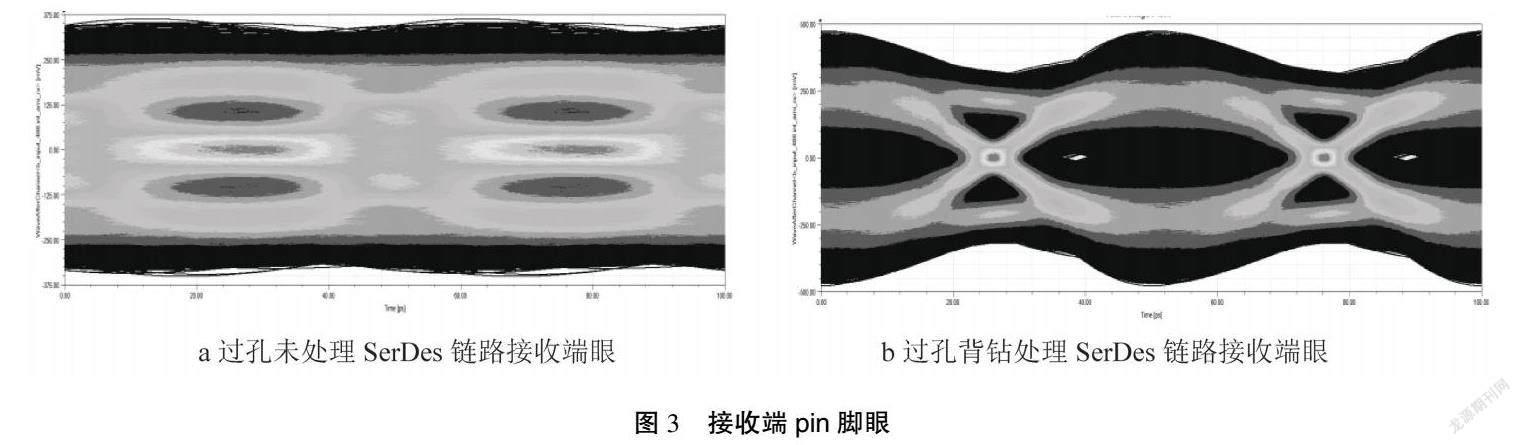

仅通过无源仿真结果难以全面反映SerDes链路的传输特性。在无源链路基础上增加驱动和接收模型,采用眼图来衡量SerDes链路的电气特性,从而更为全面的评估链路对信号传输质量的影响。数据传输速率为10 GHz,上升时间和下降时间为2.5 ps,图3为信号经过SerDes链路传输的接收端pin脚处的眼图。

经过眼图对比分析,经过4级过孔SerDes链路的接收端pin脚处眼图模糊不清,无法识别眼高眼宽大小,不满足电气特性的要求。采用背钻处理后的SerDes链路的接收端pin脚处眼图依然不够清晰,无法识别眼高眼宽大小。采用背钻和消盘处理后的SerDes链路的接收端pin脚处眼图清晰,能准确确定眼高眼宽。SerDes链路中连续4级过孔带来的阻抗突变和损耗,导致高频信号链路传输受限,信号波形在时域上展宽,从而出现了严重码间串扰,眼图混叠,影响信号质量。采用背钻和消盘处理后可以有限提升链路阻抗一致性,提升信号传输质量,进而SerDes链路接收端眼图的眼高、眼宽及眼图质量变好。

3 结语

本文通过PCB过孔的组成对SerDes链路中过孔的寄生参数进行分析,推导出影响过孔SerDes链路阻抗一致性的因素,在此基礎上建立4级过孔的SerDes链路走线模型,研究了背钻和消盘两种改善过孔性能的方法。基于仿真软件对搭建SerDes链路进行无源链路以及电气特性仿真,对过孔分别进行背钻和背钻消盘处理,进行链路的插入损耗、回波损耗、阻抗特性以及眼图仿真,观察背钻消盘处理对于SerDes链路传输特性的改善效果。对比发现,SerDes链路中引入过孔导致链路阻抗突变,信号传输出现多重反射,信号强度出现衰减,信号码间串扰严重,信号的完整性变差。在实际的设计中,应尽量避免过孔的使用,如无法避免,可以采用背钻和消盘处理在一定范围内提高SerDes链路阻抗一致性,提升信号质量。

参考文献

[1]尚文亚,刘丰满,王海东,等.PCB布线中的过孔和电容效应分析和结构优化[J].现代电子技术,2015(16):110-114.

[2]候莹莹,关丹丹.高速PCB中的过孔设计研究[J].电子与封装,2009(8):25-28.

[3]陈琼莲.基于PCB信号完整性分析与设计[J].科技信息,2009(3):487-488.

(编辑 王永超)