超宽带低功耗低噪声放大器芯片

刘莹 王测天 邬海峰 廖学介 王为

摘 要:介绍了一款基于GaAs 0.15 μm pHEMT工艺的2~18 GHz超宽带低功耗低噪声放大器芯片的设计,给出了在片测试结果。该芯片采用结合有源偏置和并联负反馈技术的改进型共源共栅放大结构,该结构可以使放大器在超宽带的工作频带范围内实现低噪声、低功耗和较高增益,同时减小放大器性能对工艺波动的敏感程度。在2~18 GHz的超宽带频率范围内,该芯片实测噪声系数≤1.4 dB,增益≥14 dB,且具有3 dB的正斜率,输出P-1功率≥12 dBm,输入输出驻波≤1.6,整个芯片功耗仅为0.15 W,芯片尺寸仅为:1.4 mm×1.1 mm×0.1 mm。

关键词:超宽带;低功耗;低噪声放大器芯片;有源偏置

中图分类号:TN72 文献标识码:A 文章编号:2096-4706(2023)01-0051-04

Ultra Wideband Low Power Consumption Low Noise Amplifier Chip

LIU Ying, WANG Cetian, WU Haifeng, LIAO Xuejie, WANG Wei

(Chengdu Ganide Technology Co., Ltd., Chengdu 610220, China)

Abstract: In this paper, the design of 2~18 GHz ultra wideband low noise amplifier chip based on GaAs 0.15 μm pHEMT process is introduced, and on wafer test results are presented. The chip uses and combines with the active bias and parallel negative feedback cascade amplifier structure, and the structure can make the amplifier achieve low noise, low power consumption and higher gain in the range of working frequency band of ultra wideband. At the same time, it reduces the sensitivity of amplifier performance to process fluctuations. In the 2~18 GHz ultra wideband frequency range, measured noise coefficient of the chip is less than and equal to 1.4 dB, a gain is more than and equal to 14 dB, and it has 3 dB Positive Slope, the output of P-1 power is more than 12 dBm, the input and output of VSWR are less than and equal to 1.6, and the power consumption of the chip is only 0.15 W. The chip size is only 1.4 mm×1.1 mm ×0.1mm.

Keywords: ultra wideband; low power consumption; low noise amplifier chip; active bias

0 引 言

隨着无线通信技术和电子对抗技术的快速发展,宽带芯片类核心元器件的需求越来越多,性能要求也越来越高,特别是在航天、军事、物联网、无线5G通信等领域,都向着更广的覆盖范围、更高的频段、更高的传输率、更广的覆盖范围、更强的兼容性的目标发展。因此宽带芯片的应用也越来越广泛。提高带宽可以使设备的兼容性更高,大大提高了电子设备的性能,满足不同应用场景的需求,降低成本、功耗和体积。

低噪声放大器应用在接收机的最前端,其性能直接影响着接收机的整体性能。肥皂水放大器的噪声系数和增益决定了接收机的信噪比,极大程度的影响着整个系统的噪声性能,若低噪声放大器自身的噪声系数不好,则会使噪声信号形成杂波,造成信号失身,降低系统的灵敏度。因此低噪声放大器性能的好坏直接影响接收机的灵敏度,而如何在宽带工作范围内涉及出性能优良的低噪声放大器一直是研究的热点和难点。

对于芯片工艺的选择,GaAs工艺是Ⅲ-Ⅴ族半导体工艺中常用的一种工艺,也是当前最重要,技术成熟度最高的化合物半导体材料之一,对比GaAs化合物和硅基工艺的优缺点,GaAs有较高的电子迁移率,具有高晶体管跨导,其增益和噪声系数性能更优;而且相比硅基工艺的衬底绝缘性能更好,电感电容Q值更高。而对于GaAs工艺中晶体管的类型的选择,HEMT高电子迁移率晶体管相较于HBT双极性晶体管,在噪声系数方面具有明显优势。综合考虑,为了实现2~18 GHz超宽带工作频带内的低噪声和中功率输出特性,该芯片选择基于GaAs 0.15 μm PHEMT工艺来设计。

本文介绍的基于GaAs 0.15 μm pHEMT工艺2~18 GHz低噪声放大芯片不仅在超宽带频带内具有低噪声和低功耗的优点,而且还具有正斜率的高增益特性,同时其对工艺波动的敏感度较低,具有很好的实际应用性能。

1 低噪声放大芯片的设计

1.1 电路结构的选择

低噪声放大器基本性能指标包括小信号增益、噪声系数、回波损耗、稳定性、输出功率1 dB压缩点、线性度、功耗等。低噪声放大器的增益特性代表的是其对小信号的放大能力,可以通过二端口网络理论进行公式推导。低噪声放大器的噪声系数是其重要指标,它指的是输入信噪比和输出信噪比的比值,直接影响了整个系统的噪声系数好坏。对于宽带放大器的设计,难点在于晶体管呈每倍频程增益下降的规律,端口驻波、功率也会随之变差,噪声系数也会恶化,此外稳定性是放大器能够正常工作的前提,设计中必须保证放大电路在全频带范围内保持绝对稳定状态,这也是宽带放大器设计的一个难点。

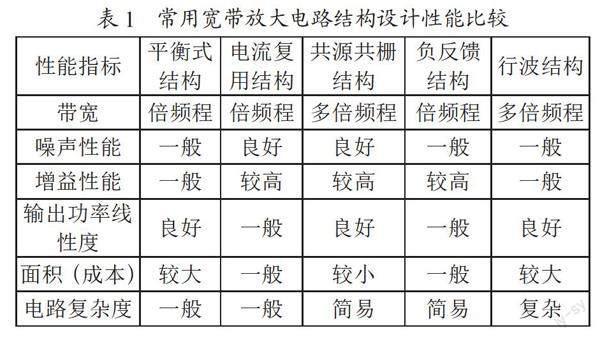

国内射频宽带低噪声放大器的设计研究在近几年发展快速,取得了丰富的研究成果,在技术和结构上取得了突破性的进展。目前,业界广泛使用且较为成熟的宽带放大去电路结构主要包括:平衡式宽带结构、电流复用宽带结构、共源共栅宽带结构、负反馈结构、行波宽带结构等,而每种结构各有其优缺点,表1对常用宽带放大电路结构的设计性能进行比较。实际电路设计中,往往不是采用单一的宽带技术,而是结合多种宽带技术,发挥每种技术的优势,同时利用其他技术改进其不足,不断提高电路的整体性能。

芯片电路设计中对电路结构的选择十分重要,需要设计者根据详细的设计指标要求,对比每种结构的优缺点,选择适合的电路拓扑。由表1中各种宽带放大器电路结构的性能对比可见,本设计需要在2~18 GHz超宽带频带内实现低噪声、较高增益和中等的输出功率,且满足较低功耗和低成本的要求,需要选择噪声系数良好,增益和输出功率性能良好且面积较小的电路结构,综上分析,因此该芯片采用共源共栅宽带放大结构,并结合并联负反馈结构;RLC并联负反馈和新型直流馈电结构达到进一步拓展带宽,提高电路稳定性的效果;采用共源共栅结构达到提高输出电压摆幅、电路的增益和隔离度的效果;同时由于本设计选择的工艺放大管类型为增强型晶体管管,先比于耗尽型晶体管,它可以实现单电源供电且具有较优的噪声系数,但其对工艺参数的波动更敏感,因此在共源管的栅极偏置部分采用新型有源偏置结构来改善电路随工艺波动的敏感度。

1.2 放大器的设计

该2~18 GHz超宽带低功耗低噪声放大器芯片的电路拓扑如图1所示。为了在超宽带范围内获得较低噪声、较高增益和中等功率特性,放大电路部分采用改进的共源共栅结合并联负反馈结构;放大电路的直流偏置部分,为放大晶体管提供合适的静态工作点,放大电路在该工作点在能正常工作,发挥出良好稳定的射频性能。直流偏置部分的滤波网络还需滤除电源纹波杂波,隔离射频与直流信号以保证电路正常工作。对于共源晶体管栅极偏置部分采用新型有源偏置结构,对于共栅晶体管栅极偏置部分采用无源偏置结构,对于共栅晶体管漏极Vdd供电部分采用两个扼流电感串联,并引入RC并联单元已消除带内谐振点的结构来拓展低频带宽,同时电源端口采用并联C1地和串联RC到地电路实现对电源低频和高频自激不稳定信号进行抑制。由于选用的晶体管工艺为增强型工艺,其噪声系数和gm均占优势,但工艺波动较耗尽型工艺略差,因此栅极偏置采用的新型有源偏置结构具有栅压补偿效果,能够减小芯片性能随工艺波动的敏感度,提高芯片一致性,同时提高电路的线性度。

通过对放大晶体管进行直流分析,可选取晶体管的直流工作点(如图2所示),根据指标要求,对晶体管进行小信号特性(如图3所示)和loadpull 输出1 dB功率特性(如图4所示)分析比较,选定晶体管的尺寸大小。该芯片共源共栅放大单元采用4×50 μm栅宽的晶体管。

在确定了放大器的电路结构、晶体管尺寸大小和直流工作点后,可以对放大器的输入输出端进行阻抗匹配设计;对于RLC并联负反馈部分,电容C为隔直作用,低频处需要很大的容值确保负反馈信号通过,电阻R主要影响反馈量,通过调整阻值大小来调整负反馈深度。芯片设计中,结合阻抗匹配技术给元件赋予合适的初始值,再以增益、噪声、输入/输出驻波、P1dB等指标为目标进行指标优化,反复调整指导放大器的原理图达到设计指标的要求并留有一定冗余量;接下来进行版图的设计优化,并根据版图布局需要反过来对原理图电路进行调整,反复优化迭代至指标满足要求。最终整体版图设计完成后,再根据DRC规则做check和修改,确认性能后就可以进行流片。

2 实验结果

流片后的2~18 GHz超宽带低功耗低噪声放大器的芯片实物照片如图5所示。整体芯片的尺寸仅为:1.4 mm×1.1 mm×0.1 mm。

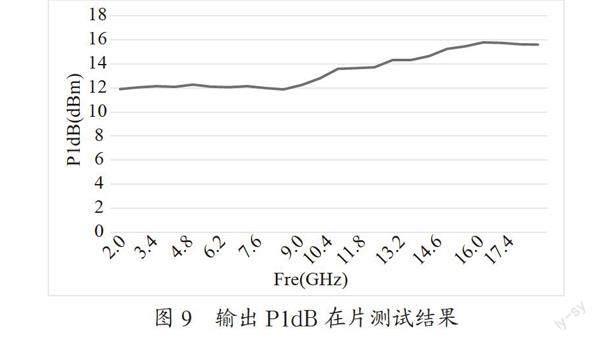

对该超宽带低功耗低噪声放大器芯片进行了探针台在片测试,其中射频探针采用间距150 μm的GSG探针,直流探针采用单针进行+5 V馈电。在常温工作条件下,直流偏置电压为Vdd=5 V,得到芯片工作电流Idd=28 mA。该芯片的在片测试结果如图6~图9所示。图6为低噪声放大器噪声系数的实测曲线,噪声实测结果≤1.4 dB;图7为低噪声放大器小信号增益的实测曲线,小信号增益实测结果在全频段范围内为14~17 dB,且为正斜率;图8为低噪声放大器输入输出驻波的实测曲线,输入输出驻波实测结果均≤1.6;图9为低噪声放大器输出P1dB功率实测曲线,输出P1dB功率在全频段范围内≥12 dBm;所有指标实测结果均达到设计指标要求。

3 结 论

本文主要介绍了一款基于GaAs 0.15 um pHEMT工艺的2~18 GHz超宽带低功耗低噪声放大器芯片的设计过程和在片测试结果。该芯片采用结合有源偏置和并联负反馈技术的改进型共源共栅放大结构,该结构使放大器在超宽带的工作频带范围内实现了低噪声、低功耗、较高的增益和功率特性,同时减小了放大器性能受工艺波动的敏感程度。由在片测试结果可知,在2~18 GHz超宽带工作频率范围内,噪声系数≤1.5 dB,增益≥14 dB,且具有3 dB的正斜率,输出P-1功率≥12 dBm,输入输出驻波≤1.6,功耗<0.15 W,芯片尺寸仅为:1.4 mm×1.1 mm×0.1 mm。该低噪声放大芯片实测结果良好,具有超宽带、低功耗、低成本、高性能的優势,在电子通信系统中有广泛的应用前景。

參考文献:

[1] PAN Z,QIN C,YE Z,et al. Wideband Inductorless Low-Power LNAs with Gm Enhancement and Noise-Cancellation [J].IEEE Transactions on Circuits and Systems I: Regular Papers,2018,65(1):26-38.

[2] CHAO S,KUO J,LIN C,et al. A DC-11.5 GHz Low-Power,Wideband Amplifier Using Splitting-Load Inductive Peaking Technique [J].IEEE Microwave and Wireless Components Letters,2008,18(7): 482-484.

[3] 程曦,邱义杰.6~18GHz小型化低噪声放大器的设计 [J].微波学报,2012,28(5):85-88.

[4] ZHANG H ,FAN X,Sinencio E S. A Low-Power,Linearized,Ultra-Wideband LNA Design Technique[J].IEEE Journal of Solid-State Circuits,2009,44(2):320-330.

[5] NGUYEN D P,PHAM B L,PHAM T,et al. A 14–31 GHz 1.25 dB NF enhancement mode GaAs pHEMT low noise amplifier[C]//2017 IEEE MTT-S International Microwave Symposium (IMS).Honololu:IEEE,2017:1961-1964.

[6] ZHANG H,QIAN G,ZHONG W,et al. A 3–15 GHz ultra-wideband 0.15-μm pHEMT low noise amplifier design[C]//2016 IEEE International Conference on Communication Systems (ICCS).Shenzhen:IEEE,2016:1-4.

[7] WENG R M,LIU C Y,LIN P C. A Low-Power Full-Band Low-Noise Amplifier for Ultra-Wideband Receivers [J].IEEE Transactions on Microwave Theory and Techniques,2010,58(8):2077-2083.

[8] MOEZ K,ELMASRY M I. A Low-Noise CMOS Distributed Amplifier for Ultra-Wide-Band Applications [J].IEEE Transactions on Circuits and Systems II: Express Briefs,2008,55(2):126-130.

作者简介:刘莹(1986.05—),女,汉族,四川夹江人,高级工程师,硕士研究生,研究方向:射频微波毫米波芯片设计。

收稿日期:2022-09-26