基于HyperLynx 的LPDDR4 信号完整性分析与优化*

刘跃成 甄国涌 储成群 单彦虎 石建华

(1.中北大学电子测试技术国家重点实验室 太原 030051)(2.西安子国微科技有限公司 西安 710065)

1 引言

信号完整性是指信号在传输过程中能够保持稳定不受外界干扰的能力[1]。随着DDR 的迭代发展,其数据传输速率在大幅度增长,根据JEDEC 发布的标准,LPDDR4 信号传输速率最高已经可以达到3200MT/s~4266MT/s[2]。DDR 在性能提升的同时,信号传输时的过冲、下冲、振铃等信号产品完整性问题也愈发严重,如果在设计时不加注意,很容易造成舰船上相关电子设备的信号传输质量无法满足要求,影响舰船电子设备的正常工作。通过对高速信号的仿真去分析、指导硬件电路的信号完整性设计,可以有效地解决上述问题,提高设计的可靠性[3]。因此,近些年国内外非常重视对信号完整性设计的研究。国外对信号完整性的研究起步较早,Eric Bogatin 博士在2005 年出版的信号完整性分析设计书籍至今仍在全球畅销[4],国内的李玉山教授后来也对这本书籍进行了翻译。三星、镁光、英特尔等公司都具备很成熟的信号完整性设计体系,在信号完整性的研究上走在前列[5]。国内对信号完整性的研究起步较晚,华为、紫光、中兴三家公司对信号完整性的研究较为成熟,在国内处于领跑地位。但总体来看,国内对信号完整性的研究设计还有待加强,不少公司还停留在依靠“经验法则”进行布局布线设计,缺乏足够的理论支撑[6]。

基于此,通过HyperLynx 电路仿真验证工具,对传输线信号带宽、耦合线宽、耦合间距等影响LPDDR4 信号完整性的关键性因素进行定量仿真分析,根据仿真结果给出提高LPDDR4 信号完整性的优化方法,有效地解决了LPDDR4 高速信号的信号完整性问题,一定程度上为LPDDR4 的应用设计提供了参考依据。

2 理论分析

信号完整性问题是多种因素复合产生的结果,由于现阶段工艺水平的限制以及器件内部各种非理想因素的存在,LPDDR4 信号线在高频状态不可避免地会出现信号完整性问题,但其主要原因还是在于阻抗不匹配导致的信号反射和信号线间相互串扰的影响。故对反射和串扰的形成机理和影响进行理论分析。

2.1 反射

信号传输实际上就是信号从驱动端经传输线到达接收端的过程。当驱动端、接收端、传输线三者任意位置处出现阻抗不匹配时,就会在阻抗突变处产生局部反射,反射回去的信号和传输过去的信号数量由反射系数P所决定[7]。

其中Z2是信号阻抗突变后所在区域的阻抗,Z1是信号阻抗突变前所在区域的阻抗。当阻抗Z2大于Z1时,反射系数为正,信号在传输路径上产生正反射,信号在阻抗突变处产生信号叠加,极限情况为接收端开路时,此时接收端阻抗无穷大时,反射系数P 值接近1,接收端电压是入射电压的两倍。当阻抗Z2小于Z1时,反射系数为负,信号在传输路径上产生负反射,极限情况为接收端短路时,此时接收端阻抗为0,反射系数P 值为-1,接收端电压为0。

信号的反射会造成信号实际电压值超过理论设定值。定义信号上升过程中第一个超过设定电压值的峰值或者下降过程中第一个超过设定电压值的谷值为过冲,信号上升过程中出现过冲之后的下一个谷值或者下降过程中出现过冲之后的下一个峰值称为下冲。如果在信号上升沿或者下降沿上出现波形的非单调性,称之为回沟。如果路径上有多处阻抗不匹配点,那么反射的能量无法被及时吸收,就会在一个时钟周期内反复出现电平振荡,被称为振铃。过冲、下冲、回沟、振铃都是常见的信号完整性问题[8]。

过冲、下冲、回沟、振铃等信号完整性问题很大程度上是因为信号反射造成的,而减小信号反射的有效途径就是使得信号驱动端、接收端、传输线的阻抗保持一致。信号驱动端和接收端的内部阻抗由芯片制造厂家所设计,传输线的特性阻抗由传输线线宽、介电常数、传输线与参考层的间距等参数所共同决定,通过调整这些参数的值可以使信号线的阻抗值维持在合适的范围内。通常将传输线单端阻抗控制在50Ω左右,差分阻抗控制在100Ω左右。此外,如果传输线布线时存在90°以下的拐角,也会很容易导致传输线阻抗的改变,所以布局布线时要避免出现锐角走线。同时,信号内层走线时的通孔,信号线上的测试点,多余的线头,都会由于信号无法继续向前传输而出现Stub 效应导致信号完全反射回来[9],设计时要尽量避免。

2.2 串扰

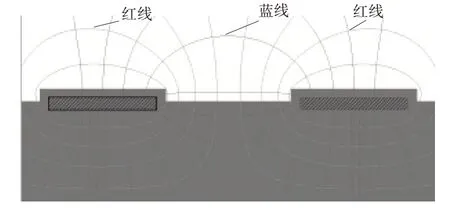

从能量场的角度讲,高频下信号线在信号传输时会向外辐射电场和磁场,如图1 所示,蓝色线是相邻信号线间的电场作用的电场线,红色线是相邻信号线间的磁场作用的磁场线。信号线间的电场作用和磁场作用会干扰与之相邻的信号线,这种干扰称之为串扰,当信号线距离过近时,串扰会表现的更加明显,对信号线的特性阻抗和传输速度造成影响。

图1 串扰能量场示意图

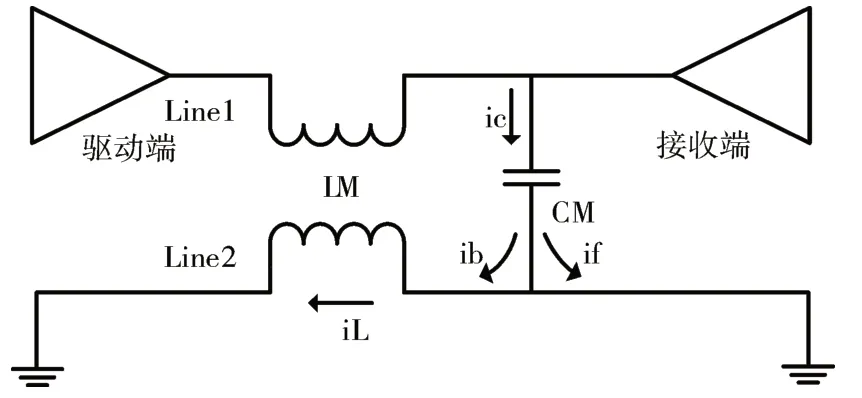

从传输线耦合的角度讲[10],当传输线上有变化的电流通过时,会因为互感作用在另一条信号线上产生电压。当传输线上有电压变化时,会因为互容作用产生变化的电流。设相邻导线间的互感系数为LM,互容系数为CM。则由互感引起的串扰电压[11]。

由互容引起的耦合电流[11]:

如图2 所示,当Line1 上有从驱动端到接收端的信号通过时,Line2 上由于互感作用产生向后的互感电流iL、由于互容作用产生向前的电流ib和向后的电流if。因此串扰对相邻传输线的两端都有影响,定义靠近驱动端的传输线受到的串扰为近端串扰,远离驱动端的传输线受到的串扰为远端串扰。

图2 传输线耦合示意图

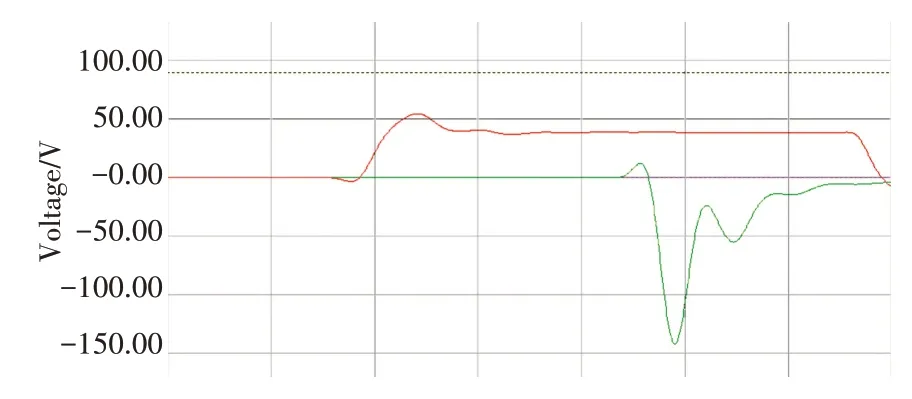

图3 近端串扰和远端串扰

远端串扰的耦合电流流向与Line1电流流向相同,因此Line2 上的前向耦合电流与已经存在的前向耦合电流不断叠加,最终表现在V/t 信号图上为幅值较高但持续时间较短的脉冲型干扰。近端串扰的耦合电流流向与Line1 电流流向相反,其在传输周期内耦合电流是以恒定的速度流向近端,不会进行叠加,在信号图上表现出幅值较低、持续时间较长的特点。

3 阻抗匹配方案设计与优化

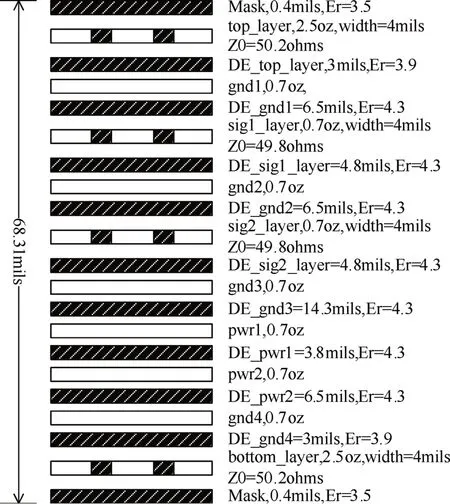

3.1 叠层设置

综合考虑加工工艺、布局走线、阻抗控制、设计成本等因素,采用如图4 所示PCB 叠层设计,使信号层单端走线阻抗尽量控制在50Ω左右,差分走线控制在100Ω左右,并使外层信号层有一个地层做信号返回路径,内层信号层有两个地层做返回路径,以保证信号层回流路径有完整的参考地平面,减少信号间串扰、提高信号完整性。

图4 LPDDR4 PCB板层叠设置示意图

3.2 阻抗匹配分析

如图5 所示为主控芯片与LPDDR4 发送数据的简化电路图,传统低速信号驱动端输出阻抗低,接收端输入阻抗高,以使信号源的驱动电压可以最大程度的分担到接收端上,同时保证驱动端输出的电流值相对较大。高速信号下为使驱动端、接收端、传输线的阻抗匹配,在驱动端和接收端内部集成串联电阻R1 和并联电阻R2,通过调节R1、R2 的阻值可以使得驱动端和接收端的阻抗值维持在与传输线一致的范围内[12]。

图5 主控芯片与LPDDR4发送数据简化电路图

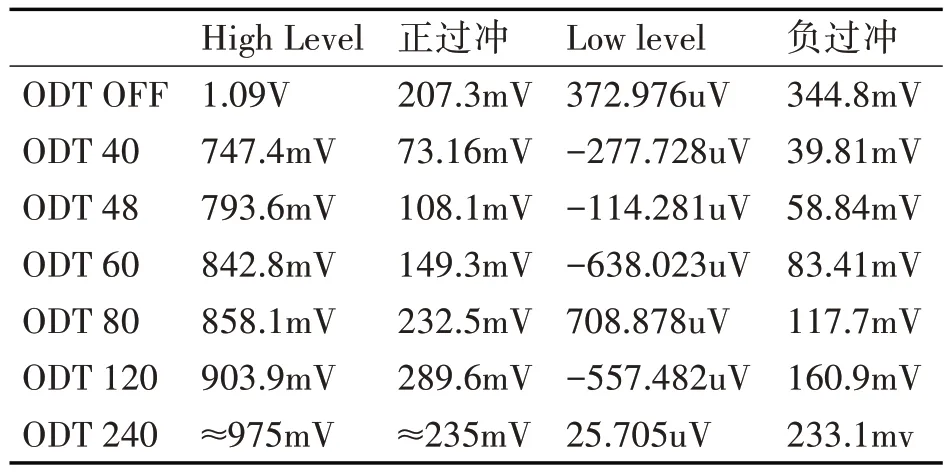

LPDDR4 有内部40Ω、48Ω、60Ω、80Ω、120Ω、240Ω 的ODT 端接电阻可选,主控芯片有25Ω、40Ω、60Ω、75Ω、90Ω、132Ω驱动电阻可选,为找到最佳阻抗匹配值,通过控制变量法进行逐步扫描分析比较,分析如下。

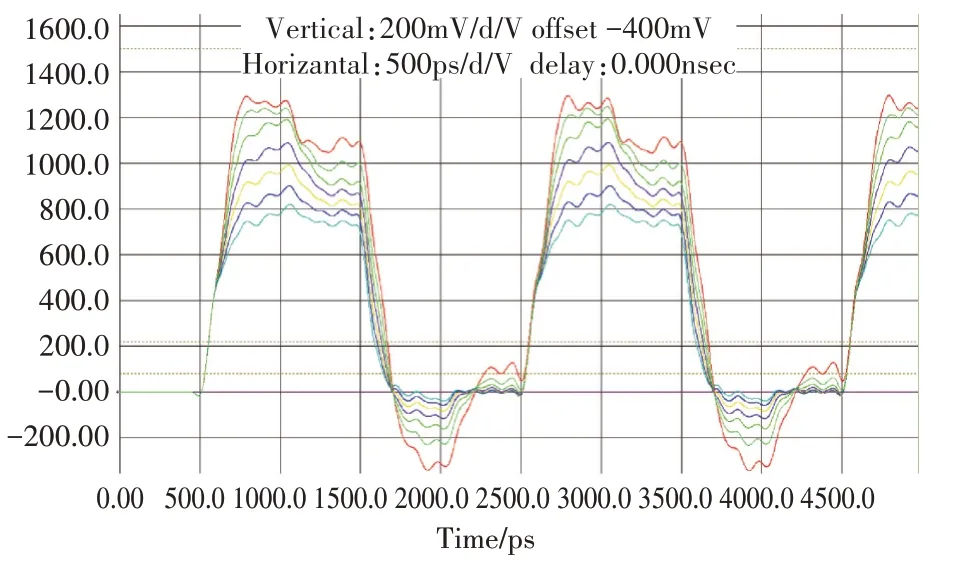

选择主控芯片驱动电阻为25Ω,施加500MHz&50%占空比的周期激励、扫描LPDDR4 ODT 电阻为40Ω、48Ω、60Ω、80Ω、120Ω、240Ω时SDQ20 数据线的接收信号,得到图6 所示波形图,根据波形图结合表1 仿真数据关键参数可以看出,当ODT端接电阻为40Ω时信号质量最佳,因此可以认为,当ODT 端接电阻为40Ω时,LPDDR4 输入阻抗与50Ω传输线阻抗最为接近。

表1 ODT电阻扫描波形关键参数表

图6 不同ODT电阻扫描波形图

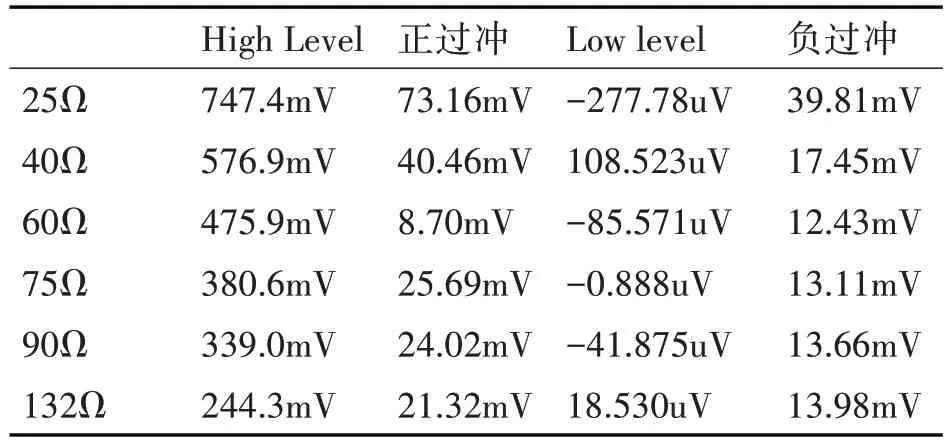

选择LPDDR4 ODT 电阻为40Ω,施加500MHz&50%占空比的周期激励、扫描主控芯片驱动电阻为25Ω、40Ω、60Ω、75Ω、90Ω、132Ω时SDQ20 数据线的接收信号,得到图7所示波形图。

表2 驱动电阻扫描波形关键参数表

由2.1节的理论分析可知,当信号发送端、传输线、信号接收端三者中有两者阻抗匹配时,就可以很大程度地减少信号反射、所以在LPDDR4 ODT电阻为40 欧姆时,主控芯片端接驱动电阻在40Ω、60Ω、75Ω、90Ω、132Ω时SDQ20 数据线的接收信号波形均相对较好,但端接驱动电阻会分走一部分电压使得LPDDR4 信号接收端High level 值降低,且阻值越大,分走的电压越多,而过低的High level值会导致“0”和“1”的电平信号不明确,容易造成电平误判。

综合考虑以上因素,LPDDR4 ODT 电阻选择40Ω、主控芯片端接驱动电阻选择40Ω或者60Ω属于比较理想的阻抗匹配方案。

4 传输线仿真与设计优化

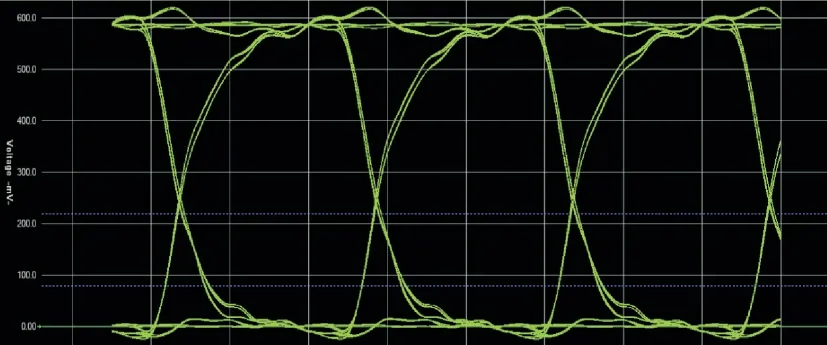

4.1 不同传输线间距仿真分析

仿真设置:选取TOP 层相邻传输线SDQ1、SDQ2 进行仿真分析、耦合线长取1000mil、传输线线宽4mil、TOP 层阻抗50.2ohms、主控芯片驱动电阻选取40Ω、LPDDR4 ODT 电阻选取40Ω,线间距选取1W、2W、3W、4W、5W(W为传输线线宽)。

图8 不同传输线间距扫描波形图

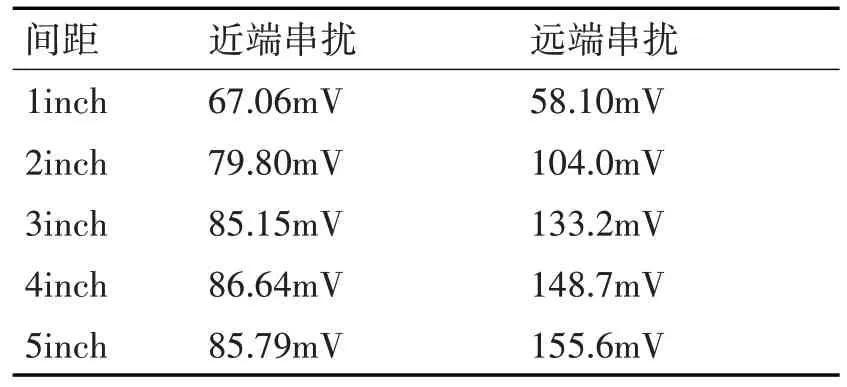

表3 不同传输线间距下的近端串扰和远端串扰

可以看出,串扰值随着传输线间距越大而逐渐越小,增大传输线间距可以极大程度减小串扰的影响,这是因为传输线间距增大以后传输线的互感值减小,串扰也随之减小,所以传输线间距需要尽可能保持在3倍线宽以上。

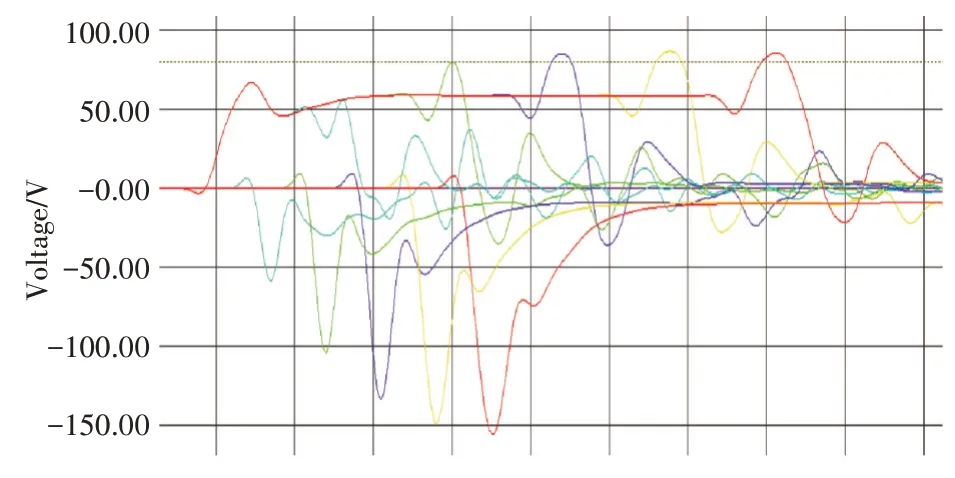

4.2 不同耦合长度仿真分析

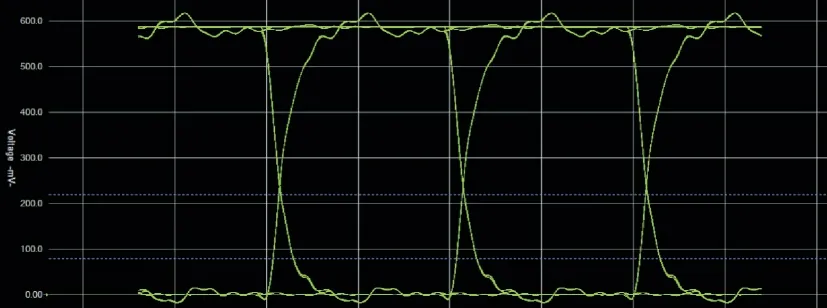

仿真设置:选取TOP 层相邻传输线SDQ1、SDQ2 进行仿真分析、传输线线宽4mil、传输线间距4mil、TOP 层阻抗50.2ohms、主控芯片驱动电阻选取40Ω、LPDDR4 ODT 电阻选取40Ω,耦合长度选取1inch、2inch、3inch、4inch、5inch。

图9 不同耦合长度扫描波形图

表4 不同耦合长度下近端串扰和远端串扰

可以看出,近端串扰值受耦合长度的影响不大,但近端串扰的持续时间会随着耦合长度的增加而增加。远端串扰值受耦合长度影响较大,随着耦合长度增加,远端串扰值逐渐加大,尤其在1inch到3inch中,串扰影响表现的更加显著。

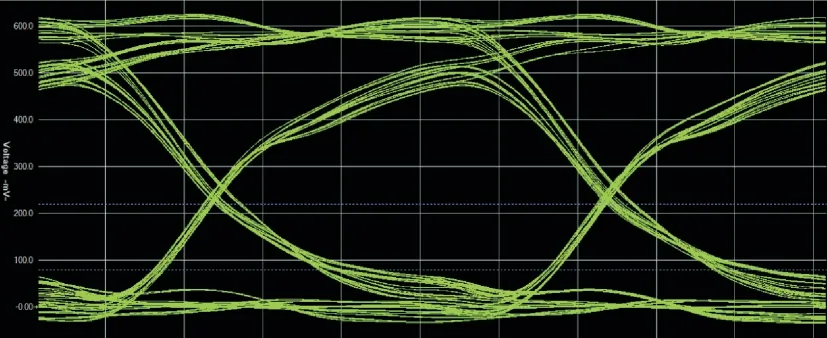

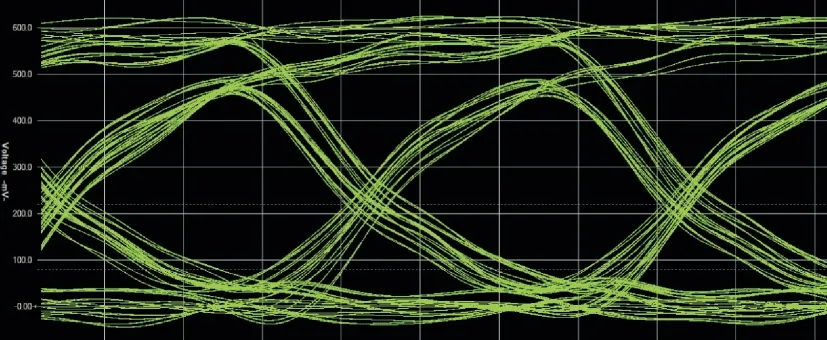

4.3 不同传输速率仿真分析

仿真设置:选取SDQ20 传输线进行仿真分析、传输线线宽4mil、TOP 层阻抗50.2ohms、SIG1层阻抗49.8ohms、主控芯片驱动电阻选取40Ω、LPDDR4 ODT 电阻选取40Ω。激励选择PRBS(Pseudo Random Binary Sequence)伪随机二进制序列,传输线传输速率选择1Gbps、2Gbps、3Gbps、4Gbps、5Gbps。

图10 所示为传输速率1Gbps 时SDQ20 传输线的眼图,其眼宽958.750ps,眼高578.2mV,平均高电平值592.7mV,正过冲24.98mV,平均低电平值487.889μV,负过冲17.85mV。

图10 1Gbps速率下SDQ20信号线眼图

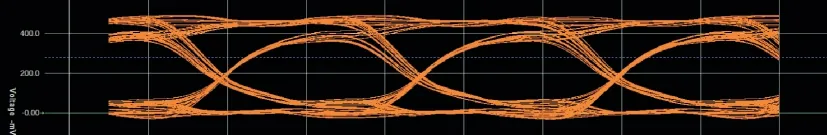

图11 所示为传输速率2Gbps 时SDQ20 传输线的眼图,其眼宽468.226ps,眼高551.3mV,平均高电平值573.6mV,正过冲48.00mV,平均低电平值4.01mV,负过冲28.71mV。

图11 2Gbps速率下SDQ20信号线眼图

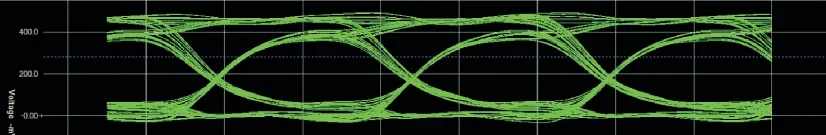

图12 所示为传输线传输速率3Gbps 时SDQ20传输线的眼图,其眼宽287.958ps,眼高458.3mV。平均高电平值562.4mV,正过冲61.37mV,平均低电平值19.43mV,负过冲50.46mV。

图12 3Gbps速率下SDQ20信号线眼图

图13 所示为传输线传输速率4Gbps 时SDQ20传输线的眼图,其眼宽218.332ps,眼高377.4mV,平均高电平值535.5mV,正过冲90.30mV,平均低电平值19.53mV,负过冲54.38mV。

图13 4Gbps速率下SDQ20信号线眼图

图14 所示为传输速率5Gbps 时SDQ20 传输线的眼图,其眼宽138.797ps,眼高361.1mV,平均高电平值520.9mV,正过冲104.7mV,平均低电平值27.21mV,负过冲70.93mV。

图14 5Gbps速率下SDQ20信号线眼图

可以看出,随着传输速率增大,眼图厚度逐渐变厚,眼宽逐渐变窄、眼高逐渐变低、信号裕量逐渐减少、噪声逐渐增大;但因为满足阻抗匹配的要求,所以5Gbps 传输速率下眼图仍有一定张开幅度,仍具有比较不错的信号质量。

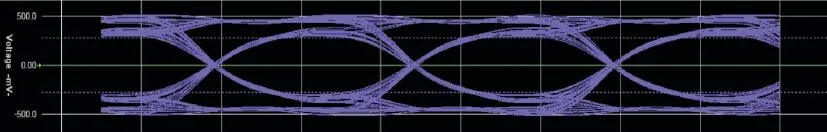

4.4 差分时钟信号仿真分析

仿真设置:选取SDQS2_P、SDQS2_N 差分时钟信号进行仿真分析、差分线线宽4mil、差分线间距4mil、TOP 层单端阻抗50.2ohms、SIG1 层单端阻抗49.8ohms、主控芯片驱动电阻选取60Ω、LPDDR4 ODT 电阻选取40Ω。激励选择PRBS(Pseudo Random Binary Sequence)伪随机二进制序列,信号传输速率选择4Gbps。

图15 4Gbps速率下SDQS2_P信号线眼图

图16 4Gbps速率下SDQS2_N信号线眼图

图17 4Gbps速率下SDQS2_P&SDQS2_N差分信号线眼图

在4Gbps 速率下、SDQS2_P 信号线眼宽204.039ps、眼高290.5mV;SDQS2_N 信号线眼宽207.208ps、眼高281.0mV;而其差分信号眼宽237.243ps、眼宽575.7mV。差分信号的眼宽、眼高相比单端信号均有提高,同时,差分时钟信号眼图开合较为工整、波形比较光滑,上升沿、下降沿均无回沟现象。可见,差分信号的确可以提升信号的抗干扰能力。

5 结语

文章对反射、串扰的形成机理进行理论分析,通过合理设置层叠参数将LPDDR4 信号线单端阻抗维持在50Ω左右,差分线阻抗维持在100Ω左右,并通过控制变量与参数扫描结合的方法,得到主控芯片与LPDDR4 的理想阻抗匹配方案,极大程度地减少了LPDDR4 的信号反射问题,在此基础上,对影响LPDDR4 信号完整性的关键性因素如传输线信号带宽、耦合线宽、耦合间距等进行定量仿真分析,使得部分传统的PCB 经验布线规则在LPDDR4设计上有了明确的分析量化,如3W 布线定则,设计者可以明确通过评估1W、2W、3W、4W、5W 的串扰值来确定走线间距,一定程度上为LPDDR4 的应用设计提供了参考依据。文章的研究思路也能为其他类型的DDR 及高速信号设计提供参考。由于时间关系加上水平有限,文章还有许多没有分析考虑的因素,比如过孔处的阻抗突变[13],信号的码间干扰以及电源完整性问题等,仍有进一步的优化改进空间。