基于FPGA的8K分屏器设计

付玉红

摘 要:设计了一款8k分屏器,主控采用FPGA芯片,支持一路HDMI2.1、8k、60 Hz信号输入;支持4路HDMI2.0、4k、60 Hz信号输出;分屏器支持将输入的8k信号进行“田”字型切片处理,输出4路4k信号,这4路4K信号的画面拼接起来就是1幅完整的8k画面。

关键词:8K分屏器;1进4出;HDMI2.1;FPGA

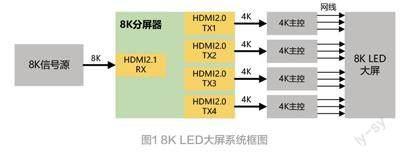

目前主流的LED 主控最大只能支持4k、60 Hz 信号输入,但是目前8k LED 大屏技术已经成熟,且已经慢慢进入商用。如图1 所示,8k LED 大屏的主控一般由4 台4k 主控拼接而成,但是前端8K 信号源目前已普遍采用HDMI2.1 接口单线传输8K 信号,为了满足8kLED 大屏显示系统需要,8K 分屏器应运而生。8k 分屏器可以将8k 信号按“田”字型分割成4 路4k 信号输出,正好可以分别对接4 台4k 主控,从而实现8k LED 大屏显示。此分屏器可广泛应用于各种8k 大屏显示系统。

本文设计的8k 分屏器采用FPGA 纯硬件逻辑实现,用户操作十分简单,接上电源和5 根HDMI 线之后上电即可使用,无需遥控或按键操作。

1 硬件设计

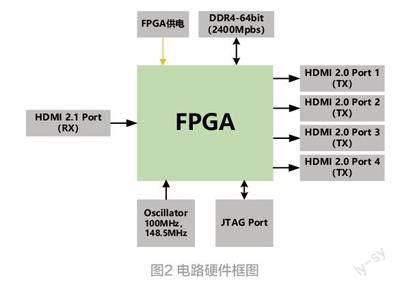

8k 分屏器主芯片为FPGA 芯片,芯片自带速率高达12.5 Gbit/s 的通用高速收发器,拥有DDR4 PHY 和DDR4 硬核控制器,DDR4 最大传输速率2 400 Mbit/s。

硬件层面,如图2 所示,HDMI2.1 输入接口的高速信号接到FPGA 高速收发器的接收通道,4 路HDMI2.0 输出接口的高速信号接到FPGA 高速收发器的发送通道,HDMI2.1 TX 和HDMI2.0 RX 的接口協议由FPGA 内部可编程逻辑实现。电路板上有64 bit DDR4 芯片(速率2 400 Mbit/s),用于缓存和切割接收的8K 视频信号。

板上还提供用于HDMI接口IP 的100 MHz和148.5 MHz固定晶振,以及一个JTAG 接口用于FPGA 配置文件下载和调试。

2 FPGA逻辑设计

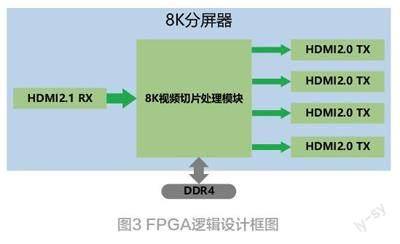

FPGA 设计框图如图3 所示,HDMI2.1、8k 视频信号进入FPGA 芯片之后,首先经过高速收发器的接收通道将高速串行信号转换成低速并行信号,然后经过HDMI2.1 RX IP 处理后输出接收的视频信号,视频信号随后进入8k 视频切片处理模块,经过此模块处理后输出4 路4k 信号,输出的4 路4k 信号分别进入4 个HDMI2.0 TX IP,TX IP 将数据按HDMI2.0 标准打包后输出到高速收发器的发送通道,此发送通道将低速并行信号转换成高速串行信号输出,输出的信号直接接到HDMI2.0 输出接口。

3 结束语

本文本文设计了一款8k 分屏器,支持一路HDMI2.1、8k、60 Hz 信号输入,四路HDMI2.0、 4k、60 Hz信号输出,此分屏器使用简单,工作稳定,可用于各种8k 大屏显示系统。