基于Quartus II与Modelsim的加减复用电路实验教学设计

陈艳 刘俊文 古国龙 黄文基 杨飒

摘 要:加减计算电路是数字计算系统的核心计算单元,也是相关专业本科生需要重点掌握的专业知识。文章通过加减计算为教学案例设计一种支持原码输入、输出的加减计算电路系统,用于支持带符号n bits位宽数据的加减运算。为了优化计算电路的硬件开销,该计算电路内核采用补码技术,将加法操作与减法操作融合在一个计算电路模块中,实现系统的加减复用计算。实验教学采用“理论指导+案例仿真操作”方式,使学生成为理论指导实践的受益人。通过该教学案例,学生不仅能够掌握数字电路系统设计的一般方法,还能通过理论结合实践的模式启迪创新设计思维,提升复杂数字电路系统设计能力,为其进一步成长为学习型人才打下良好的专业基础和实践基础。

关键词:教学研究和改革;案例教学;实验设计;数字电路;加减计算电路

中图分类号:TP331;G642 文献标识码:A 文章编号:2096-4706(2023)13-0181-08

Add–subtract Multiplexing Circuit Experimental Teaching Design Based on Quartus II and Modelsim

CHEN Yan, LIU Junwen, GU Guolong, HUANG Wenji, YANG Sa

(School of Physics and Information Engineering, Guangdong University of Education, Guangzhou 510303, China)

Abstract: The add-subtract computing circuit is the core computing unit of digital computing systems, and it is also a key professional knowledge that relevant undergraduate students need to master. This paper designs an add-subtract calculation circuit system that supports input and output of the original code for teaching cases through addition and subtraction calculation, which is used to support addition and subtraction operations with symbol n bits bit width data. In order to optimize the hardware overhead of the computing circuit, the core of the computing circuit adopts complement technology, which integrates addition and subtraction operations into a computing circuit module to achieve the addition and subtraction multiplexing calculation of the system. The experimental teaching adopts the method of “theoretical guidance+case simulation operation”, making students the beneficiaries of theoretical guidance in practice. Through this teaching case, students can not only master the general method of digital circuit system design, but also inspire innovative design thinking through the mode of combining theory with practice, improve the design ability of complex digital circuit systems, and lay a good professional and practical foundation for their further growth as learning talents.

Keywords: teaching research and reform; case teaching; experimental design; digital circuit; add–subtract calculation circuit

0 引 言

為了适应新一轮科技变革和产业革命,教育部等部门发布了加快建设发展新工科的多个文件[1,2],将工科专业的研究与实践需求推向更重要的教学地位。在教学工作中,如何发挥学生主观能动性,提升其工程实践与创新能力等越来越受到教育工作者的广泛关注[3-5]。传统教学以老师的“讲”为主,学生的工程实践能力和创新能力无法得到有效的培养[6-8],显然,传统教学中的这种模式并不利于新工科人才培养目标的实现。换句话说,这种模式不利于学生将理论知识与工程实践相结合,从而无法有效地培养学生的工程实践能力。与传统授课模式不同的是,“理论指导+案例仿真操作”模式实现了“讲解”与“实践”的有效结合,有助于提升学生的理论指导实践能力[9-11]。本文以加减计算复用电路系统设计为例,通过“理论指导+案例仿真操作”模式激发学生数字电路方面的实践能力和创新能力。

加减计算电路是处理器单元的核心部分[12-14],用于支持处理器不同类型的计算任务,加减计算相关知识也是本科阶段需要重点掌握的课程内容。授课活动通常按分离模式进行加减电路的设计。在该模式下,加法与减法操作通常被设计为不同的电路模块,从而导致数字电路系统硬件成本增加,降低电路系统在工程应用中的实用性。此外,该模式下,加减计算电路仅支持二进制补码数据,学生需要预先对原码数据进行补码转换,这就增加了学生实践过程中的理解难度。可见,这种非直观、抽象的分离式工程实践难以激发学生的工程应用兴趣,无法有效提升学生的工程实践能力与创新能力。

本案例以原码输入、原码输出的形式进行数字电路系统的设计,并将加法操作和减法操作融合在一个计算电路模块中,实现了系统的加减复用计算,优化了计算电路的硬件开销,提升了学生的工程实践能力。本文以带符号4 bits位宽数据的加减运算电路为例进行设计。为验证加减计算系统的计算功能,使用QuartusⅡ[15]与Modelsim[16]软件进行联合仿真。采用“理论指导+案例仿真操作”方式,首先给出带符号二进制原码运算的加减计算原理;其次基于计算原理进行复用电路设计;再次给出Quartus Ⅱ中计算系统的电路原理图;最后给出该原理图在Modelsim中的波形仿真结果。仿真结果表明,本案例具有正确的输入输出波形,案例设计得合理有效。通过该教学案例,学生能够以理论结合实践的模式不断启迪创新思维,提升复杂数字电路系统的设计能力,为其进一步成长为学习型人才打下良好的专业基础和实践基础。

1 带符号运算的加减计算原理

本节介绍带符号数的加法、减法计算特征。首先介绍带符号数的表示方法,其次介绍带符号数原码、补码的转换关系,最后介绍带符号数的加法、减法计算原理。

1.1 带符号二进制数的表示方法

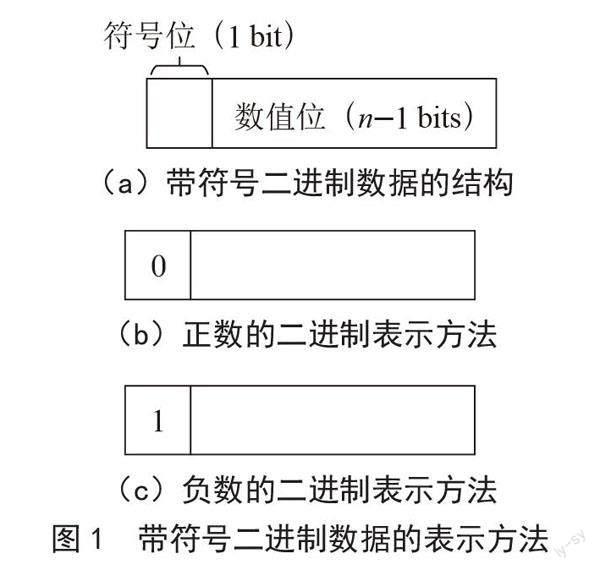

带符号数运算是科学计算的主要形式。数字电路系统通过带符号二进制数处理科学计算任务。如图1(a)所示,带符号二进制数由符号位和数值位两部分组成。最高位为符号位,符号位的值为0表示该二进制数为正数,如图1(b)所示;符号位的值为1表示该二进制数为负数,如图1(c)所示。本文4位加减计算系统用于支持输入数据位宽为4 bits的计算,最高位表示符号位,低3位表示数值位。例如,二进制数据“0111”表示数据7,“1111”表示数据?7。本案例的设计思路适用于任何位宽数据的计算。

对于n bits带符号二进制数据,所能表示数的范围为[-2n-1,2n-1-1]。本案例中4位带符号二进制数据能够表示的范围为[-8,7],其十进制数、原码、反码和补码之间的关系如表1所示。

1.2 带符号二进制数原码与补码转换关系

在数字电路系统实验中,为了便于计算,带符号二进制的加减计算通常利用补码直接计算。实验者需要在计算之前将二进制原码数据转换为补码,并在计算之后将补码计算结果转换为原码。原码、反码与补码之间的转换如图2所示。当二进制数为正数时,其原码也为该数的反码和补码,如图2(a)所示。例如,十进制数1的二进制原码、反码和补码均为0001。当二进制数为负数时,其原码(补码)除符号位之外,其他位按位取反(反码),然后加1得到该数的补码(原码),如图2(b)所示。例如,十进制数-7的二进制原码为1111,对该原码进行按位取反(符号位除外)得到1000(反码),再加1得到1001,即-7的补码为1001。同样,已知-7的补码为1001,对该补码进行按位取反(符号位除外)得到1110,再加1得到1111,即-7的原码为1111。表1给出了4位带符号二进制数的原码、反码与补码间的对应关系。

通常,学生能够直观地表示出二进制原码数据,但是对于二进制补码数据并不敏感,因此,本文将基于输入输出为原码的形式进行计算电路的设计。该实验设计旨在提高学生数字电路系统加减计算理论及其工程应用能力。

1.3 带符号二进制数的加减计算

对于二输入加减计算(两个操作数A、B,其中A、B取值可能为正数或负数),共有8种计算情况,分别为正数+正数、正数-负数、正数-正数、正数+负数、负数+正数、负数?负数、负数+负数、负数-正数。很明显,这8种情况可以等效为3类计算,分别是正数+正数(该计算体现正数+正数和正数?负数的计算)、正数+负数(该计算体现正数-正数、正数+负数、负数+正数和负数-负数的计算)以及负数+负数(该计算体现负数+负数和负数-正数的计算)。从上述分类可以看出,A与B相加与相减操作等效的三类计算均为加法操作,因此,在设计加减计算电路时可以基于该思想节约硬件开销。

本案例设计以操作数位宽4 bits为例进行说明,根据二进制数的计算理论,当输入数据的位宽为4 bits时,为了防止数据溢出,两个4 bits操作数的运算结果需要5 bits位宽才能正确表示。下面将基于4 bits操作数介绍正数+正数、正数+负数和负数+负数这三类计算,其他计算均可等效为这三类计算。

如图3所示为正数+正数的操作图,其中操作数A和B均为正数,分别为3和6。图3(a)给出了操作数A、B的原码、补码以及位扩展后的补码。位扩展是指对最高位(符号)进行扩展,如0011的最高位为0,位扩展后为00011,可见对于正数而言,位的扩展不会改变数值的大小。图3(b)为操作数A、B的补码相加过程,该加法中的操作数均为位扩展后的补码形式,其结果(01001)也是补码形式。01001的最高位为0,表示十进制数据9,该二进制结果符合3 + 6 = 9的计算结果。

如图4所示为正数+负数的操作图,其中操作数A = 3、B = ?6。图4(a)给出了操作数A、B的原码、补码以及位扩展后的补码。负数的位扩展是指对最高位(符号)进行扩展,如B的补码1010位扩展之后为11010,可見对于负数而言,位的扩展同样不会改变数值的大小。图4(b)为操作数A、B位扩展后补码的相加过程,相加的结果(11101)也是补码形式。按照图2(b)中补码与原码之间的转换关系可得补码11101,表示十进制数?3,该结果符合3 + (-6) = -3的计算结果。从图4中可以看出,A与B相减等效于A的补码与(?B)的补码相加。因此,在进行减法操作时可将该数取负后再进行补码相加的操作,将减法操作转换为加法操作,省去减法专用电路结构,节约计算电路的硬件开销。

如图5所示为负数+负数的操作图,其中操作数A = -3、B = -6。图5(a)给出了操作数A、B的原码、补码以及位扩展后的补码。A的位扩展补码为11101,B的位扩展补码为11010。图5(b)为操作数A、B位扩展补码的相加过程,相加的结果(10111)也是补码形式。按照图2(b)中补码与原码之间的转换关系可得补码10111,表示十进制数-9,该结果符合(-3) + (-6) = -9的计算结果。

图3、图4、图5计算涵盖了两个操作数的8类加减计算,其他计算均可等效为这三类计算。从图3、图4、图5所展示的补码计算操作过程可知,所有类型操作均为补码的加法操作,也就是说所有的加法操作和减法操作都可以通过加法电路实现,而无需设计复杂的减法专用电路。此外,从图3至图5可以看出,无论操作数是正数还是负数,均可由补码输入计算得到正确的补码输出。因此,本案例将正负数的计算统一为基于补码的加法计算形式,并在补码计算内核的基础上设计原码与补码转换的电路模块,实现计算电路的原码输入、原码输出,提高案例的可实践性。

2 加减复用计算电路原理图设计

本小节基于上述两个操作数的运算进行数字电路系统的设计,用于支持原码输入、原码输出的计算特征。首先介绍基于原码计算的系统框图,然后介绍系统框图中的原码、补码转换系统和加减计算复用系统,分别如图6、图7所示。

2.1 加减计算复用系统框图

如图6所示为加减计算系统框图,用于支持基于原码输入、原码输出的加减计算任务。通过上述分析可知,无论数据类型为正数还是负数,补码运算的内核可使计算形式统一为加法操作。为便于学生理解二进制数据加减操作过程,本文设计了支持原码输入、原码输出的计算电路系统,直观地展示二进制加减操作。如图6所示,该系统的输入输出均为二进制原码,计算系统包含原码、补码转换电路(为计算内核提供补码输入数据和原码输出数据)和补码计算内核电路(加减计算操作)。系统输入为A、B(均为n bits原码),系统输出为O(n+1 bits原码),图中的[]符号表示位拼接,例如O = [S [n] O1]表示S [n]与O1(n bits)的拼接形成n+1 bits位宽数据赋值给O。

2.2 原码、补码转换电路

图7(a)为原码、补码互换电路系统。图7(a)上图为系统框图,系统输入数据A的位宽为n bits,输出数据S的位宽为n-1 bits。输出数据位宽比输入数据位宽少1的原因是原码和补码的符号位一样,因此,本案例原码、补码转换系统的输出仅为除符号位的数据。

图7(a)下图为图7(a)系统图的电路细节图,实现原码与补码间的互换。该电路图的输入、输出分别为A、S。电路内核单元是由异或门和半加器组成的链式电路。其中,半加器的两个输入端均为1 bit输入数据(用符号A、B表示);半加器的两个输出端均为1 bit输入数据(用符号S、C表示),S、C分别为A + B的和值、进位值。例如A = 1、B = 1时,按照二进制加法可得S = 0,C = 1。

对于n bits输入数据,由于不需要处理符号位的数据,系统仅需n-1个异或门与半加器的组合即可实现原码与补码间的转换。其中,异或门的输出端为XOR (A[i],A[n-1]),XOR表示异或操作。当电路系统的输入为正数时,符号位A[n-1] = 0,则XOR (A[i],A[n-1]) = A[i];当电路系统的输入为负数时,符号位A[n-1] = 1,则XOR (A[i],A[n-1]) = NOT(A[i]),NOT表示取非操作。从上述分析可知,电路系统中的n-1个异或门可实现除符号位之外原码的反码操作。当原码为正数时,XOR操作后保持原码数据(正数的原码等于其反码);当原码为负数时,XOR操作后得到反码,从而实现原码与补码间转换的第一步。

基于XOR门反码输出结果,n-1个半加器的链式结构用于支持从反码到补码的操作,从而实现原码与补码间的转换。当电路系统的输入为正数(A[n-1] = 0)时,根据电路系统中链式半加器结构可知,S [0] = A [0]、S [1] = A [1]、…、S [n-2] = A [n-2],该转换系统的输出与输入(除去符号位)一致,满足正数原码等于补码的计算特征;当电路系统的输入为负数(A [n-1] = 1)时,根据电路系统中链式半加器结构可知,该电路计算操作数A除符号位外取反再加1的操作,满足负数原码与补码间转换的计算特征。综上所述,该转换电路系统能够支持原码与补码间的互换计算。

图7(b)给出输入数据位宽为4 bits(输入数据为A)的电路系统结构案例。由于符号位不需要进行转换,电路系统仅需3组异或门与半加器的链式组合。A[0]~A[2]依次作为3组异或门的输入数据;A[3]为A的符号位数值,该值为3组异或门的控制输入数据,实现二进制原码与反码间的转换操作(正数反码=原码;负数反码=NOT(原码))。半加器链式结构进行加法操作,实现反码(异或门输出结果)转换为补码的操作。例如,当A为负数时,A[3] = 1,最低位的半加器进行反码加1操作,并通过该半加器链式结构进行逐位相加,即可得到负数除去符号位的补码数据;当A为正数时,A[3] = 0,半加器链式电路输出为反码(正数的原码=反码=补码),即可得到正数除去符号位的补码数据。

2.3 加減计算复用数字电路系统

如图8所示为加减计算复用数字电路系统,用于支持补码输入、补码输出的加减计算任务。图8(a)为系统框图,包含3个输入端(A、B和ASC)和1个输出端(S)。其中,A、B为数据输入端口,位宽均为n bits;ASC为加减控制输入端口,位宽为1 bit。当ASC = 0时,系统执行加法操作;当ASC = 1时,系统执行减法操作。S为数据输出端口,位宽为n+1 bits。

图8(b)为图8(a)系统框图的电路细节图。该电路图的三个输入端分别为A、B和ASC,1个输出端为S。电路系统的内核单元为异或门和全加器组成的链式电路。其中,全加器的3个输入端均为1 bit输入数据(用符号A、B和Cin表示);两个输出端均为1 bit输入数据(用符号S、C表示),S、C分别为A + B + Cin的和值、进位值。例如A = 1、B = 0、Cin = 1时,按照二进制加法可得S = 0,C = 1。

通過图3、图4、图5分析可知,位扩展的加减计算是避免数据溢出并得到正确计算结果的有效方法。本设计采用位扩展策略,对于n bits输入数据,构建n+1组由异或门与全加器构成的链式结构,如图8(b)所示。从左往右,A、B从最低位值到最高位值(符号位的值)依次付给前n组异或门和全加器。最后为了计算正确,将A、B符号位的值再次送入最右侧的异或门和全加器,实现位扩展计算。

在该设计中,异或门的输入分别为B[i]和ASC。根据异或门的计算特征(XOR(B[i],ASC))可知,当ASC = 0时异或门输出B[i],电路系统实现A + = 的操作。例如,对于图8(b)最左侧的异或门和全加器组合,由于异或门输出为B[0],全加器三个输入端的数据分别为A[0]、B[0]以及ASC(此时ASC = 0),则全加器的计算模式为A[0] + B[0] + ASC = A[0] + B[0]。根据链式结构的数据传递特征可知,图8(b)电路在ASC = 0时实现A + B的操作,从而实现加法操作。

当ASC = 1时,图8(b)实现A - B的操作,从而实现减法操作。根据图8(b)可知,ASC = 1条件下,异或门输出NOT(B[i]),即最高的两位异或门是将B的符号位取反,其他异或门对B的数值位取反。由于最低位全加器的进位输入端为加减控制信号,即Cin = ASC = 1,全加器实现B的反码加1操作,求得B负数的补码,即(-B)的补码。根据图4的分析可知,减去一个数等效于与这个数负数的补码相加,因此,图8(b)电路实现A - B的操作。

为了更加直观地展现图8电路支持减法(ASC = 1)操作,我们以图4的3-6计算为例进行分析。设A = 3、B = 6,此时A、B均为正数,通过图7转换可得A = 0011、B = 0110。图8输入数据位宽为4 bits,需要5组由异或门与全加器构成的链式结构。图8的输入数据为A[0] = 1、A[1] = 1、A[2] = 0、A[3] = 0、B[0]=0、B[1] = 1、B[2] = 1、B[3] = 0、ASC = 1,则5个异或门对B取反可得11001,此时全加器A、B、Cin端口的输入分别为00011、11001、1,全加器执行三者的相加操作,即00011+11001+1 = 00011+(11001+1) = 00011+11010 = 11101(11101为-3的补码),其中00011为3的补码,11010为-6的补码,从而实现3-6 = -3的操作。

综上所述,图8电路设计能够同时支持补码输入、补码输出的加减计算任务,实现加减复用计算的功能。本案例给出了详细的理论知识和电路设计思路,学生可以基于教学案例的设计思想进行自主设计,进一步提升数字电路系统的创新能力。

3 实验仿真

本节将以两个4 bits位宽数据执行加减操作为例进行仿真设计,验证图6原码输入、原码输出的加减系统的计算功能。

3.1 仿真设置

本实验所用软件平台为Quartus Ⅱ 12.0和Modelsim SE-64 10.0d,其中Quartus Ⅱ用于设计、验证和综合加减计算电路,Modelsim用于提供仿真波形。Quartus Ⅱ和Modelsim联合仿真配置方式参见文献[17]。

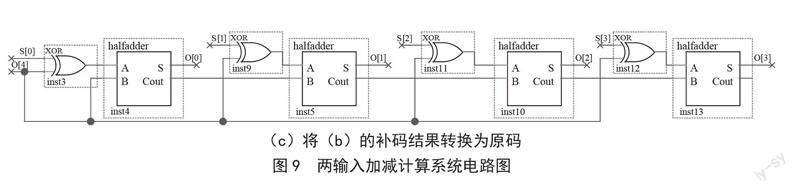

3.2 两输入加减计算系统电路

如图9所示为两输入加减计算电路图,该图包含3个部分,分别为原码转补码电路、补码加减计算电路和补码转原码电路。图9中的数据流动方向与图6一致。图9(a)为原码转补码电路,该电路对应于图6左侧的原码补码转换系统,实现将输入的原码数据转换为补码,为下一级模块提供补码输入数据。该计算系统的输入数据为A(4 bits)、B(4 bits)、ASC(1 bit),图9(a)将A、B进行原码转补码的操作,操作数A、B的补码分别用符号C、D表示。图9(b)为补码加减计算电路,该电路对应图6的加减计算复用系统,实现基于补码的加减运算,为下一级提供补码形式的加减计算值。该模块电路的输入为加减计算控制位(ASC)和符号位扩展的C、D,输出为S和O的符号位。9(c)为补码转原码电路,该电路对应图6右侧的原码补码转换系统,该模块的输入数据为S,输出数据为O的值位,实现补码转换为原码,完成从原码输入到原码输出的加减计算。

3.3 仿真波形分析

该加减操作计算电路支持所有操作数为正数或负数的情况,为了验证该计算电路的运算正确性,仿真结果将展示操作数A、B取正数或负数的运算波形,如图10、图11所示,仿真时间周期为500 ns。

图10枚举了操作数A为正数、操作数B正负切换的加减计算情形。图中A、B、ASC为计算电路的输入数据,A和B均为4 bits位宽数据(原码,最高位为符号位),ASC为加减控制位(1 bit),O为输出数据(原码,最高位为符号位)。对于操作数A为正数的情形可实现A+B(正数)、A+B(负数)、A-B(正数)以及A-B(负数)四种情形。例如,在1~1.5 μs,A = 0000(十进制数0),B = 0111(十进制数7),ASC = 1(减法操作),仿真结果O(10111符号位扩展结果)与A-B = -7的原码结果一致。通过简单计算可知,其他时刻的仿真结果与理论运算也一致,这表明该电路能够支持上述四类计算的原码运算模式。

图11枚举了操作数A为负数、操作数B正负切换的加减计算情形。图中A、B、ASC与图10一致。对于操作数A为负数的情形可实现A+B(正数)、A+B(负数)、A - B(正数)以及A - B(负数)四种情形。例如,在16.5~17 ns,A = 1000(十进制数-8),B = 0111(十进制数7),ASC = 0(加法操作),仿真结果O(10001,符号位扩展结果)与A+B = -1的原码结果一致。通过简单计算可知,其他时刻的仿真结果与理论运算也一致。

图10、图11的仿真结果表明,该电路系统能够支持各类型原码输入、原码输出的加减计算模式,验证了图9数字电路系统的计算功能,表明该电路系统的设计合理性和计算正确性。图9、图10、图11的详细电路设计图和波形分析结果可以辅助学生基于本案例的验证过程进行工程设计,进一步提升数字电路系统在QuartusⅡ和Modelsim中的实践能力。

4 结 论

本文以原码输入、原码输出加减计算复用电路设计为例进行教学案例设计,旨在利用数字电路知识构建特定需求的数字电路系统。首先,介绍带符号运算的加减计算原理;其次,基于计算原理构建加减可复用计算的电路原理图,实现原码数据输入、原码数据输出的计算;最后,对原理图进行实验验证,仿真结果直观地展示了8类运算结果,验证了加减复用计算电路系统的计算功能。一方面,本教学案例提供一种直观的原码输入、原码输出运算电路,便于学生有效处理带符号二进制运算;另一方面,本案例给出详细的理论知识和电路设计图,学生可以基于教学案例的设计思想进行自主设计,有效提升其数字电路系统的实践能力和创新能力,为其进一步成长为学习型人才打下良好的专业基础和实践基础。

参考文献:

[1] 教育部,人力资源社会保障部,工业和信息化部.制造业人才发展规划指南[EB/OL].[2023-01-04].https://www.gov.cn/xinwen/2017-02/14/content_5167903.htm.

[2] 复旦大学教务处.“新工科”建设复旦共识 [EB/OL].[2023-01-08].https://jwc.fudan.edu.cn/2b/1b/c25319a273179/page.htm.

[3] 杨飒,邢凤闯.基于高频谐振功率放大电路分析的仿真教学研究 [J].广东第二师范学院学报,2020,40(5):98-105.

[4] 宋耘.哈佛商学院“案例教学”的教学设计与组织实施 [J].高教探索,2018,183(7):43-47.

[5] 胡志超,王云超,冯薇,等.“以学生为中心”的工科混合式教学课程设计探索与实践 [J].高教学刊,2023,9(2):158-161+165.

[6] 孙觊琳,成守宇,薛若军,等.开放式实验在“核工程虚拟仿真实验”课程教学中的应用初探 [J].现代信息科技,2022,6(18):192-194+198.

[7] 朱宝忠,孙运兰,陈海飞,等.基于新工科背景的“学科竞赛”&“科研训练”双驱模式下学生工程实践能力和创新创业能力的培养 [J].创新创业理论研究与实践,2022,5(23):76-78.

[8] 艾伟,郭亮,李梅,等.基于创新能力培养的电子类工程实践教学模式探索 [J].创新创业理论研究与实践,2022,5(22):118-120.

[9] 冯李航,吴力帆,宋辉,等.虚拟工厂规划仿真系统设计及其教学案例分析 [J].实验技术与管理,2023,40(1):160-168.

[10] 阎昌国,李伟,李青,等. Boost变换器电路的“再生”教学与实验仿真 [J].实验技术与管理,2021,38(7):161-165.

[11] 张蓓,张粹玲,王新泽,等.“传感器及调理电路的设计与仿真”课程的项目实践理念探索 [J].实验技术与管理,2021,38(3):225-229+282.

[12] 李泉龙.基于Kogge-Stone算法与多米诺逻辑的64位高性能加法电路设计 [D].成都:西南交通大学,2016.

[13] 周游,李杰,贺光辉.面向高精度随机计算单元的加法运算电路与MAX运算电路设计 [J].微电子学与计算机,2021,38(7):1-6.

[14] 李鹏.减法电路在运放恒流源电路中的应用 [J].电子世界,2019,580(22):163-164.

[15] LIU B. Research and Design of a simple CPU with QuartusⅡ [J] .IOP Conference Series:Earth and Environmental Science,2019,252(3):032180.

[16] ALBATOOSH A H,SHUJA'A M I,AL-NEDAWE B M. A VHDL Code for Offset Pulse Position Modulation Working with Reed Solomon System by Using ModelSim [EB/OL].[2023-01-19].https://www.journal.mtu.edu.iq/index.php/MTU/article/view/758.

[17] 陳艳,杨飒.算术逻辑单元在Quartus Ⅱ与ModelSim中的教学实例设计 [J].现代信息科技,2021,5(18):111-115.

作者简介:陈艳(1991.02—),女,汉族,湖南常德人,讲师,博士,研究方向:FPGA高性能计算;通讯作者:杨飒(1970.10—),女,汉族,湖南湘潭人,副教授,硕士,研究方向:信息处理与电路设计。

收稿日期:2023-02-24

基金项目:广东省普通高校重点领域专项(2020ZDZX2059);广东省高等学校教学质量与教学改革工程项目(202005048);广州市科技计划一般项目(202201011386);广东第二师范学院创新创业训练计划项目(202214278076)